|

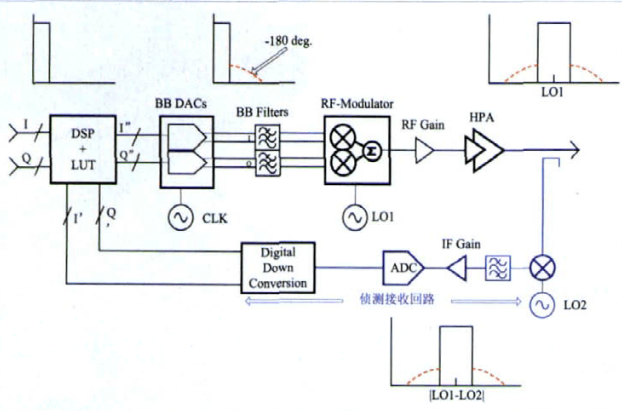

随着全球3G网络的大规模建设,运营商越来越注重降低CAPEX(建设成本)和OPEX(维护成本),功放作为基站当中最昂贵的器件之一,其对效率的要求越来越高,从而使得数字预失真DPD(Digital Pre-DistorTIon)技术得到飞快的发展。图1是功放数字预失真处理的基本结构框图。和模拟预失真以及前馈架构相比,数字预失真在提高效率、多载波应用、修正效果以及自适应方面具有很大的优势。同时随着零中频架构开始在3G基站中得到应用,数字预失真在修正零中频架构中的本振泄漏和镜像抑制方面, 具有非常好的效果。 但是要实现这些优势和取得良好的预失真效果,一个高性能的侦测接收通道是必须的,本文旨在对侦测接收回路的设计做一些具体讨论。

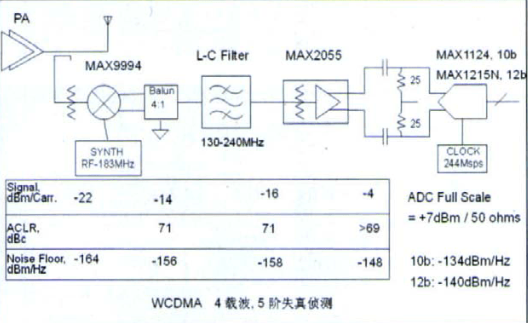

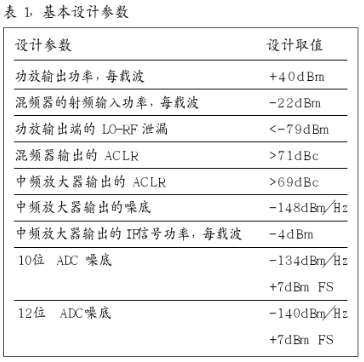

图2是Maxim提供的一个紧凑而低成本的侦测接收通道设计方案。此方案采用高线性混频器MAX9994将RF信号下变频到IF信号, 然后经过IF滤波器滤波, IF滤波采用50Ω的单端设计以降低滤波器对PCB板寄生分量的敏感度。滤波器输出的IF信号经可变增益中频放大器MAX2055调整增益, 然后以极佳的线性度驱动ADC的输入。此方案的设计讨论是基于W CDMA、4载波、40W功放、每载波10W、5阶失真侦测。表1是相关的基本设计参数。对于更少的载波和更低阶的失真监测也可以采用同样的架构, 主要是测量带宽的要求有所不同。对于不同功率的功放, 主要差异表现在LO-RF泄漏。 射频信号耦合 从功放射频输出耦合过来的信号功率必须要降低到适合混频器输入级要求的功率水平, 这可以采用定向耦合加固定衰减的方式。如果需要的话, 加入射频可变衰减器以补偿链路增益变化。加到此处混频器合适的射频输入功率为-22dBm, 所以对于每载波10W, 40dBm的功放输出功率, 这里需要62dB的衰减量。 混频器MAX9994的本振到射频的泄漏典型值为-17dBm,此泄漏同样会被射频衰减器和耦合器再衰减, 所以经过62dB的衰减后, 功放输出端的LO-RF 泄漏小于-79dBm。UMTS要求在大于60MHz的偏移范围内杂散辐射低于-73dBc, 图2的解决方案可以不需要任何射频带通滤波器就可以有很宽的余量满足这个指标。如果需要更宽的余量, 可以采用一个简单的陶瓷射频滤波器以进一步降低本振泄漏分量。 ADC及中频频率的选择

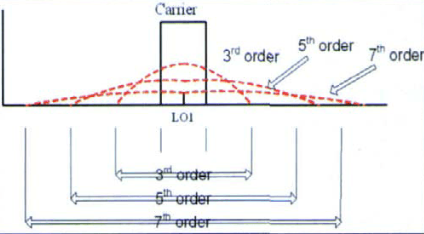

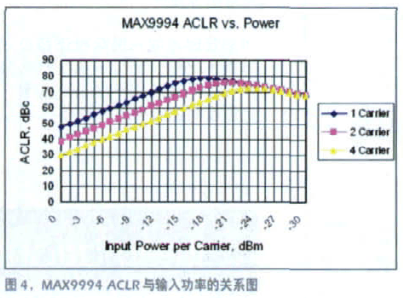

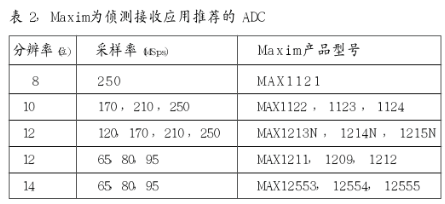

对于4载波WCDMA, 5阶失真校正, 结合下面的图3, 我们可以计算出载波带宽和谐波修正带宽如下: 载波带宽BW = 45MHz = 20MHz 五阶谐波修正带宽BW = 520MHz = 100MHz 由此可以推荐使用如下系列的ADC: 10位, 170MSps~250MSps ADC -MAX1122-1124 12位,170MSps~250MSps ADC -MAX1213-1215 下变频IF频率的选择是一个折中和平衡的过程, 较低的中频频率可以最小化离散L-C中频滤波器寄生分量的影响;如果用到射频滤波器, 较高的中频频率可以降低对RF滤波器选择性的要求。上面推荐的ADC在任何小于250MHz的中频频率下都可以很好的工作。 4载波WCDMA功放数字预失真的操作, 对于170MSps~244MSps的采样频率, 我们假定ADC工作在第一或者第二奈奎斯特域, 建议中频的中心频率在61MHz或者183MHz。对于更加受限的带宽和采样率, 也可以尝试采用65MSps ~95MSps ADC, 工作在第四或者第五奈奎斯特域。 针对数字预失真处理当中的侦测接收回路设计,Maxim提供了几个管脚兼容的ADC系列。其中一个系列可以提供8位,10位和12位的分辨率,120MSps,170MSps,210MSps和 250MSps的采样率, 见表2。所有这些ADC都针对高至250MHz的输入频率做了性能优化设计,在这样高的输入频率下,它们保持着极高的噪底、SFDR和IMD性能。这对侦测接收应用是最佳选择,因为侦测接收需要在非常宽的输入带宽内提供高精度的数字化处理。 Maxim也提供12位和14位,采样率65MSps,80MSps和 95MSps的针对两载波应用的ADC,两载波应用中失真的侦测需要较少的带宽。表2列出了Maxim为侦测接收应用推荐的典型ADC型号。 混频 混频器MAX9994为多载波应用提供出色的线性度和噪声性能,同时提供更高的集成度,该器件包含双平衡无源混频器内核、IF放大器、双输入LO可选开关和LO缓冲器,它还集成了片上非平衡变压器,允许单端RF和LO输入。 -3dBm ~ +3dBm低LO驱动可以降低系统对本振源驱动能力的要求。MAX9994的中频输出是具有200Ω源阻抗的差分输出。 图4是MAX9994在1, 2和 4载波WCDMA应用中的邻道泄漏比ACLR性能曲线。结合紧随其后的中频放大器的ACLR,混频器71dBc的ACLR预算会给所要求的功放性能水平以足够的余量, 这确保了侦测接收通道的线性度,从而不会影响整个闭环回路的性能。对于4载波操作,根据图4中对应的4载波曲线, 71dBc的ACLR要求每个载波的输入功率水平在-22dBm,较少的载波或者较宽松ACLR要求的应用可以允许更高一些的功率水平。

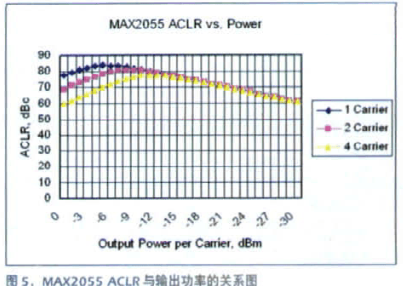

中频滤波与中频放大 MAX9994的输出通过一个4:1非平衡变压器耦合进一个单端 50Ω阻抗的中频滤波器。在这里, 客户可以选择低通或者是带通滤波器。Maxim设计和仿真了一个简单的4极高通和4极低通层叠的,中心频率在183MHz的滤波器,LC元器件取值在 9pF~23pF和 24nH ~ 100nH的范围,这些值和PCB板的寄生参数比较接近。滤波器阻抗比较低的话,可以降低对PCB板寄生电容所引起变化的敏感性,这里的PCB布线要尽量短。 混频器MAX9994的输出信号为达到ADC输入水平的要求而需要放大,中频可变增益放大器MAX2055可以在保持良好线性的情况下提供这种增益。图4演示了在1,2和4 载波WCDMA应用当中,输出功率与MAX2055的ACLR指标之间的关系。 结合前面混频器的ACLR,71dBc的ACLR目标最终合成一个69dBc的中频放大器ACLR指标, 对于4载波操作,根据图5中对应的4载波曲线, 69dBc ACLR要求每个载波的输出功率-4dBm。对于更少的载波数量,可以获得更高的ACLR。 如图2中所示, 经过MAX9994和中频滤波器以后的信号水平大概在-16dBm每载波。因为MAX2055的增益可以在-5dB~+20dB的范围内以1dB间隔进行设置,所以用户可以选择合适的增益设置, 以驱动ADC到-4dBm每载波。同时MAX2055允许用户补偿链路当中耦合器和RF衰减器产生的增益变化。 ADC输入输出结构 MAX2055的输出经电容耦合进终结ADC输入的50Ω差分阻性负载。低的源阻抗可以最小化ADC输入阻抗的影响。 ADC MAX1124和MAX1215N的满量程输入幅度是1.4Vp-p。假定WCDMA波形的峰均比是10dB,并且假设ADC至少有1dB的裕量在工作,这将使得ADC输入端的RMS信号幅度大概在200mV。对于50Ω的阻抗系统, 相当于每载波-4dBm的输入功率水平, 这与前面的中频放大器MAX2055 的输出驱动水平是一致的。

前面提到的ADC都是采用LVDS输出结构,这对支持高采样率是必须的,在侦测接收应用当中尤其重要,而且ADC的IMD性能要求非常的严格。老一点的接口技术,像CMOS,会引入较高的数字信号回流到ADC的地平面。对于10位和12位性能水平,这个回流会与ADC输入和输入滤波器件结合,给模拟输入信号引入误差。Maxim ADC所采用的低摆幅的差分LVDS输出结构可以去除这些潜在的失真源。侦测回路本身的任何失真,都将直接加入到功放的失真,所以必须最小化。 噪底 图2的方案框图中标识了通道中各级的噪底指标。可以看出, 噪底指标主要受控于所选ADC的SNR性能, 和10位ADC相比, 12位的AD转换器可以提供非常明显的更佳性能。3GPP UMTS的噪底规范是在50MHz偏移处-138dBc/Hz, 用户必须检查失真校正回路的噪声灵敏度以决定所需要的ADC噪底性能。 责任编辑:gt (责任编辑:admin) |