John Ardizzoni 和 Jonathan Pearson

引言

大多数现代高性能ADC使用差分输入抑制共模噪声和干扰。 由于采用了平衡的信号处理方式,这种方法能将动态范围提高2倍,进而改善系统总体性能。 虽然差分 输入型 ADC也能接受单端输入信号,但只有在输入差分信号时才能获得最佳ADC性能。 ADC驱动器专门设计用于提供这种差分信号的电路—可以完成许多重要的功能,包括 幅度调整、单端到差分转换、缓冲、共模偏置调整和滤波等。 自从推出 AD8138,1 以后,差分ADC驱动器已经成为数据采集系统中不可或缺的信号调理元件。

图1:差分放大器

图1是一种基本的完全差分电压反馈型ADC驱动器。 这个图与传统运放的反馈电路有两点区别:差分ADC驱动器有一个额外的输出端(V上)和一个额外的输入端(VOCM) 。 当驱动器 与差 分 输入型ADC连接时,这些输入输出端可以提供很大的灵活性。

与单 端 输出相反,差 分ADC驱动器产生平衡的差分输出信号—相对于VOCM—在V上与V上 之间。 这里的P指的是正,N指的是负。 VOCM输入信号控制输出共模电压。 只要输入与输出信号处于规定范围内,输 出共模电压必定等于VOCM输入端的电压。 负反馈和高开环增益致使放大器输入端的电压VA+和V一个- 实质上相等。

为了便于后面的讨论,需要明确一些定义。 如果输入信号是平衡信号,那么V知识产权和V在 相对于某个公共参考电压的幅度应该是相等的,相位则相反。 当输入信号是单端信号时,一个输入端是固定电压,另一 个输入端的电压相对这个输入端变化。 无论是哪种情况,输入信号都被定义为 在知识产权 –在在。

差模输入电压V在, dm和共模输入电压V在, cm的定义见公式1和公式2。

虽然这个共模电压的定义应用于平衡输入时很直观,但对单端输入同样有效。

输出也有差模和共模两种,其定义见公式3和公式4。

需要注意实际的输出共模电压V外, cm和VOCM输入端之间的差异,这个差异决定了输出共模电平。

对差分ADC驱动器的分析比对传统运放的分析要复杂得多。 为了简化代数表达式,暂且定义两个反馈系数β1和β2,见公式5和公式6。

|

|

(5, 6) |

在大多数ADC驱动应用中 β1= b2, 但含有 V知识产权在在在OCM, 1和2项的 在外, dm通用闭环公式对于了解β失配对性能的影响非常有用。在外, dm 的计算见公式7,其中包括了与频率相关的放大器有限开环电压增益A(s)。

当 b1≠ b2, 差分输出电压取决于VOCM—这不是理想的结果,因为 它产生了偏移,并且在差分输出中有过大的噪声。 电压反馈架构的增益带宽积是常数。 有趣的是,增益带宽积中的增益是两个反馈系数平均值的倒数。

当 b1= b2 ≡ | β, 公式7可以被简化为公式8。

这个表达式大家可能更加熟悉。 当 A(s) → ∞. 理想的闭环增益可以简化为RF/RG 增益带宽乘积公式看起来也很熟悉,其中的"噪声增 益 "与传统运放一样,等于1/β。

反馈系数匹配的差分ADC驱动器的理想闭环增益见公式9。

|

|

(9) |

输出平衡是差分ADC驱动器的一个重要性能指标,它分两个方面:幅度平衡和相位平衡。 幅度平衡用于衡量两个输出在幅度方面的接近 程度,对于理想放大器来说它们是完全一致的。 输出相位平衡用于衡量两个输出的相位差与180°的接近程度。 输出幅度或相位的任何 失衡都会在输出信号中产生有害的共模分量。 输出平衡误差(公式10)是差分输入信号产生的输出共模电压与相同输入信号产生的输 出差模电压的对数比值,单位是dB。

内部共模反馈环路迫使V哎呀��, cm等于输入端VOCM的电压,从而达到完美的输出平衡。

将输入端接到ADC驱动器

处理高速信号的系统经常会用到ADC驱动器。 分隔距离超 过信号波长一小段的器件之间必须用具有受控阻抗的电气传输线连接,以避免 破坏信号完整性。 当传输线的两端用其特征阻抗端接时可以取得最佳性能。 驱动器一般放在靠近ADC的地方,因此在它们之间不要求使 用受控阻抗连接。 但到ADC驱动器输入端的引入信号连接通常很长,必须采用正确电阻端接的受控阻抗连接。

不管是差分还是单端,ADC驱动器的输入阻抗必须大于或等于理想的终端电阻值,以便添加的终端电阻RT能与放大器输入端并联达到 要求的电阻值。 本文讨论的例子中的所有ADC驱动器都设计成具有平衡的反馈比,如图2所示。

图2:差分放大器的输入阻抗

因为两个放大器输入端之间的电压被负反馈驱动到零,因此两个输入端处于连接状态,差分输入阻抗R在就简单地等于2×RG。 为了匹配传输线阻抗 RL,需要将由公式11计算得到的电阻RT跨接在差分输入端。 图3给出了典型的电阻值,其中 RF= RG = 200 Ω, 理想的 RL, dm= 100 Ω,RT= 133 Ω.

|

|

(11) |

图3:匹 配100Ω传输线。

单端输入的端接更加麻烦。 图4描述了采用单端输入和差分输出的ADC驱动器工作原理。

图4:采用单端输入的ADC驱动器例子。

虽然输入是单端的,但 VIN, dm 等于 V在. 因为电阻RF和RG 是相等和平衡的,因此增益是1,而且差分输出 在上–在上, 等于输入,即 4 V p-p. 在出,厘米= VOCM = 2.5 V ,而且从下方的反馈电路可以看出,输入电压 VA+ 和 V一个– 等于 V上/2.

根据公式3和公式4, V上= VOCM+ V在/2, 即2.5V±1V的同相摆幅; V上= VOCM–在在/2, 即2.5V±1V的反相摆幅。 这样,VA+ 和 V一个– 的摆幅等于 1.25V±0.5V。 The 必须由 V在 提供的电流交流分量等于 (2 V – 0.5 V)/500 Ω = 3 mA, 因此到地的电阻必须匹配,从 V在, 看过去为 667 Ω.

当每个环路的反馈系数都匹配时,公式12 就是计算这个单端输入电阻的通式,其中R在, se是单端输入电阻。

|

|

(12) |

这是计算终结电阻的出发点。 然而值得注意的是,放大器增益公式基于零阻抗输入源的假设。 由于存在单端输入造成的不平衡而必须 加以匹配的重要源阻抗只会增加上面RG的阻值。 为了保持平衡,必须增加下面RG的阻值来实现匹配,但这会影响增益值。

虽然可以为解决端接单端信号问题而采用一个封闭形式的解决方案,但一般使用迭代的方法。 在下面的例子中这种需求将变得很明显。

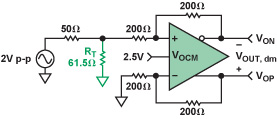

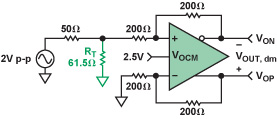

在图5中,为了保持低的噪声,要求单端到差分增益为1,输入终结电阻为50Ω,反馈和增益电阻值在200Ω 左右。

根据公式12可以算出单端输入电阻为267Ω。公式13表明,并联电阻RT应等于61.5Ω,才能将267Ω输入电阻减小至50 Ω.

图5:单端输入阻抗

图6是带源电阻和终端电阻的电路。 带50Ω源电阻的源开路电压为2Vp-p。 当源用50Ω端接时,输入电压减小到1V p-p,这个电压也是单位增益驱动器的差分输出电压。

图6:带源电阻和终端电阻的单端电路。

这个电路初看起来非常完整,但不匹配的61.5Ω电阻与50Ω的并联并增加到了上面的RG电阻,这就改变了增益和单端输入电阻,并且造成 反馈系数失配。 在低增益情况下,输入电阻的变化很小,暂时可以忽略,但反馈系数仍然必须匹配。 解决这个问题的最简单方法是增加下面 RG的阻值。 图7是一种Thévenin等效电路,其中上方的并联组合用作源电阻

图7:输入源的Thévenin等效电路

有了这种替代方案后,就可以将2 7. 6Ω的电阻RTS 增加到下面的环路中实现环路反馈系数的匹配,如图8所示。

图8:平衡的单端端接电路

注意,1.1V p -p的Thévenin电压要大于1V p-p的正确端接电压,而每个增益电阻增加了2 7. 6Ω,降低了闭环增益。 对于大电阻(>1kΩ) 和低 增 益(1或2)来说这些相反的效应基本抵消,但对于小电阻或较高增益来说并不能完全抵消。

图8所示电路现在分析起来就很容易了,其中的差分输出电压可以用公式14计算。

差分输出电压并不完全等于理想的1Vp-p,但可以通过修改反馈电阻实现最终独立的增益调整,如公式15所示.

图9是用标准1%精度电阻实现的完整电路。

图9:完整的单端端接电路。

观察: 参考图9,驱动器的单端输入电阻RJ 米, s e由于RF和RG的改变而变化。 驱动器上端环路的增益电阻是200Ω ,下端环路的电阻是 200 Ω + 28 Ω = 228 Ω 。 在不同增益电阻值的情况下计算RJ 米, s e首先要求计算两个β值,见公式16和公式17。

输入电阻 R在, se的计算见公式18。

这个值与原来计算的267Ω稍有不同,但对RT的计算没有显著的影响,因为R 在如果T 是并联的关系。

如果需要更精确的总体增益,可以使用更高精度或串联的可调电阻。

述的单次迭代方法非常适合闭环增益为1或2的场合。 增益越高,RTS的值越接近RG值,用公式18计算的R在, se 值与用公式12计算的R在, se值之间的差异就越大。 在这些情况下要求采用多次迭代。

多次迭代并不难实现:最近ADI公司发布的可下载的差分放大器计算工具, ADIsimDiffAmp™ (参考文献2)和 ADI Diff Amp Calculator™(参 考文献3)足以担当此任,它们能在几秒内完成上述计算。

输入共模电压范围

输入共模电压范围(ICMVR)规定了正常工作状态下可以施加于差分放大器输入端的电压范围。 在这些输入端上呈现的电压可以被称为ICMV、 V碳化或VA。 这个ICMVR指标经常被误解。 最常遇到的难题是确 定差分放大器输入端的实际电压,特别是相对于输入电压而言。 知道变量V±在厘米 β和VOCM的值后,当β不相等时使用通式19、当β相等时使用简化公式20就可以计算出放大器的输入电压(VA)。±

|

|

(20) |

记住V一个始终是按比例缩小的输入信号,这一点非常有用(见图4)。 不同的放大器类型有不同的输入共模电压范围。 ADI公司的高速差分ADC驱动器有两种输入级配置,即中心型和偏移型。 中心型ADC驱动器的输入电压离每个电压轨有约1V的距离(因此叫中心型)。 而偏移 型输入级增加了两个晶体管,允许输入端电压摆幅更接近–VS轨。 图10是一个典型差分放大器(Q2和Q3)的简化输入原理图。

图10:具有偏移型ICMVR的简化差分放大器。

偏移型输入架构允许差分放大器处理双极性输入信号,即使放大器是采用单电源供电,因此这种架构非常适合输入是地或地电平以下的单电源应用。 在输入端增加的 PNP晶体管(Q1和Q4)可以将差分对的输入电压向上偏移一个晶体管的V是电压 。 例如,当-IN端电压为-0.3V时,A点电压将为0.7V,允许差分对正常工作。 没有 PNP(中心型输入级)时,A点的-0.3V电压将使NPN差分对处于反向偏置状态,因而无法正常工作。

表1提供了ADI公司ADC驱动器的多数指标一览表。 对这张表粗略一看就能发现哪些驱动器具有偏移型ICMVR,哪些没有。

表1:高速ADC驱动器的指标。

|

ADC驱动器 |

ICMVR |

在OCM |

过采样模拟前端增益为10时的ADC噪声预算 |

|

供电电压 |

供电电压 |

输出摆幅(V)

|

我供应(毫安) |

|

产品型号 |

带宽(MHz) |

压摆率(V/µs) |

噪声(nV) |

±5 V

|

±5 V |

±3.3 V

|

±3 V

|

±5 V |

±5 V

|

±3.3 V

|

±3 V

|

|

AD8132 |

360 |

1000 |

8 |

–4.7 至 +3

|

0.3 到 3 |

0.3 到 1.3 |

0.3 到 1 |

±3.6

|

1 到 3.7 |

—

|

0.3 到 1 |

±1

|

12 |

|

AD8137 |

76 |

450 |

8.25 |

–4 至 +4 |

1 到 4 |

1 到 2.3 |

1 到 2 |

±4 |

1 到 4 |

1 到 2.3 |

1 到 2 |

RR |

3.2 |

|

AD8138 |

320 |

1150 |

5 |

–4.7 至 +3.4 |

0.3 到 3.2 |

— |

—

|

±3.8 |

1 到 3.8 |

—

|

—

|

±1.4 |

20 |

|

AD8139 |

410 |

800 |

2.25 |

–4 至 +4 |

1 到 4 |

—

|

—

|

±3.5 |

1.5 到 3.5 |

—

|

— |

RR |

24.5 |

ADA4927-1/

ADA4927-2 |

2300 |

5000 |

1.4 |

–3.5 至 +3.5 |

1.3 到 3.7 |

—

|

—

|

±3.5 |

1.5 到 3.5 |

—

|

—

|

±1.2 |

20 |

ADA4932-1/

ADA4932-2 |

1000 |

2800 |

3.6 |

–4.8 至 +3.2 |

0.2 到 3.2 |

—

|

—

|

±3.8 |

1.2 到 3.2 |

—

|

—

|

±1 |

9 |

ADA4937-1/

ADA4937-2 |

1900 |

6000 |

2.2 |

—

|

0.3 到 3 |

0.3 到 1.2 |

—

|

—

|

1.2 到 3.8 |

1.2 到 2.1 |

—

|

±0.8 |

39.5 |

ADA4938-1/

ADA4938-2 |

1000 |

4700 |

2.6

|

–4.7 至 +3.4 |

0.3 到 3.4 |

—

|

—

|

±3.7 |

1.3 到 3.7

|

—

|

— |

±1.2 |

37 |

ADA4939-1/

ADA4939-2 |

1400 |

6800 |

2.6

|

—

|

1.1 到 3.9 |

0.9 到 2.4 |

—

|

—

|

1.3 到 3.5 |

1.3 到 1.9 |

—

|

±0.8 |

36.5 |

输入和输出耦合:交流或直流

需要交流耦合还是直流耦合对差分ADC驱动器的选择有很大的影响。 输入和输出耦合之间的考虑因素也不同

交流耦合型输入级电路见图11。

图11 :交流耦合型ADC驱动器。

对于采用交流耦合输入的差分至差分应用来说,放大器输入端呈现的直流共模电压等于直流输出共模电压,因为直流反馈电流被 输入电容隔离了。 另外,直流反馈系数也是匹配的,完全等于单位1。 VOCM—和由此得到的直流输入共模电压—经常被设置在电源电压 的一半左右。 具有中心型输入共模范围的ADC驱动器非常适合这类应用,它们的输入共模电压接近规定范围的中心。

交流耦合单端至差分应用与对应的差分输入应用非常相似,但在放大器输入端具有共模纹波—按比例缩小的输入信号"复制品"。 具 有中心型输入共模范围的ADC驱动器将平均输入共模电压设定在规定范围的中间,因而能为大多数应用中的纹波提供足够的富余度。

当输入耦合方式可选时,值得人们注意的是,采用交流耦合输入的ADC驱动器比采用直流耦合输入的相似驱动器耗散更少的功率,因 为两个反馈环路中都不存在直流共模电流。

当ADC要求输入共模电压与驱动器输出端电压完全不同时,交流耦合ADC驱动器的输出就非常有用。 当VOCM值被设在电源电压一半附 近时,驱动器将有最大的输出摆幅,但当驱动要求非常低输入共模电压的低电压ADC时会出现问题。 走出这个困境的简单方法(图12)是驱动器输出和ADC 输入之间采用交流耦合连接,从驱动器输出中去除ADC的直流共模电压,并允许适合ADC的共模电平应用于交流耦合侧。 例如,驱动器可以工作在单5V 电源和 VOCM = 2.5V,条件下,而ADC可以工作在单1.8V电源,此时在标记为ADC CMV的点必需施加0.9V的输入共模电压。

图 12:采用交流耦合输出的直流耦合输入电路

具有偏移型输入共模范围的驱动器一般最适合工作在单电源直流耦合系统中,这是因为输出共模电压通过反馈环路实现了分压,而且它 的可变分量可以非常接近地,即负电压轨。 当采用单端输入时,输入共模电压由于输入相关的纹波而更接近负电压轨

采用双电源、单端或差分输入以及交流或直流耦合的系统通常可以采用任一种输入级电路,因为富余度增加了。

表2总结了在输入耦合和电源的各种组合方式下最常用的ADC驱动器输入级电路类型。 然而,这些选择未必总是最好的,应该对每个系统进行具体分析。

表2:耦合和输入级电路选项

|

输入耦合方式 |

输入信号 |

电源 |

输入类型 |

|

任意 |

任意 |

双电源

|

中心型 |

|

交流耦合 |

单端

|

单电源 |

中心型 |

|

直流耦合 |

单端 |

单电源

|

偏移型 |

交流耦合

|

差分

|

单电源

|

中心型 |

直流耦合

|

差分

|

单电源

|

中心型 |

输出摆幅

为了最大化ADC的动态范围,应该将它驱动到满输入范围。 但需要注意:将ADC驱动得太厉害可能有损输入电路,而驱动不够的话又会降 低分辨率。 将ADC驱动到满输入范围并不意味着放大器输出幅度必须达到最大。 差分输出的一个主要好处是每个输出幅度只需达到传 统单端输出的一半。 驱动器输出可以远离电源轨,从而减少失真。 不过对单端驱动器来说没有这个好处。 当驱动器输出电压接近电压轨时,放大器将损失线性度,并引入失真。

对于对每一毫伏的输出电压都有要求的应用来说,表1显示相当多的ADC驱动器能够提供轨到轨输出,其典型富余量从几毫伏到几百毫伏不等,具体取决于负载

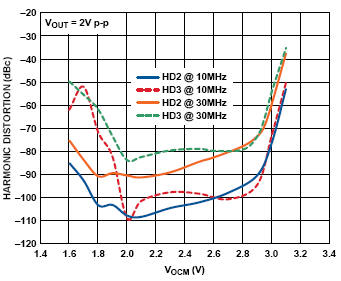

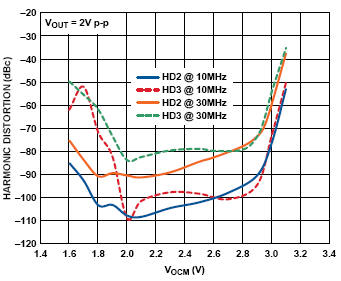

图 13:采用5V电源的ADA4932在各种频率下的谐波失真与VOCM的关系。

图13是 ADA4932在各种频率下的谐波失真与 VOCM的关系图,是典型输出摆幅在每个轨1.2V内(富余量确定的。 输出摆幅是信号的VOCM与V峰之和(1V )。 值得注意的是,失真在2.8V 以上(3.8 V峰或5V往下1.2V)开始迅速增加。 在低端,失真在2.2V (-1 V峰)时仍很低。 同样的现象还将出现在带宽和压摆率的讨论中。

噪声

ADC的非理想特性包括量化噪声、电子或随机噪声和谐波失真。 在大多数应用中重要的一点是,噪声通常是宽带系统中最重要的性能指标。

所有ADC内部都存在量化噪声,并且取决于位数n,n越大量化噪声就越小。 因为即使"理想"转换器也有量化 噪声,因此量化噪声可以用作比较随机噪声和谐波失真的基准。 ADC驱动器的输出噪声应该接近或低于ADC的随机噪声和失真。 下面先讨论 ADC噪声和失真的特征,然后介绍如何衡量ADC驱动器噪声与ADC性能之间的关系。

量化噪声产生的原因是ADC将具有无限分辨率的模拟信号量化成有限数量的离散值。 n位ADC有2n个二进制值。 两个相邻值之间的差代 表了可以分辨的最小差值,这个差值被称为量化等级的最低有效位(L S B),或q。 因此一个量化等级等于转换器量程的1/2n。 如果一个不 断变化的电压经过一个完美的n位ADC转换,然后转换回模拟信号,再从ADC输入中减去这个信号,那么差值看起来就像噪声。 它有一个 公式21计算所得有效值(rms):

|

|

(21) |

从这里可以得出n位ADC在其奈奎斯待带宽上的信号与量化噪声比的对数(dB)公式22,这也是n位转换器所能取得的最佳信噪比(SNR)。

ADC中的随机噪声 包含了热噪声、散粒噪声和闪烁噪声,一般要大于量化噪声。 由于ADC的非线性产生的 谐波失真会在输出信号中产生 与输入信号谐波有关的有害信号。 总的谐波失真和噪声 (THD + N)是一个重要的ADC性能参数,它衡量了电子噪声和谐波失真与接近ADC满 量程输入范围的模拟输入信号之间的关系。 电子噪声积分的带宽包括了所要考虑的最后一个谐波频率。 THD中的"T"(ttotal,总和)包括了前五个谐波失真分量,是连同噪声一起的和的平方根,见公式23。

|

|

(22) |

公式23中的v1是输入信号,在2到在6是前五个谐波失真分量, 在n是ADC的电子噪声。

T HD+噪声)的倒数被称为信号与噪声失真比,简称SINAD,通常用dB表示,见公式24。

如果SINAD被信号与量化噪声比代替(公式22),我们就能定义转换器具有的有效位数(ENOB),前提是这个转换器的信号与量化噪声比与SINAD相同(公式25)。

|

|

(25) |

ENOB也能用SINAD项表达,见公式26。

ENOB可以用来比较ADC驱动器的噪声性能和ADC的噪声性能,进而判断是否适合驱动这个ADC。 图14是一个差分ADC噪声模型。

图 14:差分ADC驱动器的噪声模型

公式27表明了通常情况下当 β1= b2 ≡ β时,八个噪声源中每个源对总输出噪声密度的贡献。

总输出噪声电压密度v不,分米是通过计算这些分量的和平方根得到的。 将这些公式输入电子表格是计算总输出噪声电压密度的最好方式。 ADI公司网站上还新推出了ADI差分放大器计算器(参考文献3),用它能快速计算噪声、增益和差分ADC驱动器的其它参数值。

现在可以将ADC驱动器的噪声性能与ADC的ENOB作一比较。 描述这一过程的例子是为采用5V电源工作的 AD9445 ADC选择和评估一款增益为2、2V 满量程输入的差分驱动器。 它能处理用一个单极点滤波器限制、占用50M H z(-3d B)带宽的直接耦合宽带信号。 从数据手册中记载的各种条件下的 ENOB参数列表中可以发现:对应50MHz的奈奎斯特带宽,ENOB=12位。

ADA4939 是一款能够被直接耦合的高性能宽带差分ADC驱动器。 在 噪声性能方面它是驱动AD9445的合适产品吗? A DA4939数据手册针对近似为2的差分增益推荐的RF=402Ω、RG=200Ω,数据手册给出的 这种情况下的总输出电压噪声密度为9.7nV/Hz。

首先计算给定恒定输入噪声功率谱密度下的系统噪声带宽BN,它是输出与决定系统带宽的实际滤波器相同噪声功率的等效矩形低通滤波器的带宽。 对于一个单极滤波,BN等于π/2乘以3dB带宽,如公式28所示。

|

|

(28) |

然后在系统带宽的平方根内对噪声密度进行积分,得到输出噪声有效值(公式29)。

|

|

(29) |

假定噪声幅度呈高斯分布,那么峰峰值噪声的计算可以使用常见的±3σ门限(在99.7%的时间内噪声电压摆幅位于这些门限之间),见公式30:

|

|

(30) |

现在可以在12位ENOB、2V满量程输入范围基础上对驱动器的峰峰输出噪声和AD9445 LSB的1 LSB电压进行比较,其中LSB的计算见公式31。

|

|

(31) |

相对于12位ENOB,驱动器的峰峰输出噪声与ADC的LSB具有可比性。 因此从噪声角度看,A DA4939驱动器非常适合这种应用。 最终还必须通过搭建和测试驱动器/ADC组合作出决定。

电源电压

考虑电源电压和电流是缩小ADC驱动器选择范围的快速途径。 表1提供了不同电源电压下ADC驱动器性能的快速查找表。 电源电压会影响带宽、信号摆幅和ICMVR 。 衡量这些指标并进行反复权衡对差分放大器的选择而言至关重要。

电源抑制 (PSR)是另外一个重要的参数。 作为放大器输入的电源引脚的作用经常被人忽视。 电源线上或耦合进电源线的任何噪声对输出信号都有潜在的破坏作用。

考虑ADA4937-1的电源线上存在60MHz、50mVp-p的噪声这样一个例子。 它的PSR在50MHz时是-70dB,这意味着电源线上的噪声在放大器 输出端将被减少到约16μV。 在1V满量程输入的16位系统中,1 LSB是15.3μV,因此电源线上的这个噪声将"淹没"LSB。

这种情况可以通过增加串联表贴铁氧体磁珠L1/ L 2和并联旁路电容C1/C2(图15)加以改进。

图 15:电源旁路电路

在50MHz时,磁珠的阻抗是60Ω,10nF(0.01μF)电容的阻抗是0.32Ω,由这两种元件组成的衰减器可以提供45.5dB的衰减(公式32)

|

|

(32) |

上述分压式衰减加上-70d B的PSR总共可提供115d B的抑制效果,因而可将噪声减小到远低于1 LSB的90nVp-p左右。

谐波失真

频域中的低谐波失真在窄带和宽带系统中都很重要。 驱动器中的非线性会在放大器输出端产生单频谐波失真和多频互调失真。

在噪声分析例子中使用的方法可以同样应用于失真分析,即对ADA4939的谐波失真与2V满量程输出时AD 94 45 12位ENOB的1 LSB进行比较。 一个ENOB LSB在噪声分析中代表488μV。

ADA4939规格表中的失真数据为增益为2,比较2德·和 3RD各种频率的谐波。表3显示了增益为2和差分输出摆幅为2 V p-p时的谐波失真数据。

表3:ADA4939的二次和三次谐波失真

|

参数 |

谐波失真 |

|

HD2 @ 10兆赫 |

–102 分贝 |

|

HD2 @ 70兆赫 |

–83 分贝 |

|

HD2 @ 70兆赫 |

–83 分贝

|

|

HD2 @ 100兆赫 |

–77 分贝 |

|

HD2 @ 10兆赫 |

–101 分贝 |

HD2 @ 70兆赫

|

–97 分贝 |

HD2 @ 100兆赫

|

–97 分贝 |

这些数据表明,谐波失真随频率增加而增加,并且在感兴趣带宽(50M Hz)内二次谐波失真要比三次谐波失真糟糕。 在比感兴趣频率更 高的频率点的谐波失真值较高,因此它们的幅度可能被系统频带限制功能所降低。 如果系统有一个50MHz的砖墙式滤波器,那么就只需要考虑超过25MHz 的频率点,因为更高频率的所有谐波将被滤波器滤除。 尽管如此,我们还是要评估频率最高为50MHz的系统,因为目 前的所有滤波器对谐波的抑制可能都不够,失真分量可能混叠回信号带宽内。 图16给出了ADA4939在各种电源电压和2Vp-p输出时的谐波失真与频率的关系。

图 16:谐波失真与频率的关系

50MHz时的二次谐波失真相对于2Vp-p输入信号来说大约是-88dBc。 为了比较谐波失真水平和1 ENOB LSB,这个谐波失真值必须被转换成电压值,如公式33所示。

这个失真值只有80μVp-p,或1 ENOB LSB的16%。 因此,从失真的角度看,可以认为ADA4939是AD9445 ADC驱动器的很好选择。

由于ADC驱动器是负反馈放大器,输出失真取决于放大器电路中的环路增益值。 负反馈放大器固有的开环失真将被减少 1/(1+L G)倍,其中LG代表可用环路增益。

放大器的输入(误差电压)被乘以一个大的前向电压增益A(s),然后通过反馈系数β传送到输入端,再通过调整输出使误差最小。 这样, 这类放大器的环路增益为A(s)×β。 随着环路增益(A(s), β或两者)的降低,谐波失真将增加。 电压反馈放大器,如积分器,被设计在直流 和低频率处具有大的A(s),然后随着1/f在规定高频点趋向于1而发生滚降。 随着A(s)的滚降,环路增益下降,失真增加。 因此谐波失真参数是A(s)的倒数。

电流反馈放大器将误差电流用作反馈信号。 误差电流被乘以一个大的前向互阻T(s)而转换成输出电压,然后通过反馈系数 1/R F将输出电压转换成反馈电流,以便使输入误差电流最小。 因此理想的电流反 馈放大器的环路增益是 T(s) × (1/RF) = T(s)/RF。 同 A(s)一样, T(s)也有一个 大的直流值,并随着频率的增加而滚降,从而降低环路增益,增加谐波失真。

环路增益还直接取决于反馈系数1/RF。 理想电流反馈放大器的环路增益并不取决于闭环电压增益,因此谐波性能不会随着闭环增益 的增加而下降。 在实际的电流反馈放大器中,环路增益确实某种程度上取决于闭环增益,但不会达到电压反馈放大器中那样的程度。 因此对于高闭环增益和低失真的应用来说,电流反馈放大器,比如 ADA4927, 是比电压反馈放大器更好的选择。 从图17可以看出随着闭环增益的增加失真性能保持得有多好。

图 17:失真与频率和增益的关系

带宽和压摆率

带宽和压摆率在ADC驱动器应用中特别重要。 一般情况下,器件的带宽是指小信号带宽,而压摆率衡量的是大信号摆幅时放大器输出端的最大变化率。

EUBW(有效可用带宽) , 一 个类似于ENOB(有效位数)的首字母缩略词,用于描述带宽。 许多ADC驱动器和运放自称有很宽的带宽指标, 但并不是所有带宽都是可用的。 例如,-3dB带宽是测量带宽的一种传统方法,但它并不意味着所有带宽是可用的。 -3dB带宽的幅度和 相位误差的使用比实际"截止"频率要早十年。 那么什么是放大器的EUBW? 如何确定它的大小? 确定可用带宽的一个极好方法是查询数据手册上的失真图。

图18表明,为了使二次和三次谐波保持大于-80dBc,这个ADC驱动器不应用于超过60MHz的频率。 由于每个应用都不尽相同,系统要求将 成为具有足够带宽和足够失真性能的合适驱动器的选择准则。

图 18:ADA4937电流反馈型ADC驱动器的失真曲线

压摆率,一种大信号参数,指的是放大器输出在没有过高失真的情况下能够跟踪输入的最大变化率。 以压摆率考虑正弦波输出

|

|

(34) |

公式34在过零点的导数(变化率)即最大变化率,它等于:

|

|

(35) |

其中 dv/dt max是压摆率,Vp是峰值电压,f等于满功率带宽(FPBW)。 推算FPBW:

|

|

(36) |

因此,在选择ADC驱动器时,重点要考虑增益、带宽和压摆率(FPBW),以确定放大器是否足够满足应用要求。

稳定性

关于差分ADC驱动器的稳定性考虑与运放是一样的,关键参数是相位余量。 虽然特定放大器配置的相位余量可以从数据手册中获取, 但在实际系统中由于PCB版图中的寄生效应这个相位余量会有显著降低。

负电压反馈放大器的稳定性取决于其环路增益的大小和符号, A(s) × β. 差分ADC驱动器要比典型的运放电路稍微复杂一点,因为它 有两个反馈系数。 在公式7和公式8的分母中可以见到环路增益。 公式37提供了在反馈系数不匹配(β1≠ b2)情况下的环路增益。

当反馈系数不匹配时,有效反馈系数是两个反馈系数的简单平均值。 当它们匹配并被定义为β时,环路增益可以简化为 A(s) × β.

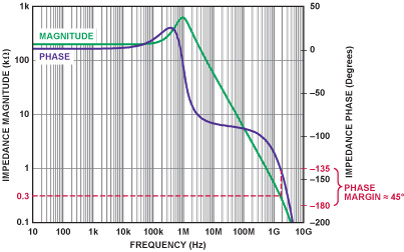

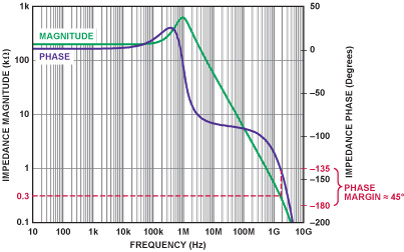

要想使反馈放大器稳定,其环路增益不允许等于-1(相当于相位偏移-180°、幅度为1)。 对于电压反馈放大器来说,其开环增益频率图上环路增益 值等于1(即0dB)的点正是A(s)值等于反馈系数倒数的地方。 对于基本的放大器应用,反馈是纯阻性的,在反馈环路中不会引入 相位偏移。 在反馈系数匹配的情况下,与频率无关的反馈系数倒数 1 + RF/RG通常被称为噪声增益。 如果将以 dB为单位的恒定噪声增益与开环增益A(s)绘制在同一张图上,那么两条曲线的交叉点就是环路增益为1或0dB的地方。 在这个频率点的A(s) 相位与-180°之间的差值被定义为相位余量。 为了稳定工作,这个相位余量应大于或等于45°。 图19给出了 RF/RG = 1 (噪声增益 =2)时A DA4932的单位环路增益点和相位余量。

图19:ADA4932开环增益幅度和相位与频率的关系

进一步观察图19可以发现,A DA4932在噪声增益为1(每个环路中100%反馈)时有约50°的相位余量。 虽然让ADC驱动器工作在零增益有点不切实际,但这一结果表明,A DA4932可以稳定工作在小数差分增益(如RF/RG=0.25,噪声增益=1.25 )。 并不是所有差 分ADC驱动器都能这样。 最小稳定增益可以在所有ADC驱动器的数据手册中找到。

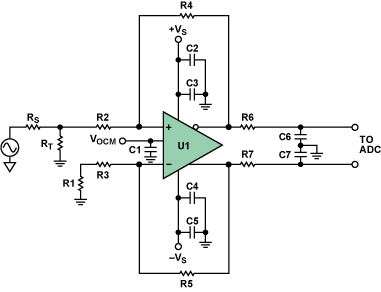

电流反馈ADC驱动器的相位增益同样可以从开环响应中判断。 电流反馈放大器不再使用前向增益A(s),而是 使 用前向互阻T(s),并 将误 差电流用作反馈信号。 带匹配反馈电阻的电流反馈驱动器的环路增益等于T(s)/RF,因此电流反馈放大器环路增益幅度在T(s)=RF时等于1(即0dB)。 这个点在开环互阻和相位图上很容易找到,定位方法与电压反馈放大器相同。 注意,绘制电阻与1kΩ的比值能使阻值表示在对数图上。 图20给出了RF=300时A DA4927电流反馈差分ADC驱动器的单位环路增益点和相位余量。

图20:ADA4927开环增益幅度和相位与频率的关系

300 Ω反馈电阻水平线与互阻幅度曲线的交叉点是环路增益为0dB的地方。 在 这个频率点,T(s)的相位接近-13 5°,因此 有45°的相位余量。 相位余量和稳定性随RF的增加而增加,随RF的减小而减小。 电流反馈放大器应始终使用具有足够相位余量的纯电阻反馈

PCB版图

在稳定的ADC驱动器设计好后,还必须在PCB上实现。 由于电路板存在寄生成分,总是会损失一些相位余量,因此电路板的寄生效应必 须保持最小,其中特别要关注的是负载电容、反馈环路电感和求和节点电容。 每种寄生电抗都会给反馈环路增加迟滞性相位偏移,从而减小相位余量。 由于 PCB版图设计不良可能导致20°以上的相位余量损失。

在使用电压反馈放大器时最好使用尽可能小的RF,以便最小化由 RF和求和节点电容组成的极点引起的相位偏移。 如果要求使用大的RF,寄生电容可以用跨接每个反馈电阻的小电容CF进行补偿,对CF的要求是RFCF等于RG乘以求和节点电容。

PCB版图是设计中最后的必要步骤之一。 遗憾的是,它也是设计中最容易被忽视的步骤之一,即使性能高度依赖于版图设计的高速电路 也是如此。 马虎或拙劣的版图设计可能降低一个高性能设计的性能,甚至使它不能工作。 虽然本文无法涵盖正确高速PCB 设计的所有方面,但还是要介绍一些关键点。

寄生成分将损害高速电路的性能。 寄生电容是由元器件的焊盘、走线、地平面或电源平面引起的。 没有地平面的长走线将形成寄生电 感,进而导致瞬态响应中的振铃和其它不稳定现象。 寄生电容在放大器的求和节点处特别危险,因为它会在反馈响应中引入一个极点, 造成尖峰和不稳定。 一种解决方案是确保ADC驱动器安装和反馈元件焊盘下方区域的所有电路板层都是干净的地和电源平面。

要使有害寄生电抗最小,首先要使所有走线尽可能短。 RF-4印制板的外层50Ω走线产生的寄生参数大约为2.8p F/英寸和7n H/英寸。 内层50Ω走线的寄生电抗将在此基础上增加约30%。 还要确保在长走线下方有地平面,以使走线电感最小。 保持短小的走线有助于减小寄生电容和寄生电感—并保持设计的完整性。

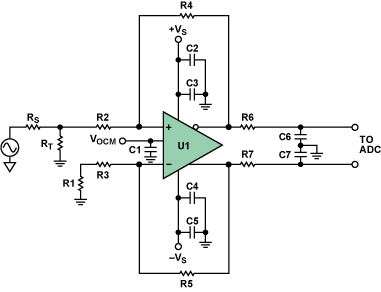

电源旁路是版图设计中另一个重要的考虑因素。 确保电源旁路电容和VOCM旁路电容尽可能靠近放大器引脚放置。 另外,在电源上使用 多个旁路电容有助于确保为宽带噪声提供低阻抗路径。 图21给出了一个带旁路和输出低通滤波器的典型差分放大器原理图。 低通滤波 器用于限制进入ADC的带宽和噪声。 理想情况下,电源旁路电容回路靠近负载回路,这有助于减小地平面中的环流,从而改善ADC驱动 器性能(图22a和图22b)。

图21 :带电源旁路电路和输出低通滤波器的ADC驱动器

使用地平面和一般的接地技巧是一个具体而复杂的课题,不在本文讨论的范围之内。 不过有几个要点需要指出,见图22a和图22b。 首先,只在一个点将模拟和数字地连接在一起,记住只是单点接地。 这样做可以使地平面中模拟和数字电流的交互作用最小,而这种交互最终将导致系统中产生"噪声"。 另外,要将模拟电源终接到模拟电源 平面,数字电源终接到数字电源平面。 对于混合信号IC,要将模拟回路终接到模拟地平面,将数字地回路终接到数字地平面。

图23:混合信号的接地方式

图 23.混合信号接地。

我们希望当您用ADC驱动器进行设计时这里提供的材料有助于您更加全面地考虑众多必要因素。 理解差分放大器—并在项目开始时就留意ADC驱动器设计的细节—将使设计过程中发生的问题最少,并使您远离ADC驱动器故障。

审核编辑:郭婷

(责任编辑:admin) |