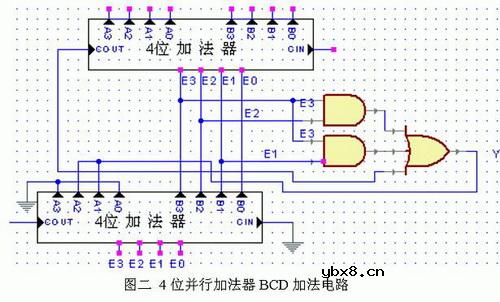

图二所示为4位并行的BCD加法器电路。其中上面加法器的输入来自低一级的BCD数字。下面加法器BCD的输出E3、E2、E1、E0和COUT至高一级 BCD数字,其A3和A1位接地,即当BCD校验信号为真时Y=1,A3A2A1A0= 0110,以实现加6的调整.当不需要BCD调整时Y=0,此时A3A2A1A0=0000,从而使输出结果无变化.

虽然4位并行加法器运算速度较快,但是所用逻辑门较多。

相关热词:#加法器

RS485基本知识介绍

RS485基本知识介绍

时间:2026-04-18

什么是激光雷达?激光雷达的构成与分类

什么是激光雷达?激光雷达的构成与分类

时间:2026-04-18

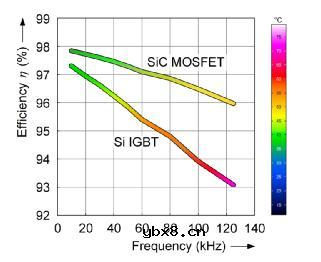

Excelpoint - 一文了解SiC MOS的应用

Excelpoint - 一文了解SiC MOS的应用

时间:2026-04-18

什么是磁电阻器?磁电阻特性及应用

什么是磁电阻器?磁电阻特性及应用

时间:2026-04-18

什么是电场?电场在电容器中的应用

什么是电场?电场在电容器中的应用

时间:2026-04-18

什么是ARM64?

什么是ARM64?

时间:2026-04-17

vga和hdmi的区别

vga和hdmi的区别

时间:2026-04-17

什么是ESD?ESD及TVS的原理和应用

什么是ESD?ESD及TVS的原理和应用

时间:2026-04-17

开关电源原理与维修完整版 (10)_标清视频

开关电源原理与维修完整版 (10)_标清视频

时间:2026-04-16

开关电源原理与维修完整版 (11)_标清视频

开关电源原理与维修完整版 (11)_标清视频

时间:2026-04-16

基于逻辑门的构成解释如何完成任意逻辑的管...

基于逻辑门的构成解释如何完成任意逻辑的管...

时间:2026-03-08

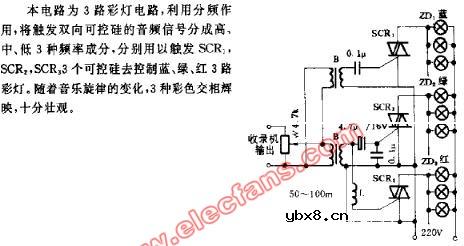

彩灯电路

彩灯电路

时间:2026-03-05

NE555的有趣电路设计分享

NE555的有趣电路设计分享

时间:2026-03-08

三相异步电动机原理

三相异步电动机原理

时间:2026-03-04

三相异步电动机的拆装详讲

三相异步电动机的拆装详讲

时间:2026-03-04

从0学电路,万用表演示测量三极管方法

从0学电路,万用表演示测量三极管方法

时间:2026-03-08

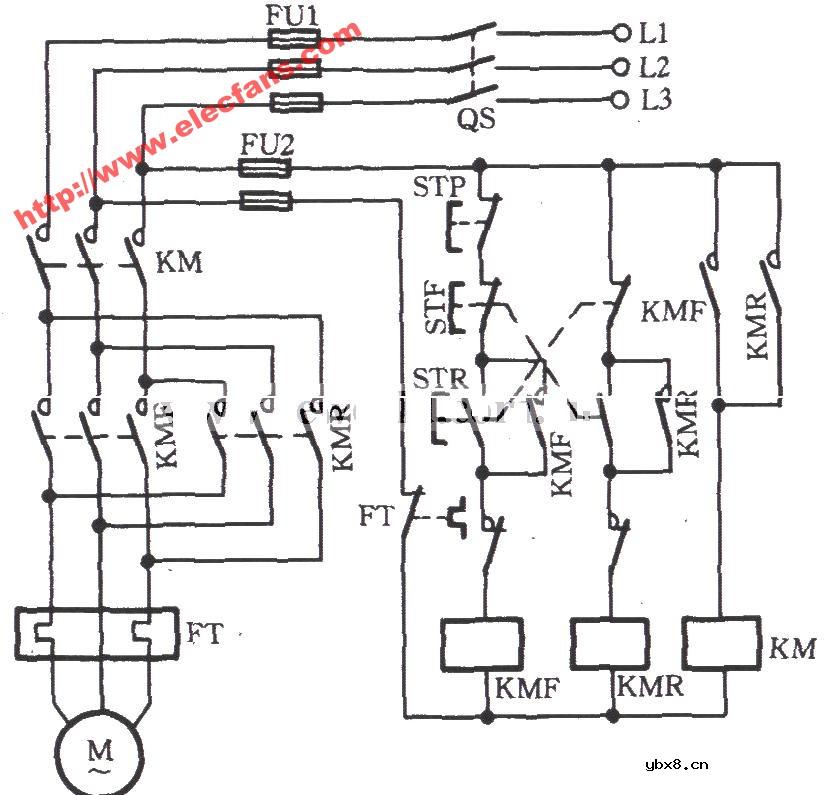

电动机单线远程正反转控制电路图

电动机单线远程正反转控制电路图

时间:2026-03-04

光耦在电子电路中作用、关键参数详解

光耦在电子电路中作用、关键参数详解

时间:2026-03-08

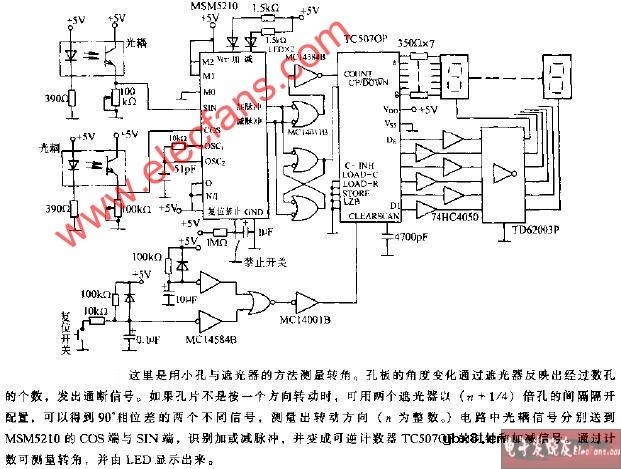

转角测量电路

转角测量电路

时间:2026-03-05

H桥电机驱动电路解析

H桥电机驱动电路解析

时间:2026-03-08