八位加法器仿真波形图设计解析

八位加法器仿真波形图设计解析

电路图基础2026-03-07

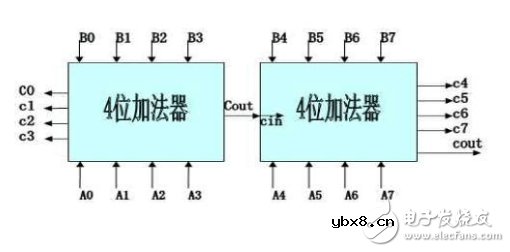

8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位

加法器内部电路原理

加法器内部电路原理

电路图基础2026-03-07

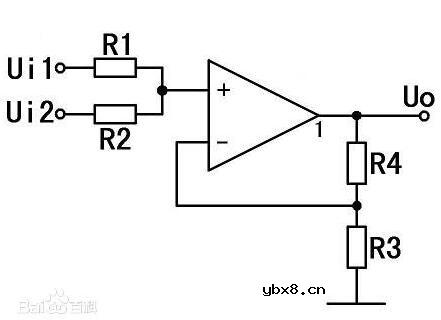

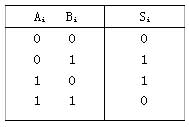

一、加法器 加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻

超前进位集成4(四)位加法器74LS283

超前进位集成4(四)位加法器74LS283

电路图基础2026-03-06

超前进位集成4位加法器74LS283 由于串行进位加法器的速度受到进位信号的限制,人们又设计了一种多位数超前进位加法逻辑电路,使每位的进位只由加数和被加数决定,而与低位的进位无关。现在介绍超前进位的概念。

用四位全加器构成二一十进制加法器

用四位全加器构成二一十进制加法器

电路图基础2026-03-06

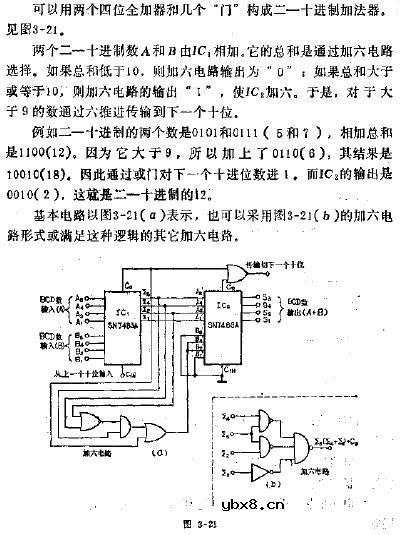

用四位全加器构成二一十进制加法器

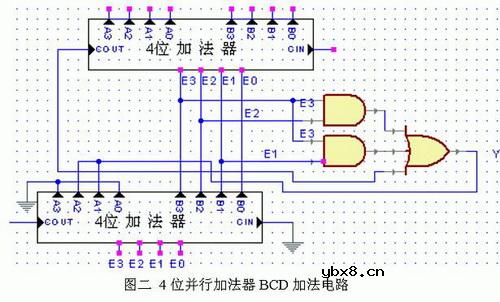

4位并行的BCD加法器电路图

4位并行的BCD加法器电路图

电路图基础2026-03-05

图二所示为4位并行的BCD加法器电路。其中上面加法器的输入来自低一级的BCD数字。下面加法器BCD的输出E3、E2、E1、E0和COUT至高一级 BCD数字,其A3和A1位接地,即当BCD校验信号为真时Y=1,A3A2A1A0= 0110,以实现加

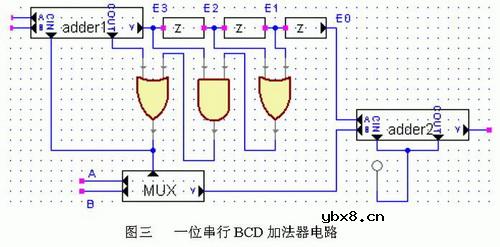

一位串行BCD加法器电路

一位串行BCD加法器电路

电路图基础2026-03-05

图三所示为一位串行BCD加法器。它是以牺牲速度以达到减少硬件逻辑门的目的,这种电路在对频率要求不高的系统中非常之适用。其中ADDER1、ADDER2均为一位全加器。ADDER1 做主运算器,ADDER2做BCD校验运算器,不管是否做

加法器,加法器是什么意思

加法器,加法器是什么意思

电工问答2026-03-04

加法器,加法器是什么意思 加法器 : 加法器是为了实现加法的。 即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全

RS485基本知识介绍

RS485基本知识介绍

时间:2026-04-18

什么是激光雷达?激光雷达的构成与分类

什么是激光雷达?激光雷达的构成与分类

时间:2026-04-18

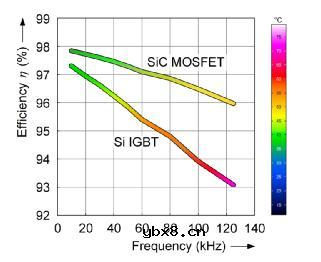

Excelpoint - 一文了解SiC MOS的应用

Excelpoint - 一文了解SiC MOS的应用

时间:2026-04-18

什么是磁电阻器?磁电阻特性及应用

什么是磁电阻器?磁电阻特性及应用

时间:2026-04-18

什么是电场?电场在电容器中的应用

什么是电场?电场在电容器中的应用

时间:2026-04-18

什么是ARM64?

什么是ARM64?

时间:2026-04-17

vga和hdmi的区别

vga和hdmi的区别

时间:2026-04-17

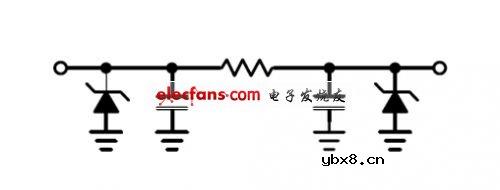

什么是ESD?ESD及TVS的原理和应用

什么是ESD?ESD及TVS的原理和应用

时间:2026-04-17

开关电源原理与维修完整版 (10)_标清视频

开关电源原理与维修完整版 (10)_标清视频

时间:2026-04-16

开关电源原理与维修完整版 (11)_标清视频

开关电源原理与维修完整版 (11)_标清视频

时间:2026-04-16

什么是追踪缓存/转接卡?

什么是追踪缓存/转接卡?

时间:2026-03-06

GPS接收机的分类

GPS接收机的分类

时间:2026-03-07

什么是GPS旅行提示器/屏幕尺寸

什么是GPS旅行提示器/屏幕尺寸

时间:2026-03-07

GPS的WAAS跟踪性能

GPS的WAAS跟踪性能

时间:2026-03-07

GPS设备的动态性能

GPS设备的动态性能

时间:2026-03-07

EMC和ESD防护技术

EMC和ESD防护技术

时间:2026-03-05

GPS设备的地图功能

GPS设备的地图功能

时间:2026-03-07

坐标基准

坐标基准

时间:2026-03-07

GPS的接口有哪些类型?

GPS的接口有哪些类型?

时间:2026-03-07

什么是EPIC

什么是EPIC

时间:2026-03-06