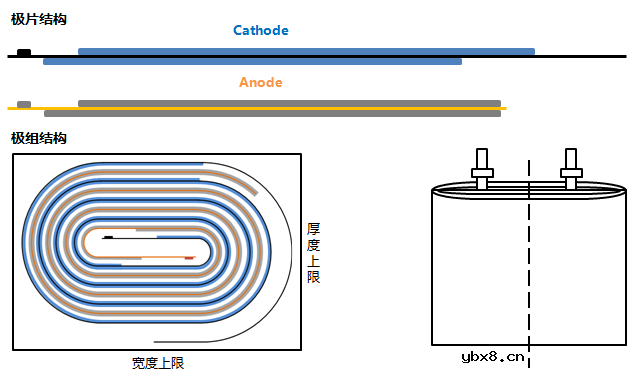

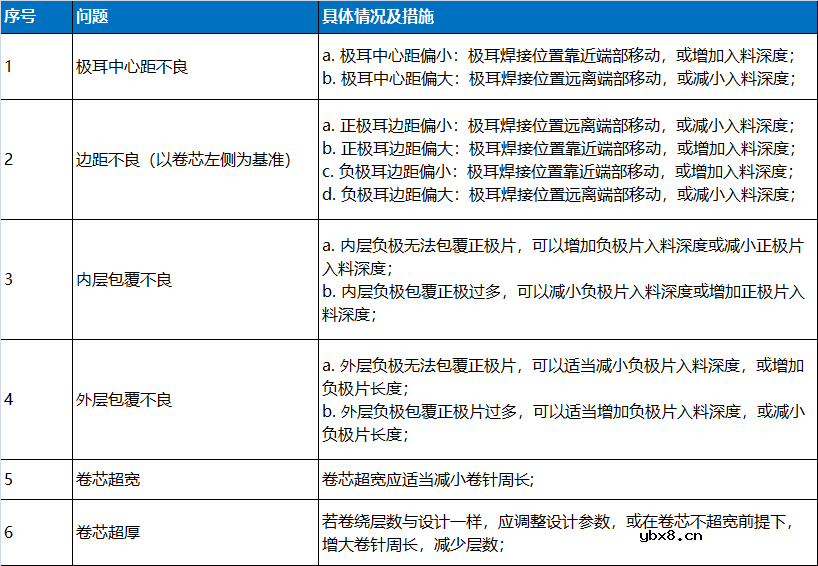

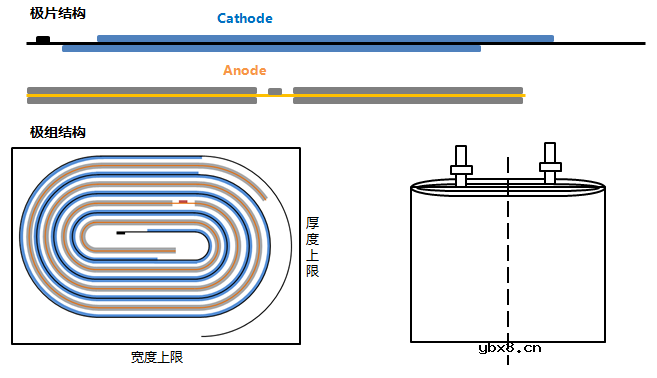

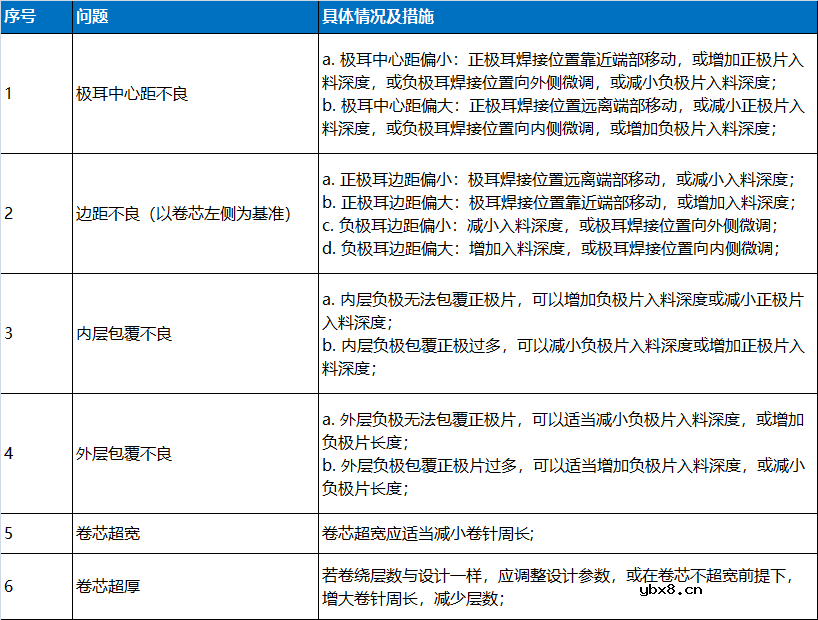

一、IIT结构

IIT(In-In-Tab)结构的卷芯,正负极耳均焊接在头部,极片入料时可以较好地控制极耳位置,通常极耳中心距和边距不良的情况较少。

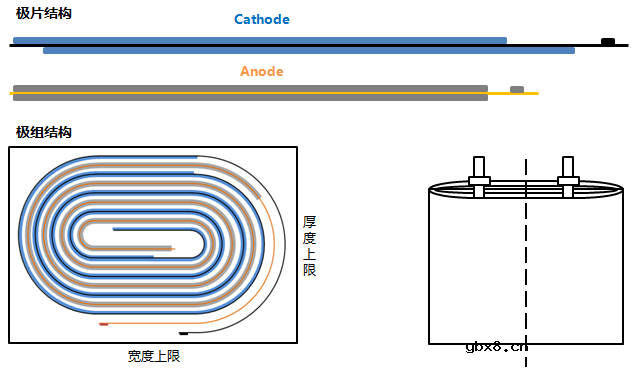

附图1:IIT结构极片及极组示意图

附表1:IIT结构试卷问题及解决措施

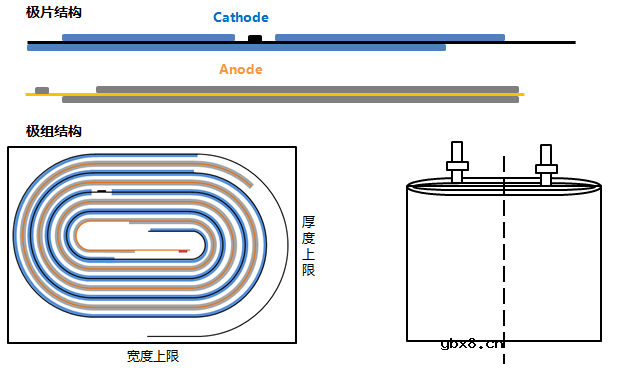

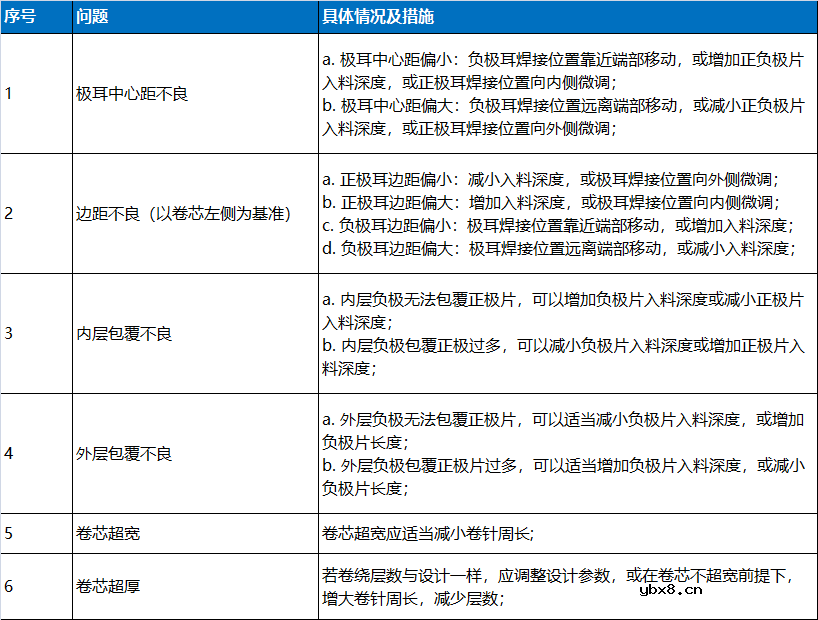

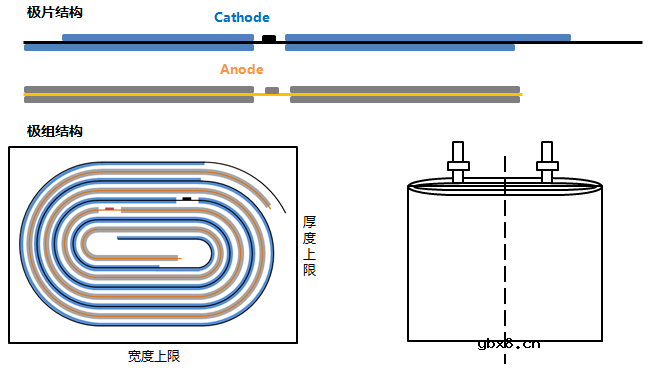

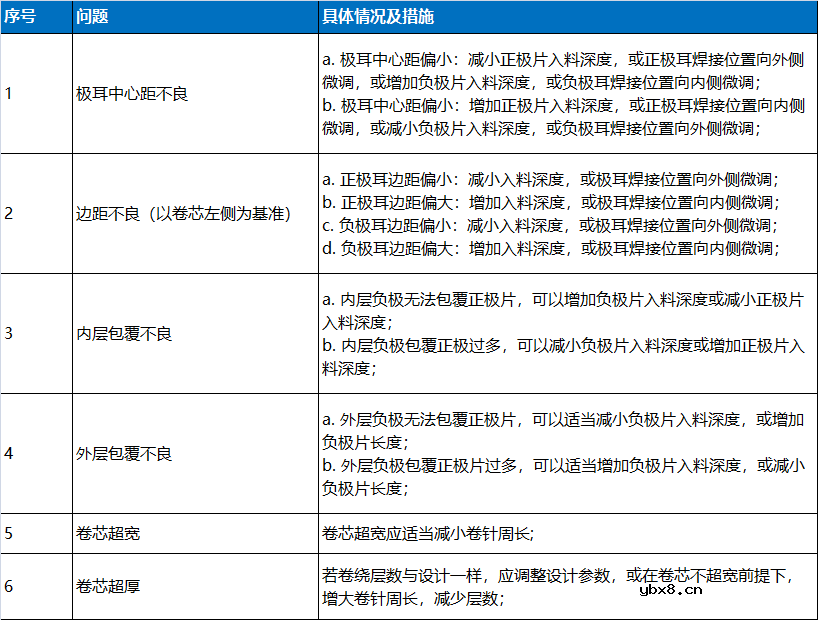

二、MIT结构

MIT(Mid-In-Tab)结构的卷芯,正极耳焊接在极片中间,而负极耳焊接在头部,相比IIT结构,中心距和边距更难控制。

附图2:MIT结构极片及极组示意图

附表2:MIT结构试卷问题及解决措施

三、IMT结构

IMT(In-Mid-Tab)结构的卷芯,负极耳焊接在极片中间,而正极耳焊接在头部,与MIT结构类似。

附图3:IMT结构极片及极组示意图

附表3:IMT结构试卷问题及解决措施

四、MMT结构

MMT(Mid-Mid-Tab)结构的卷芯,正负极耳均焊接在极片中间,中心距和边距较难控制。

附图4:MMT结构极片及极组示意图

附表4:MMT结构试卷问题及解决措施

五、OOT结构

OOT(Out-Out-Tab)结构的卷芯,正负极耳均焊接在极片尾部,卷绕完成后才能确定极耳位置,与极片一致性关系较大,中心距和边距最难控制。

附图5:OOT结构极片及极组示意图

附表5:OOT结构试卷问题及解决措施

需要注意的是,卷芯尺寸、包覆情况等之间相互存在关联性,如MMT结构卷芯,正极片入料增加后,极耳中心距和正极耳边距都会减小,而负极片入料增加后,极耳边距会减小,而中心距会增大,因此,在调整极片尺寸或极耳位置时,切不可顾此失彼。

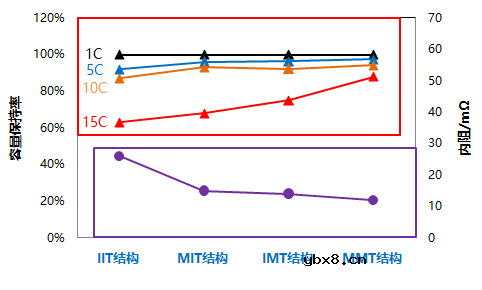

如此多的卷绕结构是基于电芯性能和制造工艺难易程度决定的,通过理论计算说明了极耳中置将会降低75%的集流体内阻,从而提高倍率性能。且有相关文献(高倍率锂电池极耳研究)研究了极耳焊接在不同位置的内阻和倍率性能,结果证实了极耳焊接越靠近极片中心,全电池内阻越小,倍率性能越好。

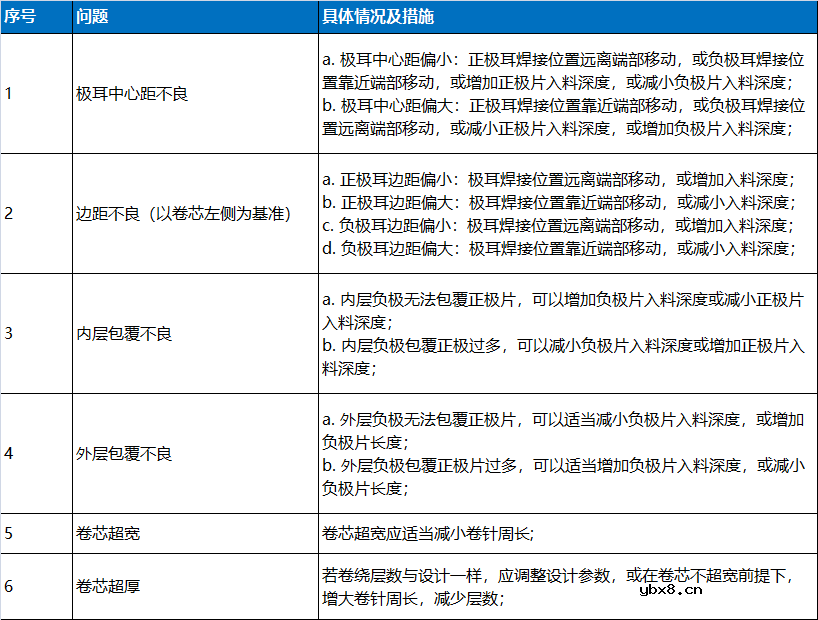

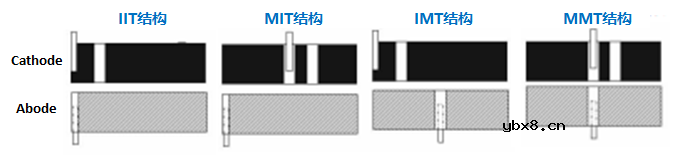

附图6:几种卷芯结构极耳焊接位置示意图

附图7:几种卷芯结构性能对比

由此可见,IIT结构的内阻最大,倍率性能差,MMT结构内阻最小,倍率性能最好,而MIT和ITM介于二者之间,并且负极耳中置的大倍率放电性能比正极耳中置更好。

总 结

1、极耳中置缩短了电子运动路径,可以有效降低全电池欧姆内阻,降低极化,减小温升,提高倍率性能,但增加了工艺复杂度,极耳中心距和边距控制难度增加。

2、IIT结构的电池和OOT结构内阻相差不大,但OOT结构极耳在卷芯外层,因此特别适合窄条形但中心距要求大的电芯,能大大降低正负极耳触碰短路的风险。

使用高压电阻进行设计的 10 个技巧

使用高压电阻进行设计的 10 个技巧

时间:2026-05-07

数字仪表与模拟仪表:它们有何区别?

数字仪表与模拟仪表:它们有何区别?

时间:2026-05-07

基于半导体的电源模块与分立元件

基于半导体的电源模块与分立元件

时间:2026-05-07

一文看懂堆和栈的区别和联系

一文看懂堆和栈的区别和联系

时间:2026-05-07

pcb板和pcba的区别

pcb板和pcba的区别

时间:2026-05-07

什么是数组?数组有什么用?

什么是数组?数组有什么用?

时间:2026-05-07

电感器设计流程和见解

电感器设计流程和见解

时间:2026-05-01

什么是触发器?触发器的作用是什么?

什么是触发器?触发器的作用是什么?

时间:2026-05-01

什么是电源?电源是如何进行分类的?

什么是电源?电源是如何进行分类的?

时间:2026-05-01

电驱动NVH的特点和结构

电驱动NVH的特点和结构

时间:2026-05-01

电阻的原理和作用 电阻色环识别图 电路中电...

电阻的原理和作用 电阻色环识别图 电路中电...

时间:2026-03-09

什么是室温超导?半导体时代将走向结束?芯...

什么是室温超导?半导体时代将走向结束?芯...

时间:2026-03-09

NVIDIA CPU+GPU超级芯片大升级!

NVIDIA CPU+GPU超级芯片大升级!

时间:2026-03-09

半导体光刻工艺 光刻—半导体电路的绘制

半导体光刻工艺 光刻—半导体电路的绘制

时间:2026-03-09

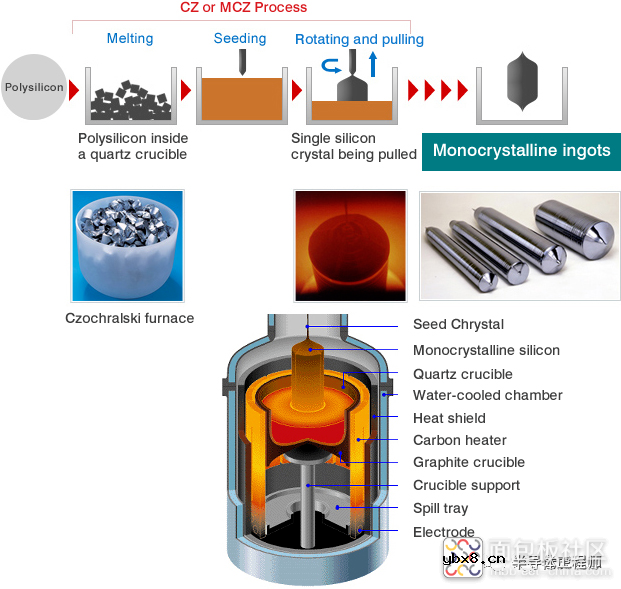

什么是硅片或者晶圆?一文了解半导体硅晶圆

什么是硅片或者晶圆?一文了解半导体硅晶圆

时间:2026-03-09

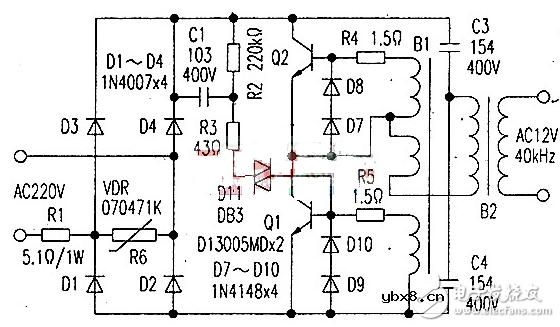

石英灯电子变压器电路原理

石英灯电子变压器电路原理

时间:2026-03-06

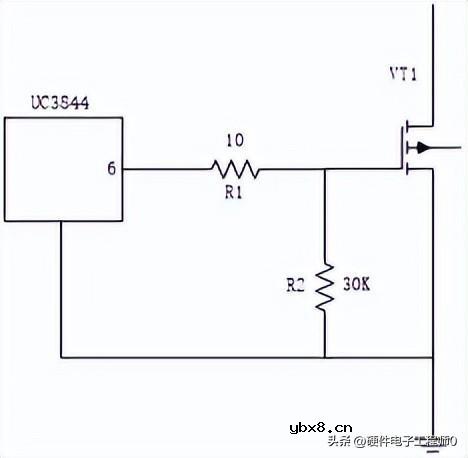

一文详解MOS管驱动电路拓扑的设计

一文详解MOS管驱动电路拓扑的设计

时间:2026-03-09

汽车芯片业应汲取的教训

汽车芯片业应汲取的教训

时间:2026-03-09

半导体行业之ICT技术简介

半导体行业之ICT技术简介

时间:2026-03-09

集成电路的几纳米代表了什么?

集成电路的几纳米代表了什么?

时间:2026-03-09