|

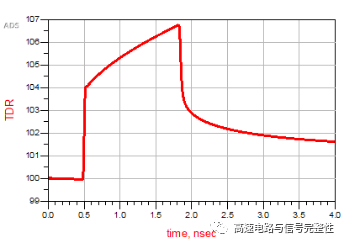

一、传输线的TDR阻抗为什么是上翘的? 在做SI仿真时,经常需要查看差分线的TDR阻抗,我们经常发现即使是一段非常均匀的传输线,其TDR阻抗也是逐渐上翘的,这是为什么呢?如下图所示,是一段5in长的差分微带线,其模型如下,导体材料是copper,电导率为5.8e7.

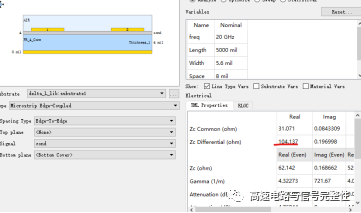

TDR阻抗 我们发现阻抗从104逐渐增加到107了,增加了3欧姆。那这段差分线的阻抗到底是多少呢?104还是107还是两者取平均?我们先用ADS自带的CILD来计算一下,如下图,差分阻抗是104.13欧姆。

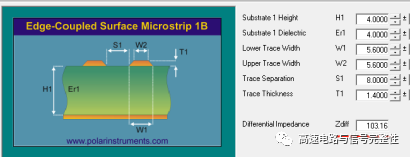

ADS CILD计算结果 我们再看看polar计算的结果,是103.16欧,与104比较接近。这说明这段传输线的阻抗是104欧,应该以TDR的起始点作为阻抗值。那么为啥TDR阻抗要上翘呢?

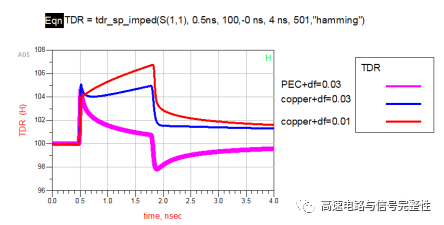

Polar计算结果 二、TDR阻抗上翘的原理 先来看一个实验,如下图所示,同样的模型,我只改变介质损耗和导体的电导率,3种情况如下图所示,红色就是原始情况,既有导体损耗(默认电导率5.8e7)又有介质损耗(df=0.01)的情况下,TDR曲线是上翘的。而当把介质损耗加大到0.03时,红色TDR变成了蓝色曲线,也就是说上翘减小了,区域平坦了。这时候,再把铜导体改为PEC,我们发现蓝色曲线变成了粉色,TDR不但没有上翘,反而是下降趋势了。是不是觉得很奇怪,好像从来没有见过TDR阻抗往下飘的情况。不着急,且听我娓娓道来。

不同导体损耗和介质损耗下的TDR曲线 上面的实验表明,如果只有单纯的介质损耗,如粉粉色曲线所示,那么TDR其实是往下飘的,正是由于导体损耗的存在,导致了TDR往上飘了。总结以下就是介质损耗导致TDR曲线往下飘,导体损耗导致TDR往上飘。那么两者同时存在的时候,就看谁的比重大,就往哪个方向飘。所以导体损耗才是TDR上飘的罪魁祸首。换句话说,如果导体损耗和介质损耗的比例恰当,也可以不飘,如蓝色曲线所示。 在我们现实情况中,由于导体损耗是一定存在的,同时介质损耗比较低,所以往往看到的大多数情况是上飘。有时候也会看到比较平坦的长走线阻抗,这并不一定是PCB厂家牛逼,而可能是材料的介质损耗较大,如图纸蓝色曲线对应的情况,df=0.03,这是一个损耗较大的介质材料。 当然PCB厂家应该尽量把导体的粗糙度减小点,也会减小导体损耗,使得TDR阻抗更加平坦,这也是跟厂家的工艺相关的。那么作为一个对技术有追求的工程师,一定要多问几个为什么?即为什么导体损耗的存在会使得TDR就往上飘了呢?其实这要从传输线的阻抗公式说起,如下图所示,阻抗

图1 Z是RLGC的函数。在频率比较高的时候,虚部jwl和jwc占据主导,远远大于实部的R和G,因此,Z最终可以化简为下图2的公式。

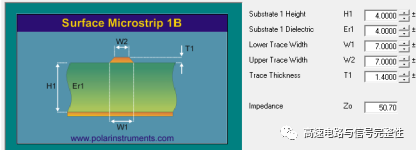

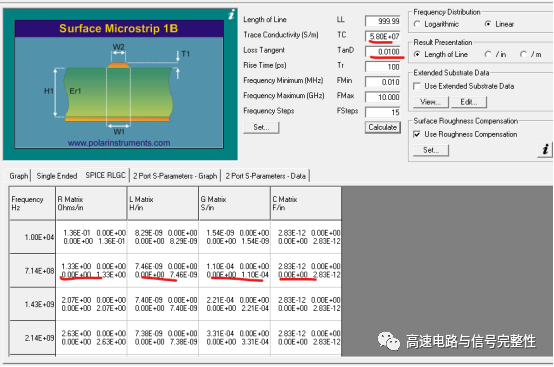

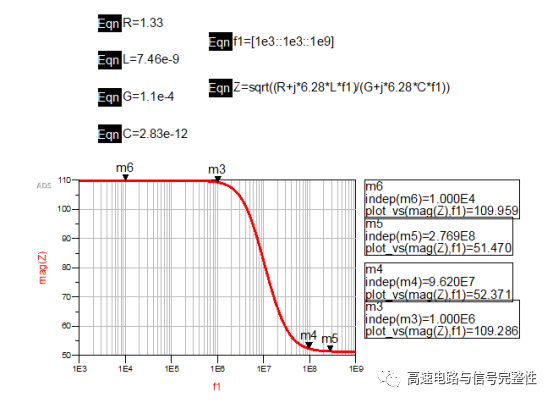

图2 换句话说,Z其实是随频率变化的,只有当频率大于某个频率以后,阻抗才能化简为L/C的开方,并且跟频率不再相关。那么在某个频率之前,阻抗Z究竟是怎么变化的呢?为了研究这个变化的趋势,我们随便设计一段微带线,然后求出RLGC,再根据阻抗Z的公式画出阻抗Z随频率f的变化曲线,如下图:

50欧微带线

等效的RLGC

Z随频率f的变化曲线 在ads里面可以很方便地使用公式画出阻抗Z的曲线图。从图中可以看出,大约在300MHz以后,阻抗Z就呈现定值,不再随频率变化了。那么在1MHz之前,阻抗大约是高频时候的2.2倍左右达到110欧姆,也是一个定值。而从1MHz~300MHz之间特征阻抗呈现下降趋势。这一段频率范围称之为过渡区。 再回到时域TDR测量,由于TDR测量阻抗采用的是时域反射的方法,其信号源是一个跃阶信号的上升沿,其包含非常高的频率分量,很显然,在信号源从0开始上升的瞬间,频率是最高的,包含较多的高频分量(这跟上升沿的时间有关系),所以刚开始的阻抗对用的其实是高频分量感受到的阻抗。随着时间的推移,频率分量从高频往低频下降,那么阻抗就是会逐渐上升的,如上如所示。随着时间越长(走线长度越长),低频分量越低,其阻抗也会越高,因此会看到往上飘的趋势。具体飘到多高主要取决于传输线的长度,也就是信号传输的延迟了。所以TDR曲线在时间上的上飘其实对应着阻抗随频率的下降。

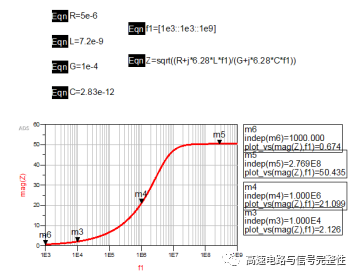

TDR的跃阶信号源 同样,如果是理想导体,没有导体损耗的时候,TDR就是往下飘的,我们也可以用此方法进行分析。如下图是理想导体时,只有介质损耗存在的RLGC。

理想导体下的Z曲线 可以看到,如果导体是理想的,只有介质损耗存在时,通过RLGC值可以画出阻抗Z的曲线就是逐渐上升的。相应的TDR曲线就是往下飘的。 所以在低频的时候,其实主要取决于R/G的比值,当R>>G的时候,其比值就会很大,这时候Z就非常大,那么阻抗频率曲线就是下降的,当R< 三、学习小结 1、综上对于一段长的均匀传输线来说,其TDR上翘的原因是两方面构成: 一是由于导体损耗的存在,即R>>G; 二是TDR测量阻抗的原理是发射跃阶信号源,刚开始上升的很短时刻首先是大部分高频分量(>300MHz)先感受到这个阻抗,随着时间的推移小于300MHz的低频分量再感受到这个阻抗。 所以虽然TDR是时域测量阻抗的方法,但是其时域波形里面仍然包含着不同频率分量所感受到的阻抗,上翘的背后其实是代表着不同频率所感受到的阻抗。而且我们看到,走线越长,这种上翘越明显。同时这种现象也让我们体会到了时域与频域是如何相互转化的过程,即时间从0开始往后增加的过程,其实对应的就是频率从高频往低频下降的过程。 2、在理论上存在TDR阻抗往下的趋势或者平坦的趋势,但现实中基本看不到TDR往下飘的曲线,这是因为现实中的导体损耗不可能忽略,因为不可能存在理想导体。同时也不会存在理想介质。但是我们可以通过对PCB工艺的控制,尽量去减小导体损耗,从而使得曲线更加趋于平坦或者说不要飘的那么厉害。 编辑:黄飞 |