|

导线:元器件与元器件之间的电线 生成接触孔后,下一步就是连接导线。在半导体制程中,连接导线的过程与一般电线的生产过程非常相似,即先制作线的外皮。在一般的电路连接中,直接采用成品电线即可。但在半导体制程中,需要先“制作电线”。

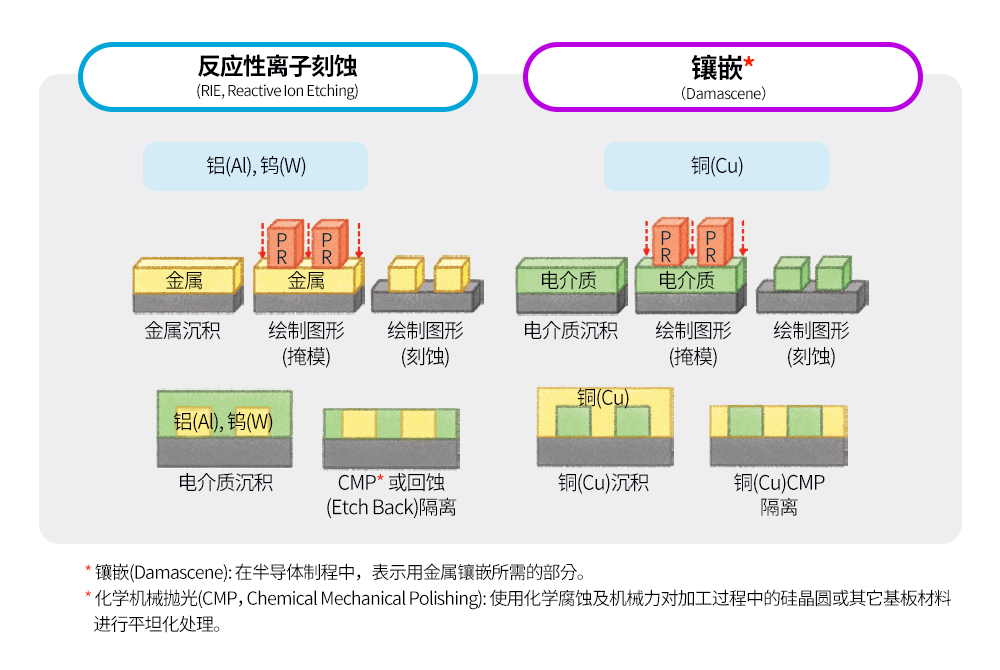

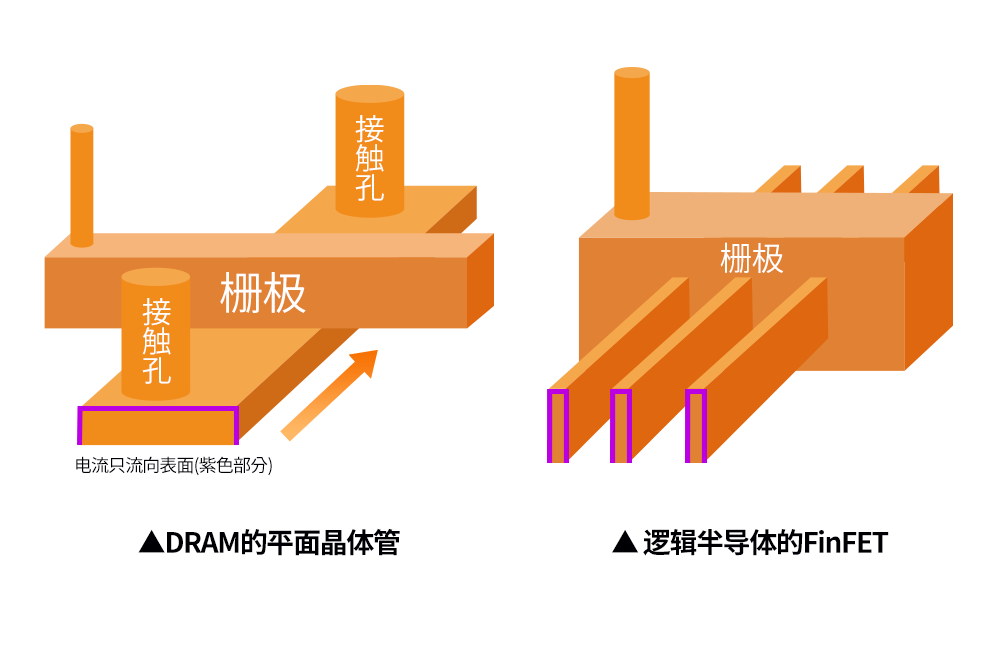

▲ 图5:反应性离子刻蚀(RIE)与镶嵌(Damascene)工艺的比较(摘自:(株)图书出版HANOL出版社[半导体制造技术的理解293p]) 技术的组合 上述技术并非各自独立存在,而是根据各半导体制造商的不同目的,形成各种不同组合,从而生产出厂商希望制造的多种半导体。例如,与SK海力士等芯片制造商不同,台积电(TSMC)、英特尔等逻辑半导体5制造商对晶体管的电流控制能力要求比较高。为此,逻辑半导体制造商采用了FinFET等三维晶体管,实现了三维结构的电流,以增加电流通道的面积。在三维晶体管上生成接触孔,当然要比在DRAM等平面晶体管上难度更大。图6形象地揭示了这两种情况,左图是在平面电流通道生成接触孔,较容易;右图是在三维晶体管上生成接触孔,较难。 5逻辑半导体(logic semiconductors):CPU、GPU等通过处理数字数据来运行电子设备的半导体

▲ 图6:在逻辑半导体的FinFET生成接触孔,要远比在DRAM的平面晶体管生成接触孔难。 导线的金属阻挡层也一样,英特尔在其7纳米工艺中,为解决铜的电迁移6现象,试图用钴配线代替铜,却兜了好几年的圈子。2022年,英特尔在4纳米工艺中又重新回到原点,采用铜配线,试图通过用钽(Ta)和钴金属层包裹铜线来攻克技术难关。英特尔将此称为“强化铜(Enhanced Cu)”。 6电迁移(EM,Electromigration):指在金属导线上施加电流时,移动的电荷撞击金属原子,使其发生迁移的现象。 随着半导体的日益微细化,这种新的挑战将不断出现。对英特尔等CPU制造商来说,元器件的高速运行至关重要。正是由于CPU制造商非常重视元器件的速率,连抗电迁移性能出色的铜配线也遇到了瓶颈。英特尔的几番周折正是为了解决铜配线带来的技术难关。而像SK海力士等芯片制造商,虽然不存在电路运行速率上的问题,但却在堆叠电容维持电荷容量上遇到了难题。微细化给处于不同制造环境的制造商提出的技术难题各有不同。但可以肯定的是,SK海力士在金属布线上的难题也终将出现。 结论 半导体制程可以说是一个“集腋成裘”的过程。一张晶圆需经数百道工艺、数万人联手才能完成。尽管每一名作业人员对最终成品的贡献可能都不及1%,但任何一道工艺出现任何差错,都会影响半导体的整体运行。半导体制程中,每一名工作人员的工作都不是孤立的。我们要铭记:半导体制程的所有工艺都有机地交融在一起,牵一发而动全身。

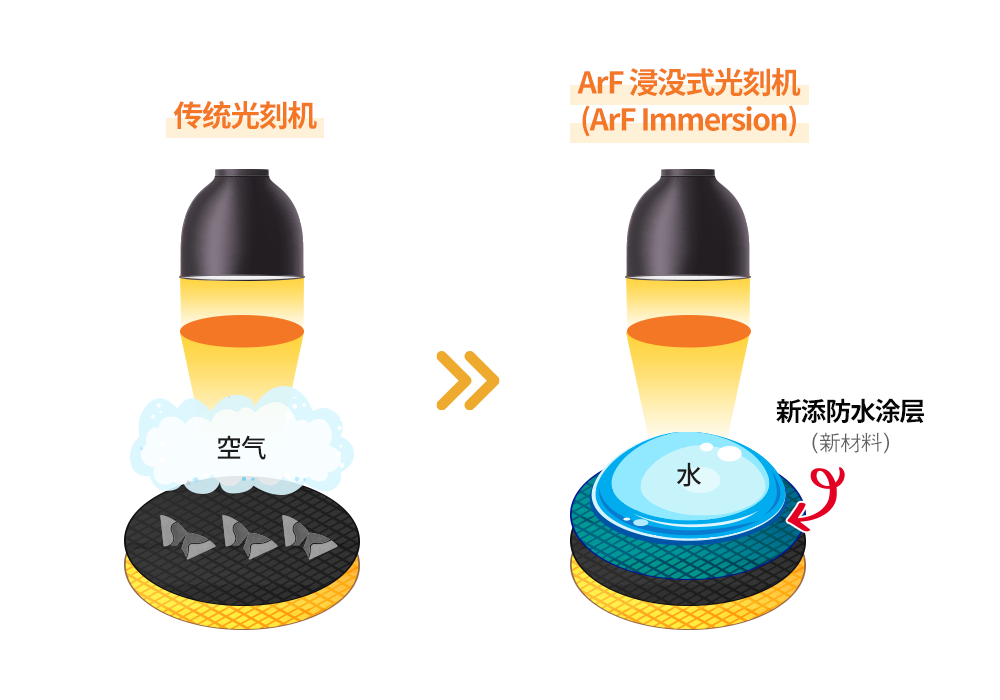

▲图7:用光刻胶解决光刻机带来的新问题

|