|

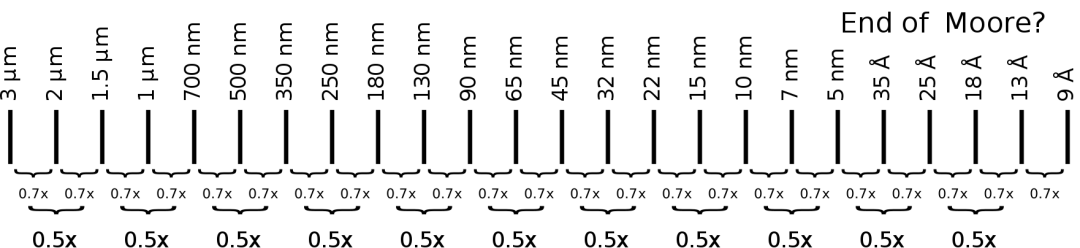

本文翻译自Wikichip. https://en.wikichip.org/wiki/technology_node 技术节点[Technology Node](也称工艺节点[Process Node]、工艺技术[Process Technology]或简称节点[Node])是指特定的半导体制造工艺及其设计规则。不同的节点通常对应着不同的电路世代和架构。一般来说,技术节点越小,意味着特征尺寸越小,生产出的晶体管更小,速度更快,功耗更低。 大约2017年以后,节点名称已完全被市场营销所取代,一些领先的代工厂含糊地使用节点名称来代表略有改动的工艺。此外,代工厂之间晶体管的尺寸、密度和性能也不再匹配。例如,英特尔的10纳米与代工厂的7纳米相当,而英特尔的7纳米与代工厂的5纳米相当。 术语 工艺节点扩展背后的驱动力是摩尔定律。要实现密度翻番,每个节点的接触栅极间距(CPP)和最小金属间距(MMP)大约需要缩小0.7倍。换句话说,0.7× CPP ⋅ 0.7× MMP ≈ ½ 面积。节点名称实际上是摩尔定律驱动下的自我实现预言( self-fulfilling prophecy )。

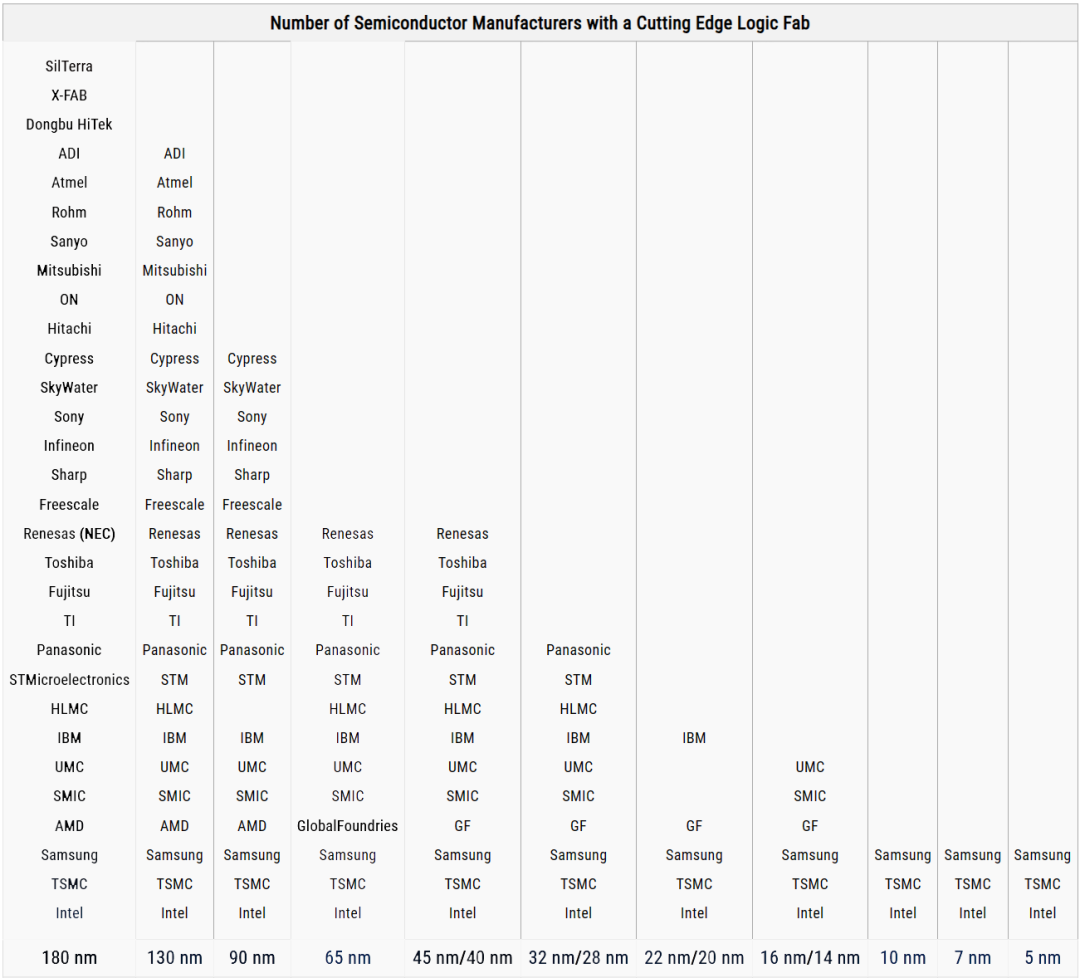

历史 从1960年代MOSFET首次量产到1990年代末,在半导体历史的前35年中,工艺节点大体上是指的是晶体管的栅极长度(Lg),它也被认为是 "最小特征尺寸"。例如,英特尔0.5微米工艺的Lg=0.5µm。这种情况一直持续到1997年的0.25微米工艺,英特尔在这一时期开始使用更激进的栅极长度缩小。例如,其0.25微米工艺的栅极长度为0.20微米,同样,其0.18微米工艺的栅极长度为0.13微米(领先一个节点)。在这些节点上,"工艺节点 "实际上大于栅极长度。 工艺节点这个术语本身可以追溯到1990年代,当时微处理器的发展主要由更高的频率驱动,而DRAM的发展则主要由对大容量的需求驱动。由于更大的容量是通过更高的密度实现的,因此DRAM成为技术发展的驱动力。这种情况一直持续到2000年代。国际半导体技术路线图(ITRS)为半导体行业提供了各种技术节点的指导和帮助。到2006年,随着微处理器开始主导技术的扩展,ITRS用闪存、DRAM和MPU/ASIC的一系列独立指标取代了这一术语。 ITRS传统上将工艺节点定义为制造工艺中允许的第一层金属线的最小半节距。它是用于描述和区分集成电路制造技术的通用指标。 意义的变化 在45纳米工艺中,英特尔传统平面晶体管的栅极长度达到25纳米。在这一节点上,栅极长度的扩展实际上停滞了;栅极长度的任何进一步扩展都会产生不理想的结果。在32纳米工艺节点之后,虽然晶体管的其他方面有所缩小,但栅极长度实际上有所增加。 随着英特尔在其22纳米工艺中引入FinFET,晶体管密度继续增加,而栅极长度基本保持不变。这是由于FinFET的特性造成的;例如,有效沟道长度是新鳍片的函数(Weff = 2* Hfin + Wfin)。由于晶体管与过去相比发生了巨大变化,目前的命名方案失去了意义。 半节点 半节点也可追溯到1990年代,当时很容易实现超量收缩。全技术节点的线性收缩率预计为0.7倍(例如,全收缩后的130纳米变为90纳米)。同样,相关的半节点也有望实现0.9倍的线性收缩。这种想法的前提是,当新的技术节点被考虑当作全节点时,代工厂的设计规则(如标准单元)需要经过提前布局,以兼容18个月后会出现半节点收缩。这样,应对半节点收缩,只需进行各种调整,就可以实现向新工艺的无缝过渡,而不会遇到违反设计规则、时序或其他可靠性问题。请注意,封装等某些步骤确实需要重新设计。 技术发展趋势 随着收缩变得越来越复杂,需要更多的资金、专业知识和资源,能够提供尖端制造工艺的公司数量一直在下降。截至2020年,只有三家公司有能力在最尖端的工艺上制造集成电路:英特尔、三星和台积电。

|