|

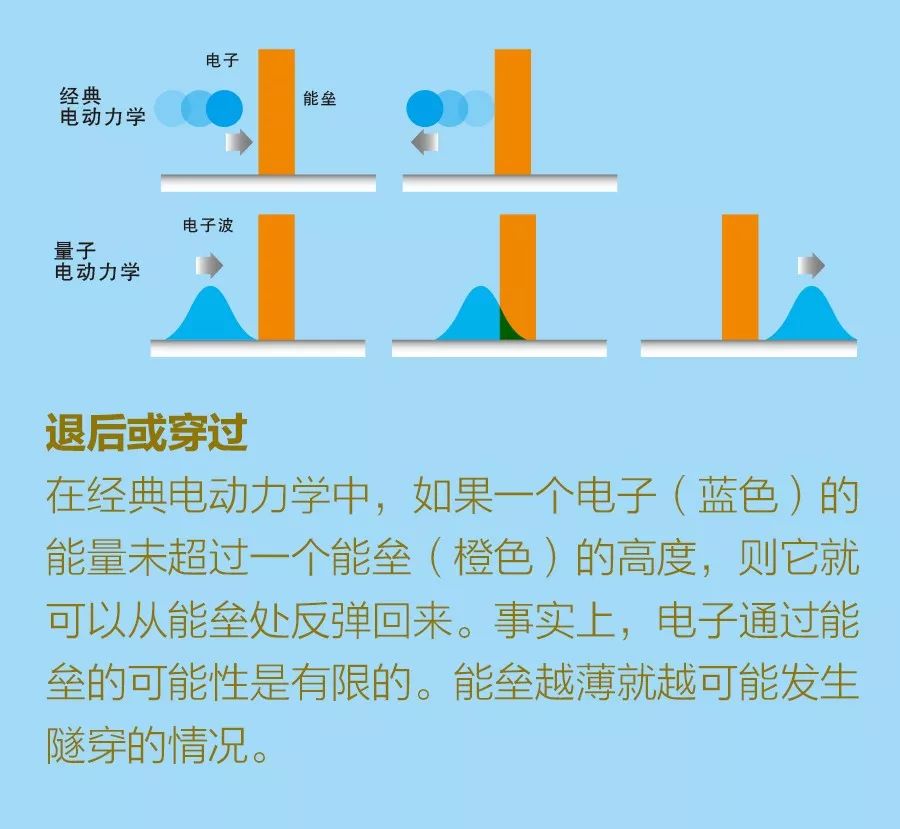

我们所处的这个由永远在线的个人电脑、平板电脑和智能手机构成的世界的诞生,要归功于一个了不起的趋势:金属氧化物半导体场效应晶体管(MOSFET)的不断微型化。MOSFET是大多数集成电路的基础构件,在过去的半个世纪内,其体积已经缩小到了原来的千分之一,从20世纪60年代的数十微米到如今仅数十纳米。随着一代代MOSFET变得越来越小,基于MOSFET的芯片与以前相比运行得更快,也更加省电。 这个趋势带来了工业史上持续时间最长、也是最伟大的一系列胜利,使我们获得了前几代人所无法想象的器件、容量和便利。但是这一稳定的进步受到了威胁,而问题的核心就在于量子力学。 电子有一个让人伤脑筋的能力,即可以穿透能垒——这一现象被称为量子隧穿。随着芯片制造商在一个芯片上安装越来越多的晶体管,晶体管变得越来越小,于是不同晶体管区域之间的距离就被压缩了。因此,曾经厚度足以阻挡电流的电子屏障现在却变得非常薄,使得电子能够从中快速通过。

芯片制造商已经不再削薄构成晶体管的一个重要部分——栅氧化层。该层通过电子将控制晶体管导通和关断的栅极与导电沟道隔开。通过将该氧化层削薄,就可以将更多的电荷导入沟道,加快电流流动,使晶体管运行速度更快。但是,氧化层厚度不能比1纳米小太多,这也是我们今天大概所能达到的程度。如果超出这个限度,当晶体管处于“关断”状态时,会有过多的电荷在沟道内流动,而此时理想的状态是没有任何电荷在流动。这只是若干泄漏点之一。 很长一段时间以来,要确定在哪一年尺寸缩减才能到头一直是件难事。业界的路线图现在预测MOSFET的微型化将持续到2026年,届时栅极长度将仅为5.9纳米——大约是现在长度的四分之一。这一时间表假定我们能够找到更好的材料来堵住泄漏。但是,即便能够找到这个材料,如果希望继续像我们所习惯的那样提升性能,则还需要尽快找到MOSFET的替代品。 我们无法阻止电子隧穿过这个薄薄的屏障,但是,我们可以使这一现象为我们所用。在最近的几年中,一种较新的晶体管设计——隧穿场效应晶体管(TFET)——加速发展。与通过提高或降低能垒来控制电流流动的MOSFET的工作原理不同,TFET的能垒保持高位。该装置通过改变能垒一侧的电子在另一侧出现的可能性来控制导通和关断。 这个工作原理与传统晶体管的工作方式有很大的差别。然而,这也许正是在MOSFET停止发展之时我们所需要大力发展的。它为开发更快、更密集和更加节能的电路来将摩尔定律拓展至下一个十年铺平了道路。 这不是晶体管第一次改变形态。最初,基于半导体的计算机使用的是由双极晶体管制造的电路。但就在硅制的MOSFET于1960年问世的几年之后,工程师们意识到他们可以制造出两个互补的开关,这样它们可以共同组成互补金属氧化物半导体(CMOS)电路。该电路与双极晶体管逻辑不同,只在导通时消耗能量。自从第一个基于CMOS的集成电路在上世纪70年代早期出现后,MOSFET就开始占据市场的主导地位。 从许多方面来看,MOSFET都与双极晶体管没有太大不同。二者都通过提高或降低能垒来控制电流流动——有点像提高或降低河上的水闸。在这个情况下,“河水”即由两种载流子构成:电子和空穴,后者是一个带正电荷的实体,本质上是材料中一个原子的外层能壳上缺少一个电子。 对这些载流子来说,存在两个可被允许的能量范围,或者称能带。拥有足够能量可以在材料中自由流动的电子位于导带。空穴则在低能带(称为“价带”)流动,从一个原子流向另一个原子,很大程度上就像,由于附近的汽车不断开进开出,一个空停车场可能变成一个停满车的停车场。 这些能带都是固定的,但我们可以改变与之相关的能量,通过添加杂质或者掺杂原子的方式使能量变高或者变低,从而改变半导体的传导性。掺杂了额外电子的n型半导体传导带负电荷的电子;通过掺杂造成电子减少的p型半导体传导带正电荷的空穴。 如果我们将这两种半导体类型结合到一起,就会得到一个错位的能带,从而创造了一个介于两者之间的能垒。为制造一个MOSFET,我们在两个互补类型之间注入一种材料,采用n-p-n或者p-n-p的构形。这就在晶体管中间创造出了3个区域:源极(电荷由此进入组件)、沟道和漏极(电荷出口)。

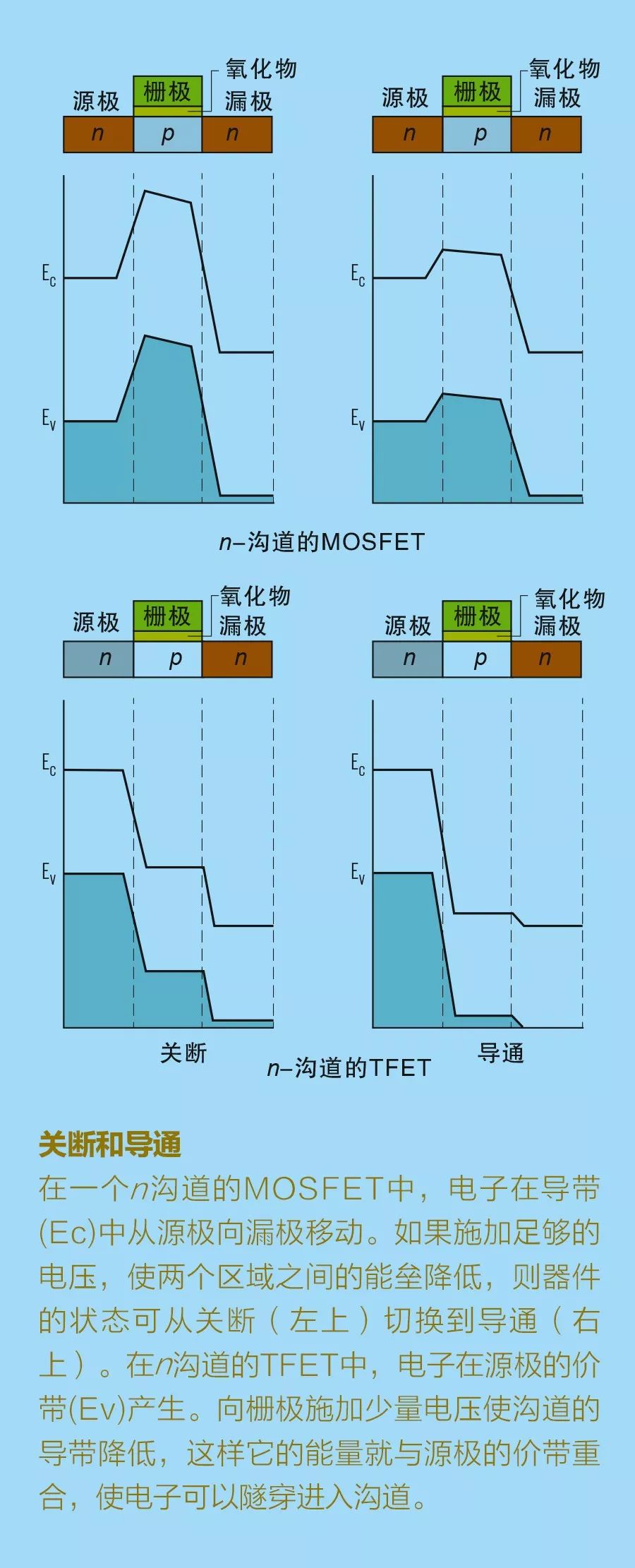

每个晶体管的两个p-n结提供了电荷流动的电子能垒,而晶体管可以通过向沟道上方的栅极施加电压来导通。向n沟道的MOSFET施加一个正电压可使得沟道吸引更多的电子,因为它减少了电子向沟道移动所需的能量。向p沟道的MOSFET施加一个负电压可以对空穴产生相同的效果。 这个简单的降低能垒的方式是半导体电子中应用得最为广泛的电流控制机制。二极管、激光、双极晶体管、晶闸管和大部分场效应晶体管都利用了这种方式。但是这种方式有一个物理局限:晶体管需要一定量的电压才可以被导通或者关断。这是因为电子和空穴由于热能的缘故一直处于运动中,而它们中能量最强的部分会溢出能垒。在室温下,如果能垒减少60毫伏,流经能垒的电流就会增加10倍;每个“十进位”的电流变化需要60毫伏的变化。 所有这些电流泄漏都发生在低于器件的阀值电压时。阀值电压是导通晶体管所需的电压。器件物理学家将这一能垒降低区域称为亚阀值区域,而每十进位60毫伏的电压被认为是最小亚阀值摆幅。为保持低水平能耗,应尽可能降低亚阀值摆幅。这样器件导通所需的电压就会减少,而当关断时泄漏的电流就会减少。 亚阀值摆幅在过去不算是个大问题,当时芯片运行需要的电压较高。但是现在,亚阀值摆幅开始对我们降低能耗的努力造成干扰。这部分是由于电路设计者希望确保他们的逻辑组件在定义“0”和定义“1”的电流之间有明显区别。晶体管通常的设计是它们处于导通状态时所载的电流是处于关断状态时所泄漏的电流的1万倍。这就意味着要导通一个晶体管,需要至少向它施加240毫伏的电压,即4个十进位的电流,因为每十进位需要60毫伏电压。 在实践中,CMOS电路使用的工作电压通常要高得多,接近1伏。这是因为CMOS中最基础的逻辑电路,即逆变器,采用的是两个串联晶体管。NAND栅极需要3个串联晶体管,这就意味着其需要比逆变器更高的电压。如果要进行调整以应对过程的可变性——意味着需要设置更宽的电压裕度以应对器件与器件的差异——于是就需要如今所看到的接近1伏的电压以确保运行。 这些对电压的需求,加上泄漏的问题,意味着MOSFET微型化正日渐式微,没有出路。如果我们想要进一步降低电压以减少能量消耗,有两个选择(这两个选择都没有什么吸引力):我们可以降低通过器件的电流,这会降低启动速度,从而牺牲了性能;或者,可以保持电流的高水平,同时在关断的时候允许更多电流向器件外泄漏。 这就是可以利用TFET之处。与在MOSFET中提高或降低源极和漏极之间的物理能垒不同,在TFET中我们采用栅极来控制能垒的实际电厚度,从而控制电子通过能垒的可能性。 这个做法的奥妙还是在于p-n结——但进行了一些扭转。在一个TFET中,半导体材料被安置在p-i-n和n-i-p的构形中。其中“i”代表“固有”,意味着沟道拥有和空穴一样多的电子。固有状态与一个半导体所拥有的最大电阻率相对应。它同时提高与沟道内的能带相关的能量,形成一个源极内的电荷载子不太可能穿过的厚能垒。 电子和空穴都遵守量子力学定律,这意味着它们的大小是模糊不定的。当能垒的厚度不到10纳米时,一开始在能垒一侧的电子就不太可能(但并非完全不可能)出现在另一侧。 在TFET中,我们通过在晶体管栅极上施加电压的方式来提高这种可能性。这使得源极内的导带和沟道内的价带重叠,开启了一个隧穿窗口。要注意的是,在一个TFET中,电子在移动至沟道时在导带和价带之间隧穿。这与MOSFET中发生的情况形成鲜明对比。在一个MOSFET中,电子或者空穴主要是在一个带或者另一个带中穿行,一路从源极穿过沟道,最后到达漏极。 由于隧穿机制不是由能垒上的载流子流动所控制的,启动TFET所要求的电压摆幅可以比MOSFET小很多。只需施加足够制造或移动一个使导带和价带交叉或不交叉的重叠的电压足矣。(见插图“关断和导通”。)

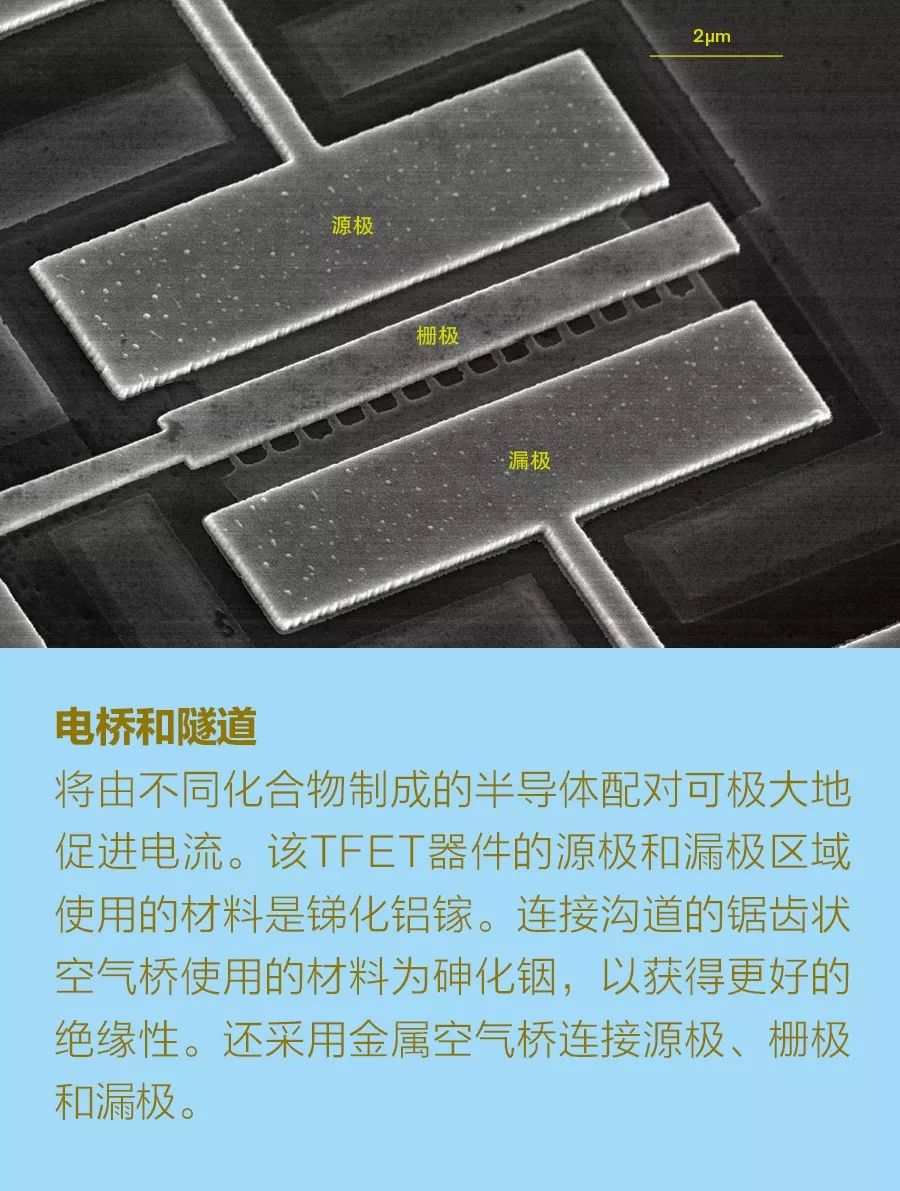

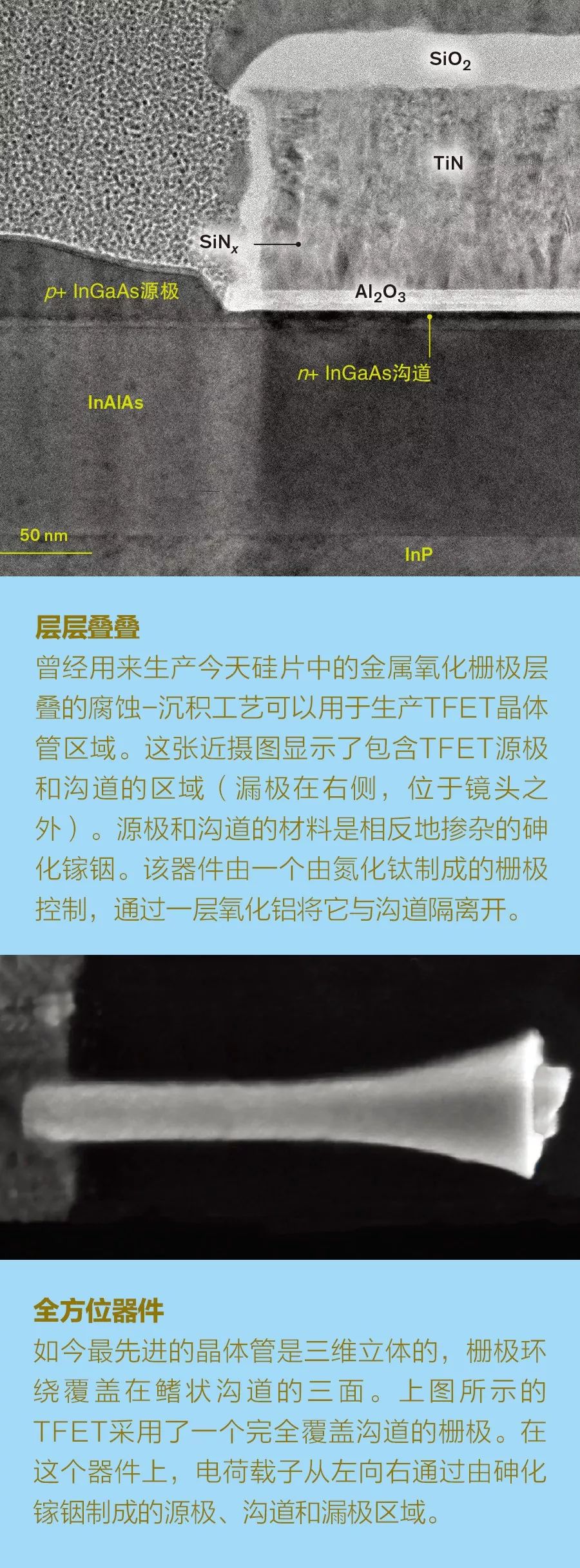

作为一个器件机制,隧穿并不是一个新概念。我们所使用的优盘内的闪存处理器、手机和其他装置都采用了隧穿技术来将氧化阻挡层上的电子注入电荷捕获区域。比如,在TFET中使用的隧穿结也广泛地用于连接多结太阳能电池和触发基于半导体的量子串级激光器。隧穿还控制着电流流过金属半导体触点(这是每个半导体设备的关键部分)的方式。 p-n隧穿结的研究也经历了一段时间。这一概念首先是由诺贝尔奖得主江崎玲于奈在1957年论证并解释的。但是,要让业界认真思考如何将隧穿应用于逻辑,却遇到了一个基本障碍。 直到十多年前才出现首篇关于TFET的论文。当时芯片制造商开始发现计算机的时钟频率失速,同时要应对更加密集、漏电更多的芯片的散热问题。 乔治•阿彭策勒(Joerg Appenzeller)和他IBM的同事们率先论证了低于MOSFET的每十进位60毫伏限制的电流摆幅是可能的。2004年,他们报告说已经制造出来一个隧穿晶体管,它的沟道由碳纳米管制成。其亚阀值摆幅仅为每十进位40毫伏。在几年的时间内,来自加州大学伯克利分校、法国微电子研发机构CEA-LETI、比利时校际微电子中心和斯坦福大学的研究团体也纷纷效仿。他们的研究表明,使用芯片工业最主要的半导体材料硅和锗,即可制造出每十进位消耗量小于60毫伏的开关。 这一成果使业界非常兴奋,因为虽然TFET的电流控制机制对于半导体行业来说是一个新概念,但是这个装置与MOSFET非常相似。它们有相同的基本配置(源极、漏极和栅极),当连上电路时会产生相似的电学特性。半导体设计的基础架构无须改变。 但还是要进行一些改变。研究结果显示,硅和锗对于隧穿来说并不是非常合适。正是出于同样的原因,这些材料无法用于制造出好的光发射器和激光器。硅和锗带有间接能隙,这就意味着为了从一个能带转移到另一个能带,电子还必须从组成该物质的晶格的震荡中吸收一些额外能量。这一额外的障碍显著降低了电荷载子进行跨越的可能性。于是,硅和锗制成的TFET的电荷运载能力跟今天的晶体管相比是微不足道的。 这对业界采用这一技术来说是一个巨大阻碍。不过,将从元素周期表第三行和第五行挑选出来的元素进行混合,可制造出一系列隧穿可能性高得多的直接能隙材料。这些材料尚未应用于逻辑芯片的大规模生产中,但将它们融合进传统的MOSFET中的工作已经在加快进行。在可预见的未来将它们应用于逻辑芯片中的想法,现在看来已经不像之前那样显得过于牵强。 对由III-V族元素制成的TFET的研究近些年也进展飞快。苏曼•达塔(Suman Datta)和他在宾夕法尼亚州立大学的同事在2009年率先对由这些元素制造的TFET进行了论证。他们采用铟、镓和砷的混合物来制造TFET沟道,并随即创造了一项纪录:“导通”的电流高达最好的锗制TFET的50倍。 之后,宾州州立大学的团队和我位于印第安纳州南本徳圣母大学的团队都研制出了产生更高电流的TFET,其原材料是两种化合物的混合体:锑化铝镓和砷化铟。前一种物质的能带可以通过调整铝和镓的比例来上移或下移。这使得我们可以创造出能在两个能带之间自然重叠的隧穿结,意味着导通所需的电压就可以减少。由于能垒可以非常薄——大约就一个单独原子的宽度——更多的电流就可以通过。我们研制的这个器件只需0.5伏的电压就可以良好地运行,能够承载将近200微安的电流通过1毫米宽的沟道,效果可与最先进的MOSFET媲美。

需要注意的是,这些“异质结”TFET的亚阀值摆幅目前都无法击败MOSFET的每十进位60毫伏的限制。许多研究团队努力应对这一挑战。问题的主要症结是半导体和栅氧化层之间接口的电子缺失——许多缺失是由于不固定的化学键造成的。这些缺失会捕获电荷或使电荷无法移动,使得能用于传导的电荷变少。这就意味着我们必须向栅极施加更高的电压,以促进沟道内的电荷载子的活动。 尽管有这个问题,我们还是有理由乐观。位于俄勒冈州希尔斯伯勒的英特尔团队和位于日本札幌的北海道大学的研究团队已经对亚阀值摆幅小于每十进位60毫伏的III-V族元素的TFET进行了论证。英特尔团队的模拟显示,在不对材料进行重大改变的情况下进一步降低亚阀值摆幅是可能的,只须按比例缩小他们已经研制出的晶体管即可。原则上,器件的亚阀值摆幅为每十进位20毫伏左右是可能的;极限状态将根据晶体的热振动来设定。热振动使得导带和价带的边缘不那么锋利。 正如50年以前难以预测MOSFET的极限能力一样,现在要精确预测TFET最终会达到怎样的水平也非常困难。 一个不确定因素是一个TFET在通电时能够承载的最大电流是多少。导通的电流才是决定电路最大速度的最终因素。很长一段时间以来,研究人员一直认为速度不会很快。但是,在2010年,IBM的西屿•库瓦塔(Siyu Koswatta)通过模拟显示,仅施加0.4伏的电压,锑化镓和砷化铟就有可能在每1毫米宽的沟道内承载1.9微安的电流。若可以制造出该器件,则它就可以与MOSFET在高性能应用中进行直接竞争。《国际半导体技术发展蓝图(ITRS)》提出的目标是在0.73伏的电压下每1毫米宽的沟道内承载1.685微安的电流。 我们还需要解决在关断状态下TFET的电流泄漏问题。随着沟道变得越来越短,电子将更加容易直接从源极隧穿到漏极。 器件最终极限的确定取决于若干因素,例如电子结构、缺失,以及性能要求。幸运的是,普渡大学和苏黎世联邦理工学院开发出的计算工具现在已经可以让研究人员模拟出整个器件,包括每一个原子和能带,以预测器件的特性。这对指导试验非常有帮助。 虽然TFET的电子特征看上去前景非常光明,但在开始采用这些晶体管制造芯片之前还必须解决一些实际问题。研究人员一直将主要注意力放在开发n沟道的TFET上,而p沟道的TFET,以及可以将这两种晶体管类型结合起来制造电路的互补加工技术则一直停留在制图版上。 此外,芯片制造商们还必须找出解决变异性问题的方法。随着MOSFET体积的缩小,掺杂物的添加和集中,以及界面的粗糙都会导致电子特性的显著变异。当TFET推出时,其体积很可能比MOSFET还要小。它也不可避免地会遇到这个问题。而对于MOSFET,我们必须想出其他并行方式,例如冗余和纠错,以解决这个问题。 尽管如此,我还是对将来取得更加令人满意的成果的前景持乐观态度。从开发第一个硅制MOSFET到第一个CMOS微处理器的诞生只间隔了10年。到TFET的跨越也许是个更大的挑战,但是凭借着我们对半导体研究了半个多世纪积累下来的经验,这一跨越的实现也许会比我们认为的更快一点。 编辑:黄飞 (责任编辑:admin) |