|

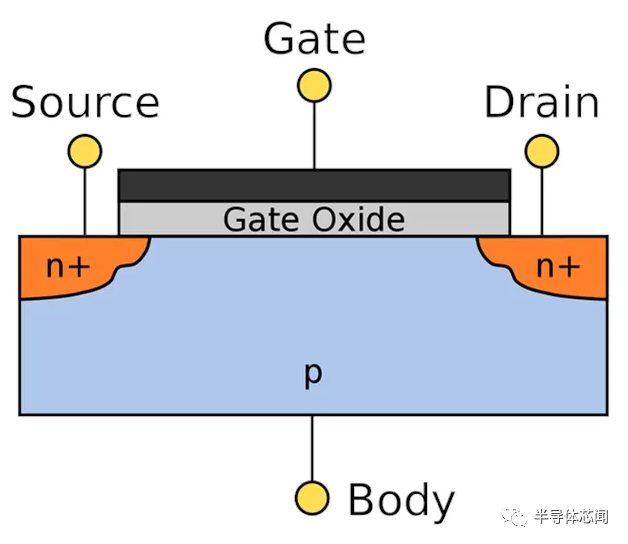

75任何芯片的基本组成部分都是晶体管,它最近迎来了 75岁生日。今天我们将讨论下一个 25 年。 晶体管本质上是电流开关。施加到其“栅极”的电压会导致电流在其“源极”和“漏极”之间的通道中流动。每个晶体管都可以打开或关闭,对应于“1”或“0”。在摩尔定律扩展和 CMOS 工艺技术改进的推动下,现代计算芯片在数十亿甚至万亿的规模上做到了这一点。 理想的晶体管执行以下操作: 开启时传导最大电流量; 关闭时不允许任何电流流动; 尽快切换;

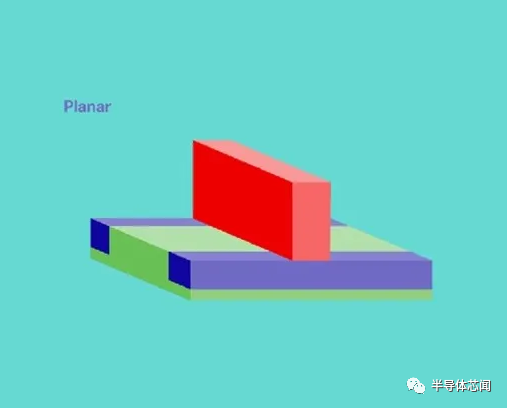

晶体管的三个主要组成部分:“栅极”、“源极”和“漏极”。 晶体管简史 1947 年,约翰·巴丁 (John Bardeen)、威廉·肖克利 (William Shockley) 和沃尔特·布拉顿 (Walter Brattain) 在 AT&T 的贝尔实验室发明了第一批晶体管,称为“平面”晶体管,因为晶体管的所有元件,包括栅极、源极和漏极都位于二维平面上。

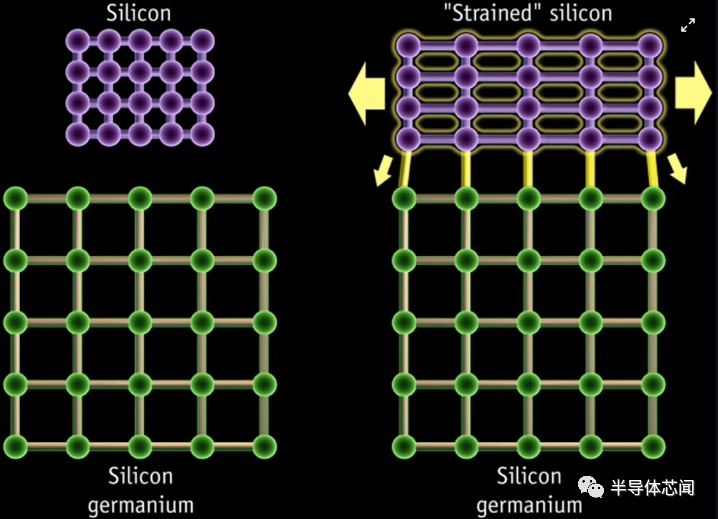

在发展早期,平面晶体管的开关速度可以通过缩短栅极长度来提高。“拉紧”(Straining)硅沟道也会提高开关速度。为了应变沟道(strain channels),将一层硅放置在一层硅锗 (SiGe) 上。由于硅层中的原子与 SiGe 层对齐,这导致硅原子之间的连接拉伸,从而使沟道应变。在这种配置中,硅原子距离更远,干扰电子运动的原子力减少。在应变沟道中,电子迁移率(即电子在被电场牵引时的移动速度)提高了 70%,从而使晶体管开关速度提高了 35%。

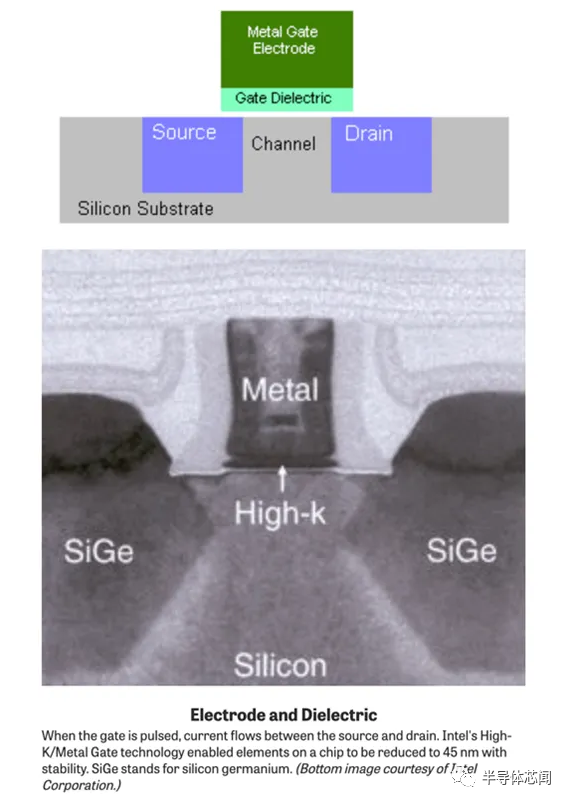

允许继续缩放的进一步发展是“High-K/Metal”门(gate)的开发。在 45nm 节点,栅极电介质开始失去其绝缘(介电)质量并表现出过多的泄漏电流(即,当晶体管处于关断状态时,大量电流会流过晶体管)。 栅极电介质( gate dielectric )是一个非常薄的绝缘层,通常由二氧化硅制成,位于晶体管的金属栅电极和电流流过的沟道之间。英特尔在其 45 纳米工艺(2007 年)中取得重大突破,采用铪基介电层(hafnium-based dielectric)和由替代金属材料组成的栅电极。3 年后,该行业的其他公司也纷纷效仿。由此产生的组合产生了“high dielectric constant”或“High K”栅极。

随着晶体管尺寸的不断减小,源极和漏极之间的空间减小到栅极失去适当控制沟道中电流流动的能力的程度。正因为如此,平面晶体管表现出明显的“短沟道”效应,尤其是在 28nm 节点以下,漏电流过大。

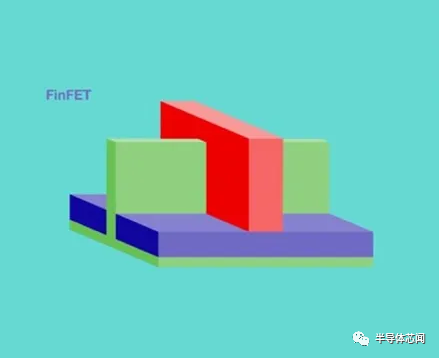

为了应对这一挑战,业界转向“3D”晶体管,即 FinFET。 在 FinFET 中,栅极在硅鳍(silicon fin)的三个侧面环绕沟道,而不是像平面晶体管那样仅在顶部环绕。这样可以更好地控制流过晶体管的电流;FinFET 晶体管的开关时间明显快于平面晶体管。在 2010 年代初期,英特尔开始生产 22 纳米节点的 FinFET,而台积电等代工厂在 3 年后开始生产 16 纳米节点的 FinFET。

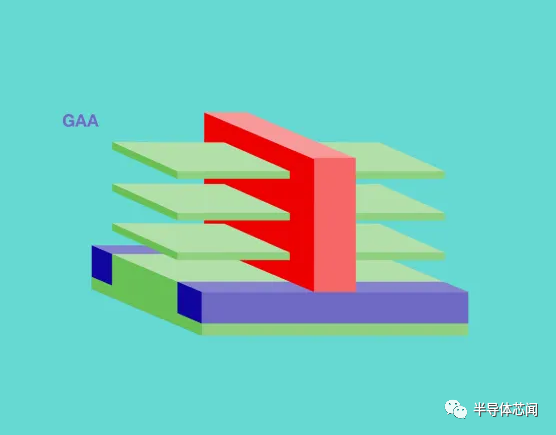

由于可以制造多薄/多高的鳍片以及可以并排放置多少鳍片的限制,晶体管的另一种发展目前正在行业中进行。这些下一代晶体管被称为“Gate-All-Around”晶体管,或GAAFET。GAA 使用堆叠的水平“纳米片”,因此栅极在所有 4 个侧面都围绕着沟道。这进一步增加了晶体管的驱动电流和整体性能。每个纳米片的宽度以及每个晶体管中的纳米片数量都可以变化,从而允许定制设计。 2022年,三星开始在其3nm工艺中使用GAA。由于良率问题,三星3nm GAP的大批量芯片有望在 2024 年实现量产。英特尔的20A工艺节点路线图上有GAA,该工艺节点将于2024年制造就绪,产品将于2025年批量出货。台积电在2025年或2026 年的工艺节点N2有GAA 。这些生产年份是目标,我们认为,这些参与者中至少有2个可能会进一步延迟。

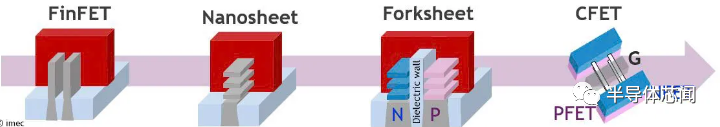

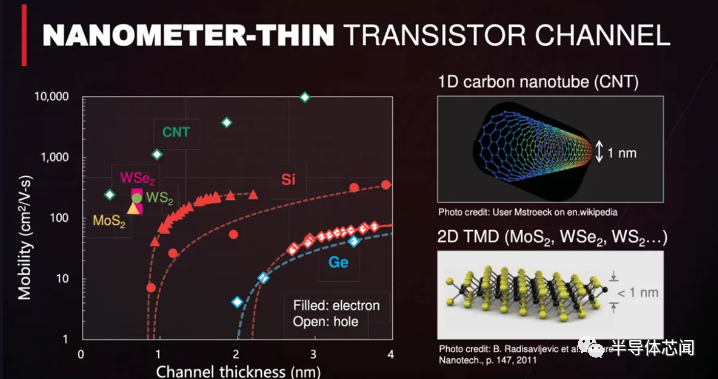

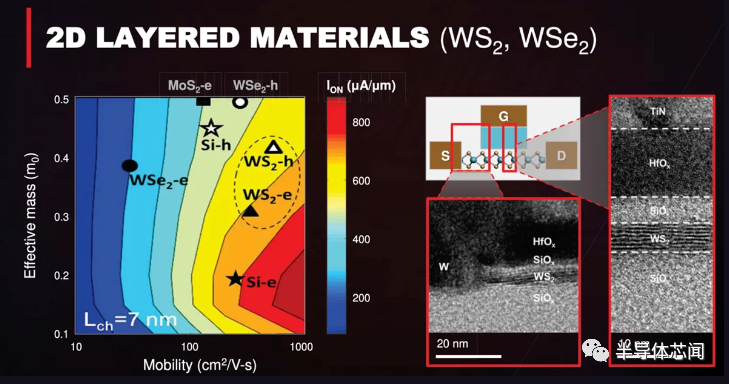

除了最初的 GAA 工艺之外,还包括转向forksheet或3D互补 FET (CFET),其中 n 和 p 沟道移动得更近或垂直堆叠。 为了继续超越2nm的路线图,向 Gate-All-Around 的过渡也将需要用于纳米片的新晶体管沟道材料。这是因为硅和锗等块状材料中的电子迁移率在5nm以下显著下降。随着我们深入到纳米尺度,原子效应不再被忽视。也许应对这些挑战的最佳材料系列是二维材料。 二维材料 二维材料是由单层原子组成的结晶固体,最著名的二维材料是石墨烯,它是一种碳的同素异形体,由排列在六边形晶格中的单层原子组成。但是,需要注意的是石墨烯没有带隙。

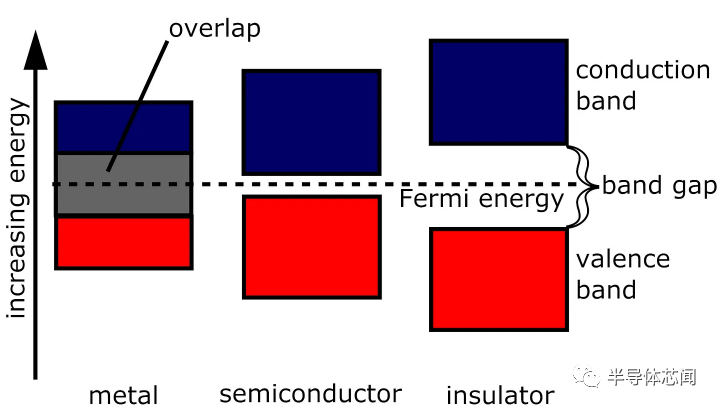

半导体由它们的带隙定义:将卡在价带中的电子激发到它可以导电的导带所需的能量。带隙需要足够大,以便晶体管的开和关状态之间有明显的对比,这样它就可以在不产生错误的情况下处理信息。尽管具有高电子迁移率,但没有带隙,石墨烯不能用作半导体材料。尽管石墨烯在掺杂时具有带隙,但掺杂的石墨烯不允许足够低的关断电流或足够高的导通电流。 用于下一代纳米片的最有前途的二维材料来自“过渡金属二硫化物”或“TMD”子系列。该组中的材料包括二硫化钼 (MoS2)、二硫化钨 (WS2) 和二硒化钨 (WSe2)。TMD 具有 < 5nm 沟道厚度所需的带隙和迁移率。

Philip Wong 在他于 HotChips 2019 主题演讲“What will the next node offer us?”中也强调了这一点。

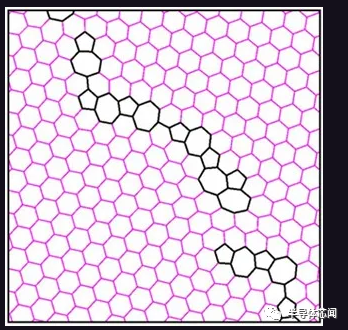

虽然碳纳米管(CNT,一种一维材料)也受到关注,但经过 30 多年的研发,它们的制造难度仍然众所周知。为了实现晶体管应用所需的性能指标,必须生长数百万个单独的管子(即密度)并且所有管子都以相同的方式对齐(即对齐)。此外,对于 CNT,您只需要处理碳。二维材料的用途要广泛得多,指的是一整套材料,而且理论上比碳纳米管更容易制造。可以生长大面积的单层片,然后转移。 二维材料生长 二维材料通常通过化学气相沉积 (CVD) 生长,尽管最近的努力还包括原子层沉积 (ALD)。根据衬底和参数的选择,二维薄膜生长可以是单层或多层。 例如,单层石墨烯(最成熟的二维材料)如今主要通过 CVD 在铜箔或薄膜基板上生长。然而,目前的 CVD 生长技术产生的“多晶”石墨烯在晶格中具有多个晶界。生长也是可变的,这意味着晶圆与晶圆之间的一致性很难实现。由于存在晶界和其他缺陷,CVD 石墨烯固有的电子迁移率通常仍远低于 10,000 cm²/(V⋅s),与载体上原始剥离石墨烯薄片报道的 200,000 cm²/(V⋅s) 值相去甚远。 剥离石墨烯是指从石墨中剥离出来的纯石墨烯薄片;这就是 2004 年曼彻斯特大学的两名研究人员(Andre Geim 和 Kostya Novoselov)使用透明胶带从石墨上剥离石墨烯层时首次分离出石墨烯的方式。 正如您所想象的,当您的材料/晶圆的特性变化如此之大时,计量/检查变得异常困难。

因此,今天的石墨烯电子市场可以忽略不计,一些参与者主要专注于传感器(例如:霍尔效应)或 mems 设备(限制较少的光刻规则/更大的线宽,可以容忍更高的可变性等)。Cardea Bio 和 GrapheneDX 等公司特别致力于石墨烯生物传感器,因为石墨烯具有生物相容性,可以通过场效应传感进行功能化以检测各种分子化合物。欧洲的 Graphenea和Applied Nanolayers等其他公司正在建设专门的石墨烯铸造厂。 像MoS2和WS2这样的TMD甚至更新生,如今通常生长在蓝宝石晶圆上。Aixtron和Oxford Instruments 目前是唯一一家销售二维材料专用生长工具的OEM。要认真对待2D材料,必须开发更一致的晶圆到晶圆生长工艺,以实现长期“单晶”材料的目标。 编辑:黄飞 (责任编辑:admin) |