|

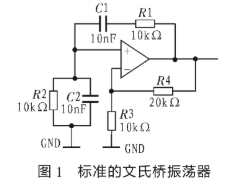

1、引言 在所有低频振荡电路中,文氏桥是最简单的一种,其工作状况几乎不受外部环境变化的影响,很少发生背离设计初衷的情况。即使采用非常普通的标准器件,也能输出非常标准的正弦波,受运算放大器的限制也很小。尽管如此,对文氏桥的理解也不能过于简单,因为设计过于理想化或简单化会导致其性能或结果偏离设计要求。 2、文氏桥振荡器 我们知道,对于一个振荡电路,在给定频率下电路增益大于l、相移为零,并通过反馈网络回馈到输入端。由此,在设计振荡器时首先需要考虑相移,观察图1所示标准文氏桥电路,R1和C1会产生正相移,而R2和C2将产生负相移。在一个特定频率下,R1、C1产生的正相移量与R2、C2产生的负的相移量相等,总相移量为零。在此频率下,电路将可能发生振荡。

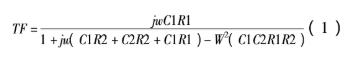

对于图1,考虑到运算放大器的高阻输入和低阻输出特性,可以推导出文氏桥网络(R1、C1和R2、C2)的传输函数:

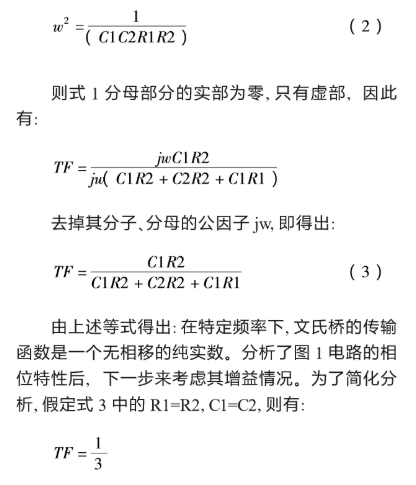

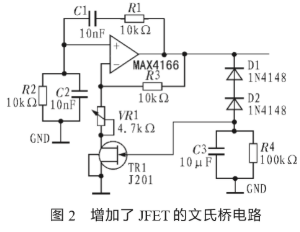

为了满足振荡器的基本条件(零相移,单位增益),运算放大器电路增益必须≥3,以弥补文氏桥电路的衰减。为了运算放大器同相、反相端输入电压一致,从运放输出到输入之间增加一个电阻分压网络,衰减因子为3,以便与文氏桥网络匹配(见图1)。 因此从理论上讲,利用文氏电路产生正弦波非常简便,然而从实际情况考虑实际意义不大,因为电阻的精度很好控制,而电容容值的精度很难控制,即使是精度为±20%的电容成本也很高。比较明智的办法是首先考虑电容器精度对电桥性能的影响,然后找到一种低成本的弥补办法。 表1以一个简单的数据表举例说明文氏桥网络元件参数及其对电路增益的影响。第7行是文氏桥传输函数的结果(式(3)),第12行是由方程式2推导出的工作频率,而第9行是第7行结果的倒数。假定:Cl=C2=10 nF,同时R1=R2=lO kΩ,则电桥将在1.5915494 kHz振荡,因为此时运放的增益为3。如有兴趣,可根据图2参数实际搭建一个实验电路加以验证。需要注意的是,上述电路正常工作的条件是:电容器的精度不能低于额定参数的±10%,否则电路将停振或不能输出正确的频率。譬如,当C1实际参数为8nF(额定值的80%),C2=18nF(额定值的180%)时,振荡器增益应为4.25,即由于电容偏差过大导致3倍增益不足以使电桥发生振荡。相反,当C1偏大、C2偏小时,电桥不需要3倍增益补偿,此时电桥仍会振荡,但会产生失真。偏差越大,失真也越大。不仅如此,此时的振荡频率也不是设计所需的频率。因此一个理想的电路应该是使电桥的参数与运放增益一致,因为,过小增益的电路会停振,而过大增益会引入失真或偏离振荡频率。

为了解决上述问题,在图1电路中插入一个J型FET,见图2,这样可以在小范围内改变运放增益,确保电路的持续振荡条件。上电时,由于场效应管栅极电压为零,因此导通,TRl的RDS为低阻,运放增益此刻大于3,保证电路启振。一旦电路开始振荡,运放有输出信号,整流网络将把一个负电压输入到J型FET的栅极,使其RDS变大或呈高阻。最终结果是运放增益降低,从而使振荡电路进入稳态。输出波形幅度大小取决于两个串联二极管的正向导通电压和提供给J型FET的栅极电压。不幸的是由于工艺问题,J型FET的栅极关断电压与产品批次关系很大,即使是同样电路,不同批次的JFET对应的输出电压变化很大。图2中之所以选择TRl(J201)是因为它的栅极关断电压变化较小,从而保证输出波形变化不大。即便如此,上述电路只能保证电路振荡,并不能保证输出低失真波形,因增加的J型FET只是强迫电路振荡,并不能掩盖电路设计的缺陷。

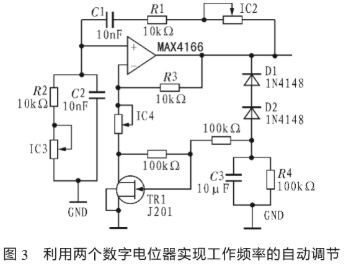

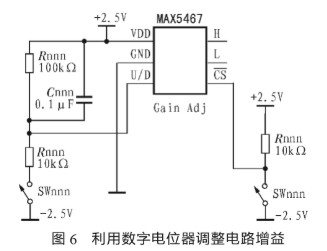

由此可见,除非采用更复杂的电路设计,否则只好在图2电路反馈环路中插入一个可变电阻调整电路增益,以便补偿电桥网络增益,使运放输出低失真的正弦波。设计工程师可能认为增加一个可变电阻十分简单,但它不利于批量生产,生产成本太高。 理想的解决方案是采用电子可调电阻或数字电位器取代或插入到电阻支路。比如用一个低成本、小体积、简单的数字电位器取代图2中的可变电阻VRI,这样可以使电路在批量生产时既便于调整,又使输出波形失真最小。一旦电路启振,利用数字电位器、J型FET可提供一个恰到好处的增益,既保证电路持续振荡,又不会因为增益过大而引起失真。 采用MAX5467 10 kΩ数字电位器取代图2中的VRl。如果把另外两个MAX5467插入到R1、Cl和R2、C2支路,用户就可以很方便地调整电路输出频率。MAX5467的数字控制接口十分简单,甚至无需微处理器干预。 图3中,Rl、Cl和R2、C2支路插入两个10 kΩ数字电位器后,电桥的工频率可以在833 Hz到1.6kHz范围调整。同样,VRl被MAX5467取代后,当IC4改变时,增益也改变,结果输出波形可以是一个直流电压、一个纯正弦波和一个失真的正弦波。

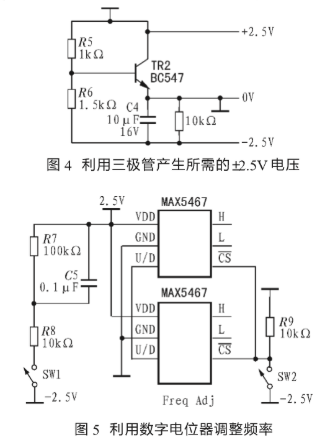

电源电路、频率和增益调整电路分别见图4、图5和图6。利用三极管BC547,可同时得到+2.5V,-2.5V两组输出电压(见图5),为运放和数字电位器供电,三个数字电位器分别为:IC2、IC3、IC4。IC2和IC3占用同样的数字接口,同时改变电阻值(增加或减少)。而增益调整数字电位器IC4的控制是独立的,因此可单独对电路增益进行调整。

本文已对文氏桥振荡器内部关键元件的作用及其对电路的影响进行了详细分析和描述,只有保证电路基本要素正确,才能保证不会由于附加电路导致电路工作失效。通过深入分析电路,文氏桥的性能可以从两方面得以改善。首先必须考虑电容元件的误差,其次通过增加适当的外部电路,比如低成本的数字电位器,改善频率的准确度、降低生产成本。 最后需要注意的是,反馈环路因为器件性能稳定性等因素会在电桥输出引入失真。譬如,二极管的正向导通电压随温度变化会产生漂移(2.1 mV/℃),J型FET的偏置电压也会随温度变化而改变,这些均会对输出电压产生影响。解决上述问题的办法是在输出电路增加一个RMS到DC转换电路或峰值电平检测器。利用它们输出一个与正弦波输出成比例的精确的直流电平信号,再把该信号直接回馈到JFET的输入端,这样就可以使输出正弦波信号更稳定。为了使JFET的线性度更好,可在JFET栅极电路的周边增加两个100 kΩ的电阻,由于这两个电阻在此起负反馈作用,因此可减小JFET的非线性。 3、结束语 从理论上看,文氏桥电路十分简单。然而实际设计时,如果不考虑电容等实际元件的性能,往往会把设计人员引入歧途。通过在电桥三个关键位置插入低成本的数字电位器可以保证电路工作更稳定并便于生产调试。 责任编辑:gt (责任编辑:admin) |