|

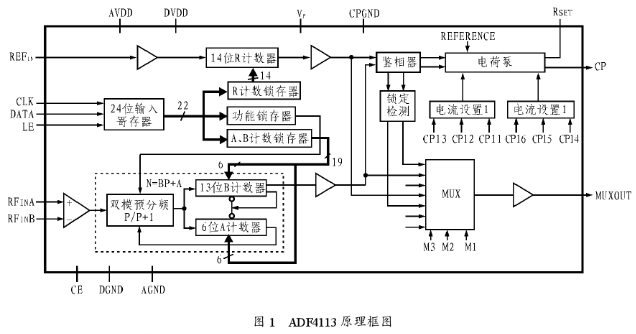

锁相环(phase locked loop)是一种建立在相位负反馈基础之上的闭环控制系统,对相位噪声和杂散具有很好的抑制作用,因此在电视、仪器、通信等许多领域得到了广泛的应用。ADI公司生产的ADF4113的最大RF输入频率可达4GHz,内置可编程预分频器,具有电荷泵电流编程功能,可应用于无线射频通信系统基站和手机、WLAN以及通信检测设备、CATV设备中,是一款性价比很高的电荷泵锁相芯片。 1、主要性能及工作原理 ADF4113可用于无线射频通信系统基站、手机、WLAN、通信检测设备及CATV设备中,其主要性能特点如下: ●工作电压:2.7~5.5V,同时还提供外部可调的电荷泵电压调节功能; ●最高鉴相芯片55MHz,最高RF输入频率达4GHz; ●具有四组可编程双模分频器8/9、16/19、32/33、64/65; ●内置可编程电荷泵电流和可编程反冲(antibacklash)脉宽功能; ●编程控制采用3线串行接口; ●能够进行模拟和数字锁定检测; ●软硬件断电模式; ●具有良好的相位噪声参数,鉴相频率为200kHz 时,相噪基底为-164dBc/Hz;输出900MHz 时,相噪可达-91dBc/Hz@1kHz;输出1960MHz时相噪为-85 dBc/Hz@1kHz;鉴相频率1MHz、输出3100MHz时相噪为-86 dBc/Hz@1kHz。 图1所示为ADF4113的原理框图,它由一个低噪声数字鉴相器、一个高精度电荷泵、一个可编程参考分频器(R分频器)、一个可编程A、B计数器以及一个双模分频器(P/P+1)组成。6位A计数器、13位B计数器与双模分频器(P/P+1)共同组成了N分频器,分频比N=BP+A。只需外加一个环路滤波器和压控振荡器(VCO),就可以构成一个完整的锁相环电路。输出频率为:fVCO=N(fREF/R),其中,fREF为参考频率,频率步进等于fREF/R。

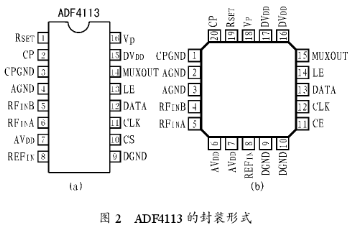

2、引脚功能

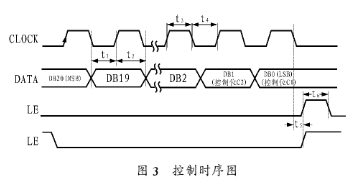

ADF4113有TSSOP和LFCSP两种封装形式,引脚排列如图2所示。各引脚功能如下: RSET:用来设置最大电荷泵输出电流,外接一个电阻RSET并连接至CPGND,换算关系为:ICPmax=23.5/RSET(Ma); CP:电荷泵输出,接环路滤波器; CPGND:电荷泵地; AGND:模拟地; RFINB:RF互补输入,一般接一个100pF的去耦电容; RFINA:RF输入(来自VCO的RF信号耦合输入); AVDD:模拟电源,电压范围为:2.7~5.5V;去耦电容应尽量靠近该引脚;AVDD必须和DVDD一致; REFIN:参考晶振输入; DGND:数字地; CE:芯片使能端,逻辑“1”有效; CLK:串行时钟输入端,在每个CLK的上升沿,串行数据锁入寄存器; DATA:串行数据输入端,首先装入的是最高有效位MSB,控制位在最低两位设置; LE:加载使能,该位为逻辑“1”时,存储在24位移位寄存器中的数据将全部装入指定的锁存器中,锁存器的选择由控制位来决定; MUXOUT:模拟或数字锁定检测端; DVDD:数字电源,2.7~5.5V,去耦电容应尽量靠近该引脚;DVDD大小必须和AVDD一致; VP:电荷泵电源,应大于或等于VDD,最高可到6V。 3、编程控制 ADF4113的数字部分包括一个24位输入移位寄存器、一个14位R计数器和一个19位N计数器(含A、B计数器)。图3给出了数据输入的时序图。数据(DATA)在每个时钟(CLK)的上升沿从MSB(最高有效位)开始依次写入24位移位寄存器中,直到LSB位写入完成之后,由来自LE的上升沿将存储在24位移位寄存器中的数据一次性锁存入目标寄存器(包括R计数锁存器、N计数锁存器、功能锁存器以及初始化锁存器),接着再进行下一个目标寄存器的初始化工作。目标寄存器的选择由移位寄存器中的最末两位DB1、DB0来决定。

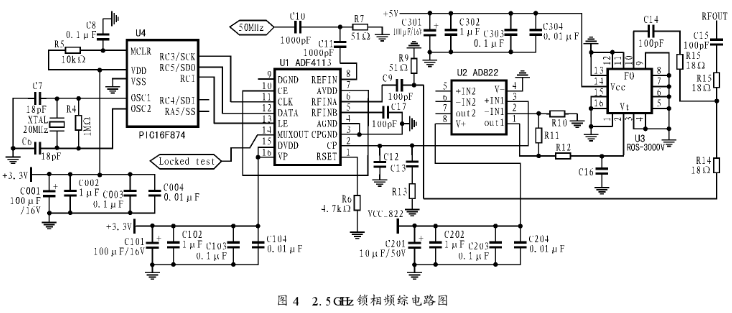

4、应用电路

图4是利用ADF4113设计的2.5GHz锁相环电路,其中单片机选用Microchip公司的PIC16F874,串行数据采用SPI方式写入;VCO选用Mini公司的ROS-3000V。芯片使能端CE直接与电源连接,鉴相频率fPD取25MHz,50MHz参考晶振从REFIN输入,因此参考分频比R=2;VCO分两路输出,一路作为频综输出,另外一路输出至ADF4113的RFINA端,经N分频后与来自R分频器的参考频率进行鉴相并产生一个误差信号,该误差信号从CP输出经有源三阶环路滤波后驱动VCO,最终锁定在2.5GHz的频点上。调整环路滤波电路中的电阻和电容可以改变环路参数,阻尼系数ζ一般取0.707。这里分频比N=2500MHz/25MHz=100,P取16,由N=BP+A得B=6,A=4。4个24位锁存器的初始化设置如下: FUNCTION锁存器:0101 1111 1000 0000 1001 0010; INITIALIZATION锁存器:0101 1111 1000 0000 1001 0011; R计数锁存器: 0000 0000 0000 0000 0000 1000; AB计数锁存器:0000 0000 0000 0110 0001 0001。 最后测得电路在2.5GHz输出时的相位噪声为-93dBc/Hz@5kHz,测试频谱如图5所示。

责任编辑:gt (责任编辑:admin) |