Protel转换至Allegro及CCT格式的简便方法

由于接触和使用较早等原因,国内Prote用户为数众多,他们在选择Cadence高速PCB解决方案同时,都面临着如何将手头Protul设计移植到Cadwe PCB设计软件中问题。在这个过程当中碰到问题大致可分为两种;一是设计不很复杂。设计师只想借助Cadenca CCT强大自动布线功能完成布线工作;二是设计复杂,设计师需要借助信噪分析工具来对设计进行信噪仿真。设置线网布线拓扑结构等工作。

对于第一种情况。要做转化工作比较简单,可以使用Pro曲或h上一提供Protul到CCT转换工具来完成这一工作、对于第二种情况,要做工作相对复杂一些。下面将这种转化方法作一简单介绍。

Cadwe信噪分析工具分析对象是Cadence All6erobrd文件,而Allegro可以读入合乎其要求第三方网表。Protel输出eleds格式网表满足Allesro对第三方网表要求,这样就可以将Protel文件注入Allesro。这里有两点请读者注意。首先,Allesro第三方网表在$PACKAGE段不允许有“”;其次, Allegfo第三方网表中总线中一根信号表示形式为Bas NameX。读者可以通过直接修改Protel输出Teleds网表方法解决这些问题。

Allegro在注入第三方网表时还需要$#F类型器件设备描述文件DeviCetxt文件。它格式如下;

Package;gkBge tyIXi

Class Caatyy

Plllcount;total pinnamber

其中常用是PACKAGE,CLASS,PINCOUNT这几项O PACKAGEha了器件封装,但Alleqro$1ii入网表时会用网表中PACKAGE项而忽略设备描述文件中这一项。CLASS确定器件类型。以便信噪分折。Cadffi将器件分为IC,IO。DISCRETE三类O PINCOUNT说明器件管脚数目。对于大多数器件。eMtri文件中包含有这三项就足够了。有了第三方网表和设备描述文件。我们就可以将Protel中原理图设计以网表形式代入到Cadence PCB设计软件中,接下来,设计师就可以借助CadChce PCB软件在高速高密度PCB设计方面强大功能完成自己设比。

如果已经在Protel作了PCB布局工作,AllesroSCflpt功能可以将pYOtCI中布局在AlloptO中重现出来。在 Protel中。设计师可以输出一个Place&PICk文件,这个文件中包含了每个器件位置、旋转角度和放在PCB顶层还是底层等信息。可以通过这个文件很方便生成一个M吨roscriPt文件,在Allegro中执行这个scriPt就能够重现Protel中布局了。

此

相关热词:#Protel转换至A #电子电路图

电感器设计流程和见解

电感器设计流程和见解

时间:2026-05-01

什么是触发器?触发器的作用是什么?

什么是触发器?触发器的作用是什么?

时间:2026-05-01

什么是电源?电源是如何进行分类的?

什么是电源?电源是如何进行分类的?

时间:2026-05-01

电驱动NVH的特点和结构

电驱动NVH的特点和结构

时间:2026-05-01

什么是霍尔传感器?

什么是霍尔传感器?

时间:2026-05-01

电负性的计算方法

电负性的计算方法

时间:2026-04-30

电导的定义_电导的单位_电导怎么算

电导的定义_电导的单位_电导怎么算

时间:2026-04-30

什么是计数器_计数器的作用

什么是计数器_计数器的作用

时间:2026-04-30

什么是欧姆定律_欧姆定律公式

什么是欧姆定律_欧姆定律公式

时间:2026-04-30

RAID是什么?RAID有哪些?

RAID是什么?RAID有哪些?

时间:2026-04-30

电阻的原理和作用 电阻色环识别图 电路中电...

电阻的原理和作用 电阻色环识别图 电路中电...

时间:2026-03-09

NVIDIA CPU+GPU超级芯片大升级!

NVIDIA CPU+GPU超级芯片大升级!

时间:2026-03-09

什么是室温超导?半导体时代将走向结束?芯...

什么是室温超导?半导体时代将走向结束?芯...

时间:2026-03-09

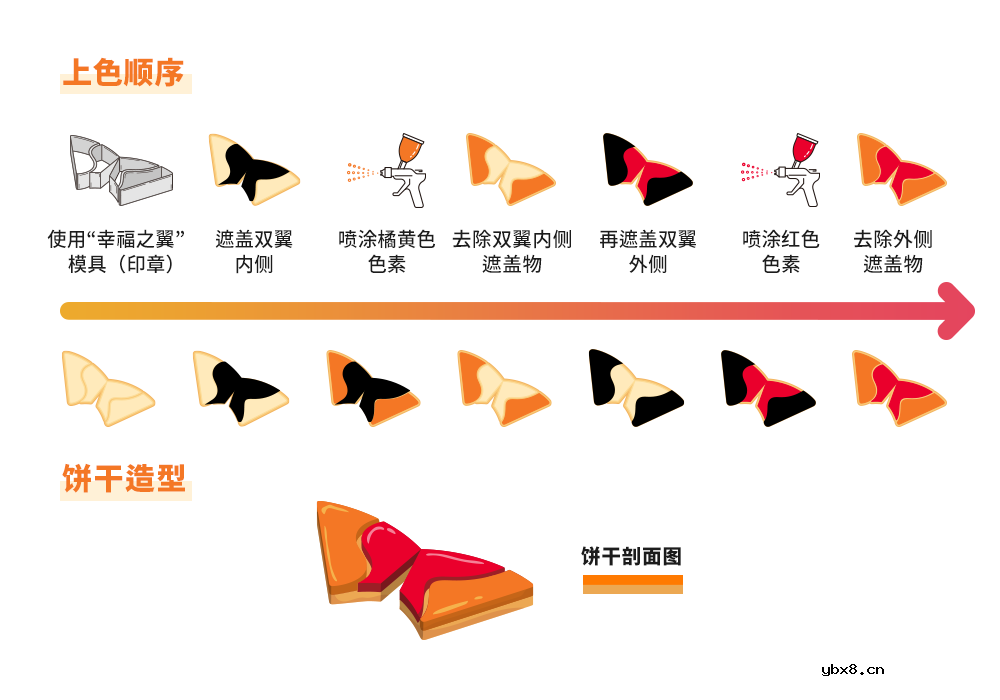

半导体光刻工艺 光刻—半导体电路的绘制

半导体光刻工艺 光刻—半导体电路的绘制

时间:2026-03-09

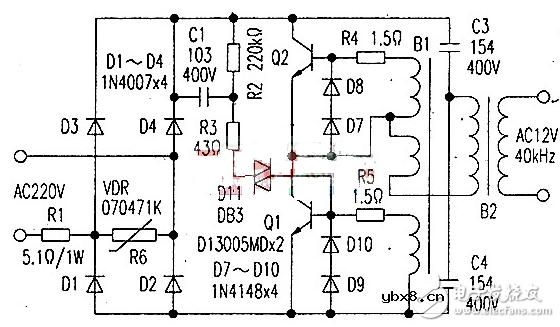

石英灯电子变压器电路原理

石英灯电子变压器电路原理

时间:2026-03-06

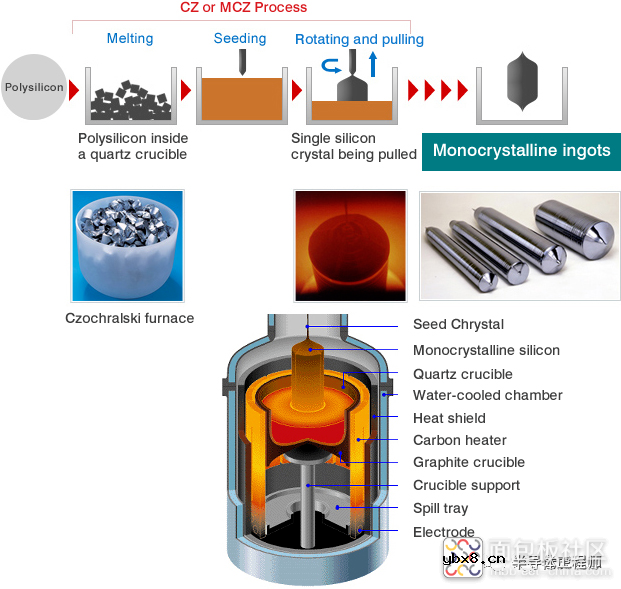

什么是硅片或者晶圆?一文了解半导体硅晶圆

什么是硅片或者晶圆?一文了解半导体硅晶圆

时间:2026-03-09

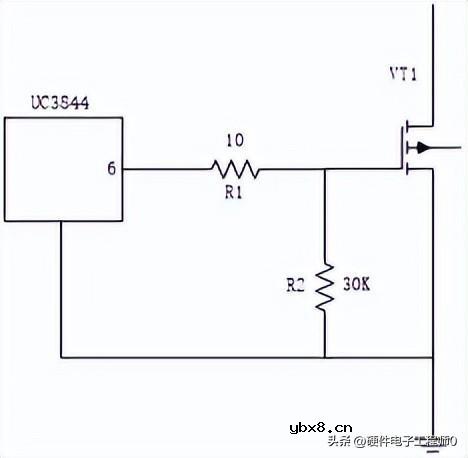

一文详解MOS管驱动电路拓扑的设计

一文详解MOS管驱动电路拓扑的设计

时间:2026-03-09

汽车芯片业应汲取的教训

汽车芯片业应汲取的教训

时间:2026-03-09

压敏电阻型号的含义

压敏电阻型号的含义

时间:2026-03-05

半导体行业之ICT技术简介

半导体行业之ICT技术简介

时间:2026-03-09