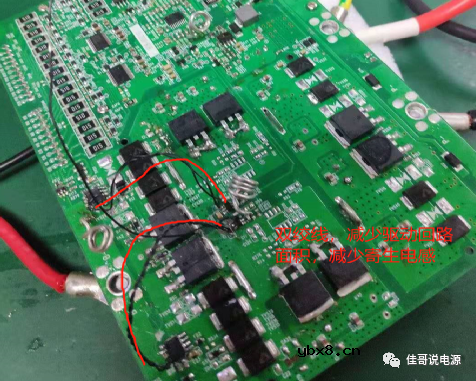

下图是一款DCDC电源初样,测试时发现上电,或带大载时出现炸机,示波器测试驱动IC输入端

波形,发现严重振荡,检查PCBlayout,发现驱动走线回路与功率回路出现交叉,且由于考虑到

过认证,打静电和EFT,使得GPS MCU等数字地线和驱动地线,选通IC地都接到电池地 ,按照通常的反激电源

layout经验走线 使得选通IC到驱动IC走线环路面积非常大;后割断原来走线,用双绞线代替原来走线,

再也没出现炸机情况

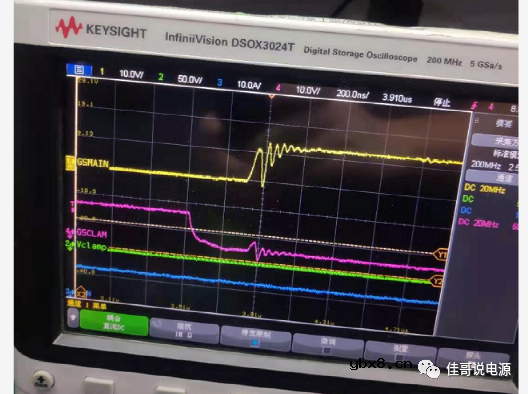

下面从理论简易分析为什么减少回路面积可以减少驱动振荡?

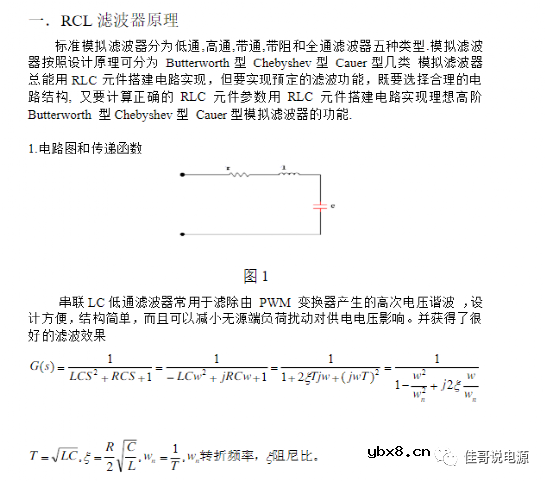

MOS驱动回路可等效为RCL二阶振荡模型

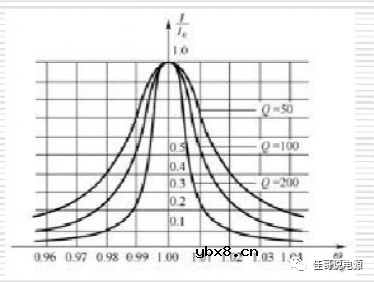

对于一定开关频率,减小Q值,则可以减少振荡时电压幅值,如何减少Q值?

1、减少L 2、增大C 3、增大R 在后续仿真加以验证

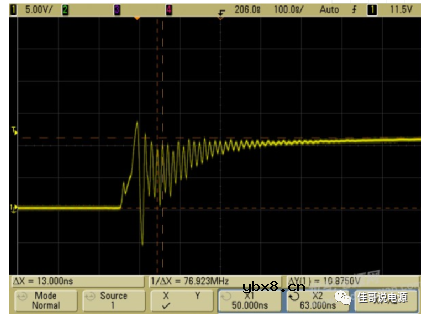

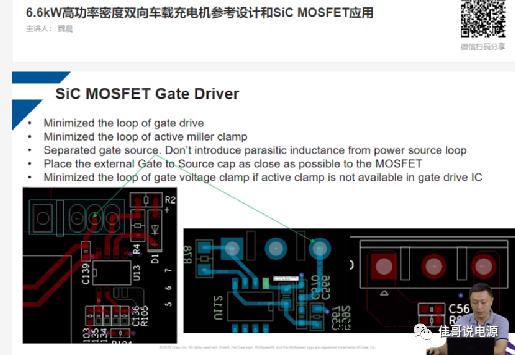

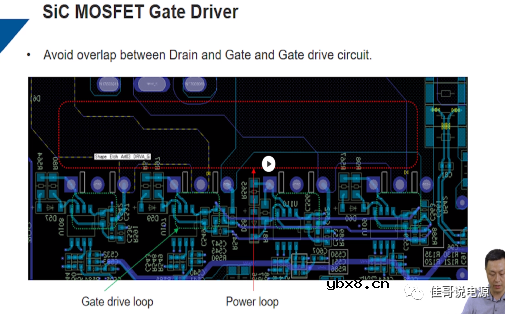

驱动电路PCBlayout要点:

1、避免驱动回路与功率回路重叠,

一方面重叠会增加功率回路与驱动

回路寄生耦合电容面积,另一方面增加了

耦合磁路面积

2、减少驱动回路面积;就近GS放置电容;分离

驱动回路source极和功率回路source极

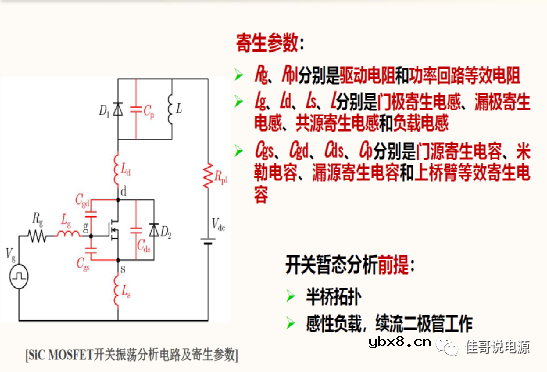

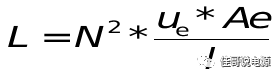

如何减少寄生电感?

L:自感感量

N:电感匝数

:相对磁导率

Ae:磁路等效截面积

u:磁导率

l:磁路等效路径长度

由上述电感计算公式可知:减少寄生电感方法有 (对于驱动回路匝数N为1)

1:减少相对磁导率

2:减少回路面积

3:增加磁路长度

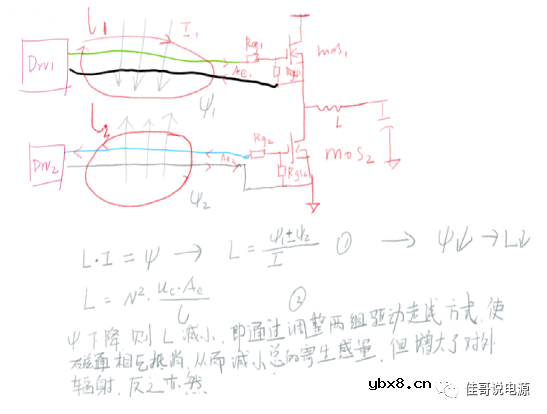

在实际PCB Layout中 ,驱动电路通过差分对走线的方式减少驱动回路面积

如下图,则可通过走差分对尽量的形式,减少驱动回路Ae面积,同时驱动IC的地线与MOS管source极直接相连

另外对于半桥而言DRV1与DRV2驱动时序刚好相差180度,也即磁通方向刚好反向可运用空间耦合方式减少等效磁导率从而减小寄生电感,反之可以降低对外辐射。

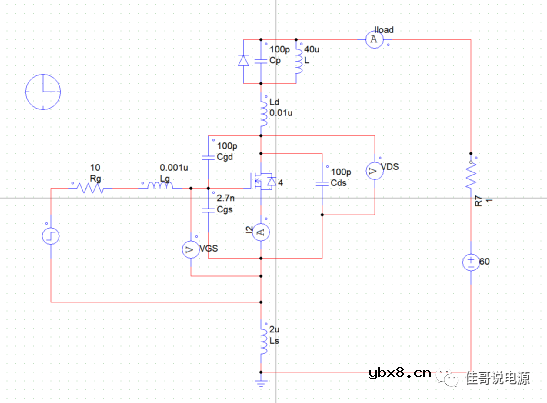

仿真原理图如下 软件平台:PSIM 9.04

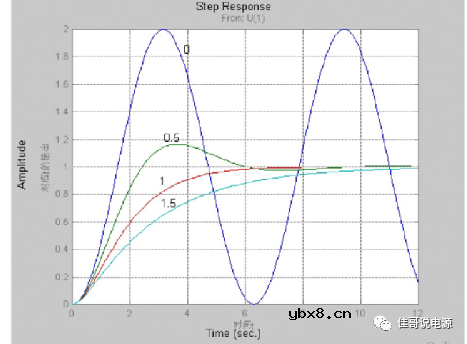

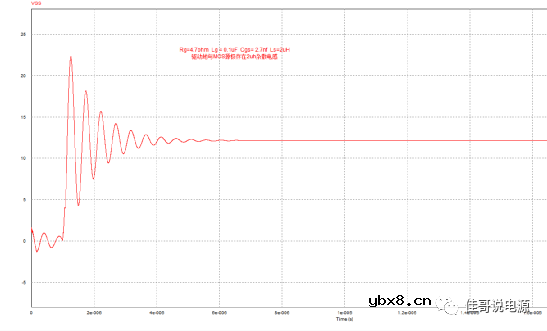

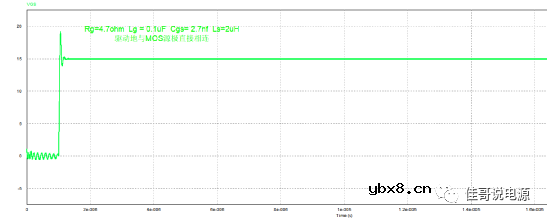

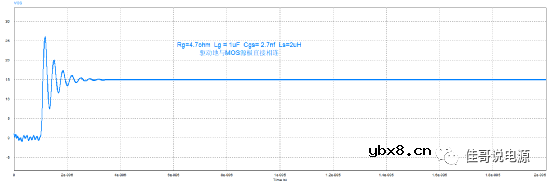

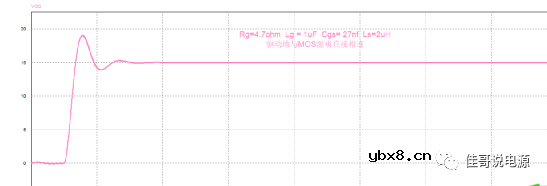

实际仿真

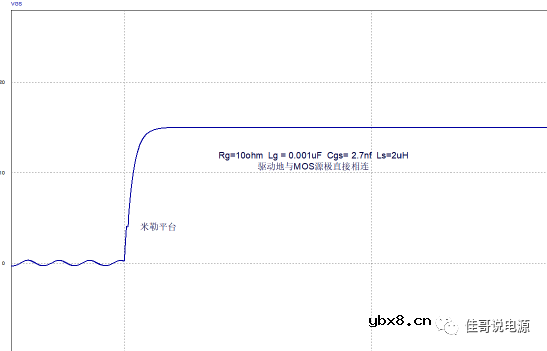

与图一相比,只是将驱动的source与mos的source直接相连,振荡明显减小

与图二相比,将驱动回路杂散电感由0.1uH增大到1uH,振荡加剧

与图三相比,增加GS电容到27nf,振荡减小

将Rg增大到10ohm,驱动回路寄生电感减少到0.001uH后,振荡消失

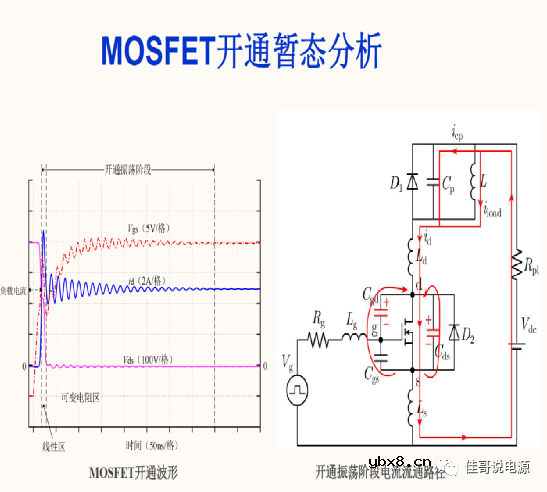

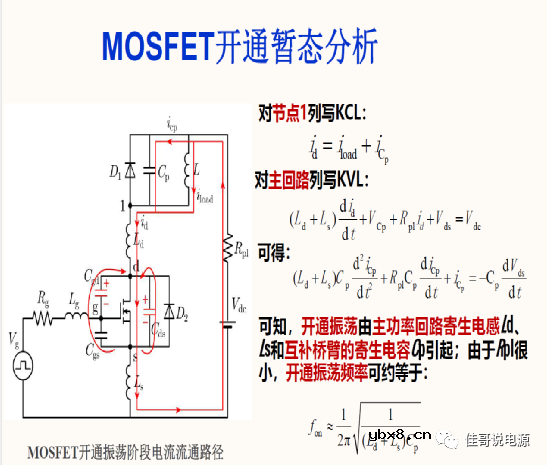

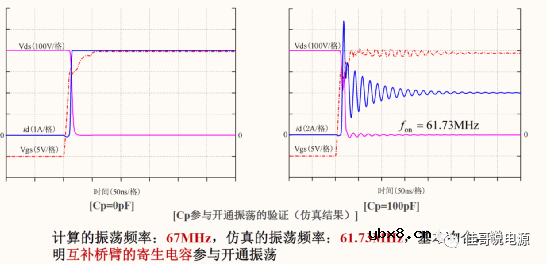

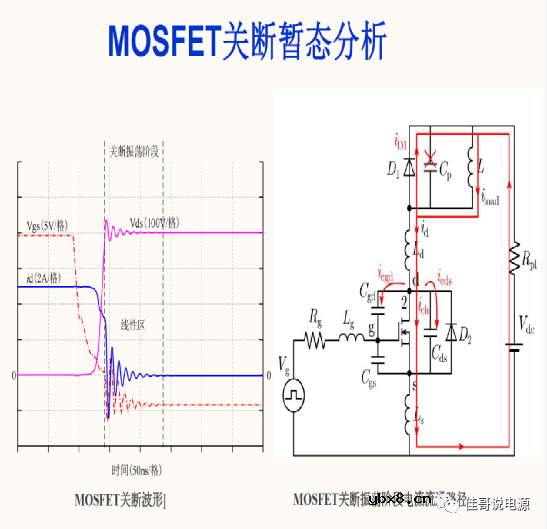

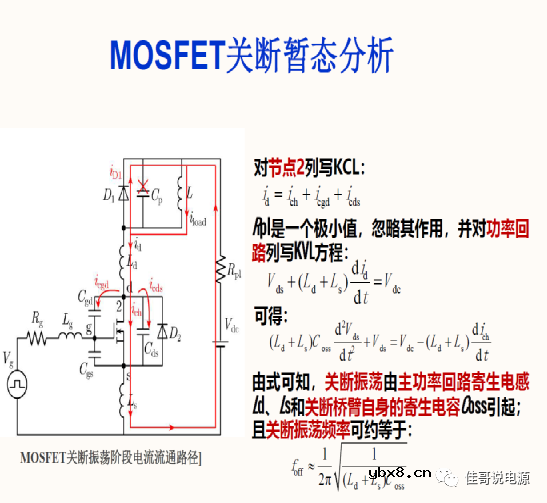

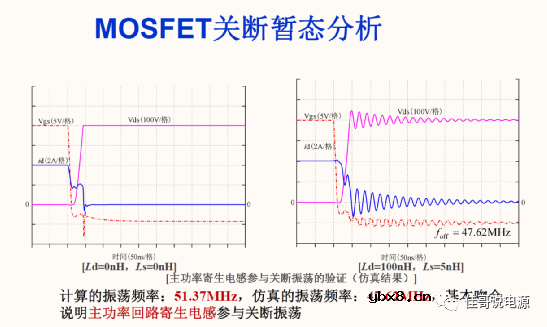

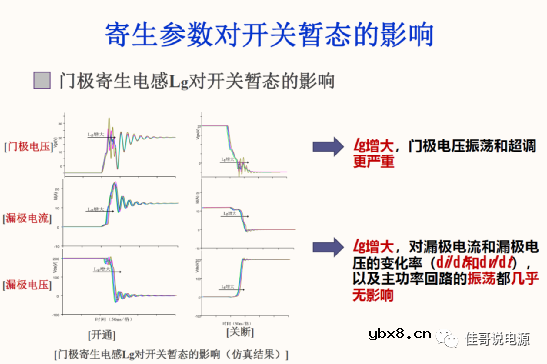

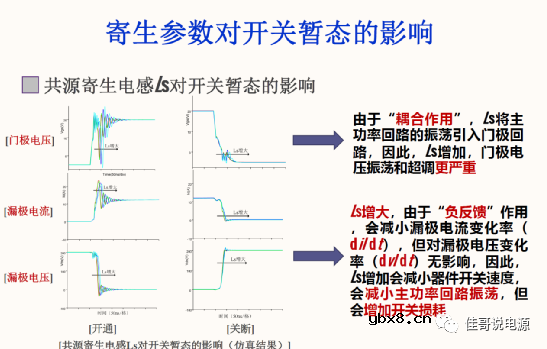

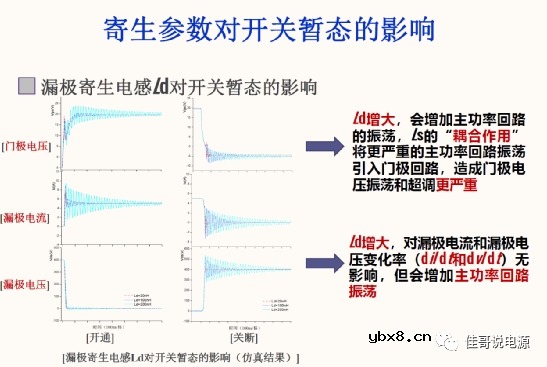

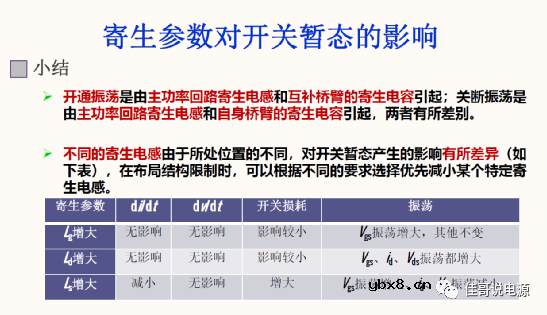

MOSFET开关暂态分析

什么是PCA?何时应该使用PCA?

什么是PCA?何时应该使用PCA?

时间:2026-04-28

仪表放大器放大倍数分析

仪表放大器放大倍数分析

时间:2026-04-28

射频微波设计入门

射频微波设计入门

时间:2026-04-28

变压器结构

变压器结构

时间:2026-04-28

8种进行简单线性回归的方法分析与讨论

8种进行简单线性回归的方法分析与讨论

时间:2026-04-28

什么是RS485通信接口

什么是RS485通信接口

时间:2026-04-28

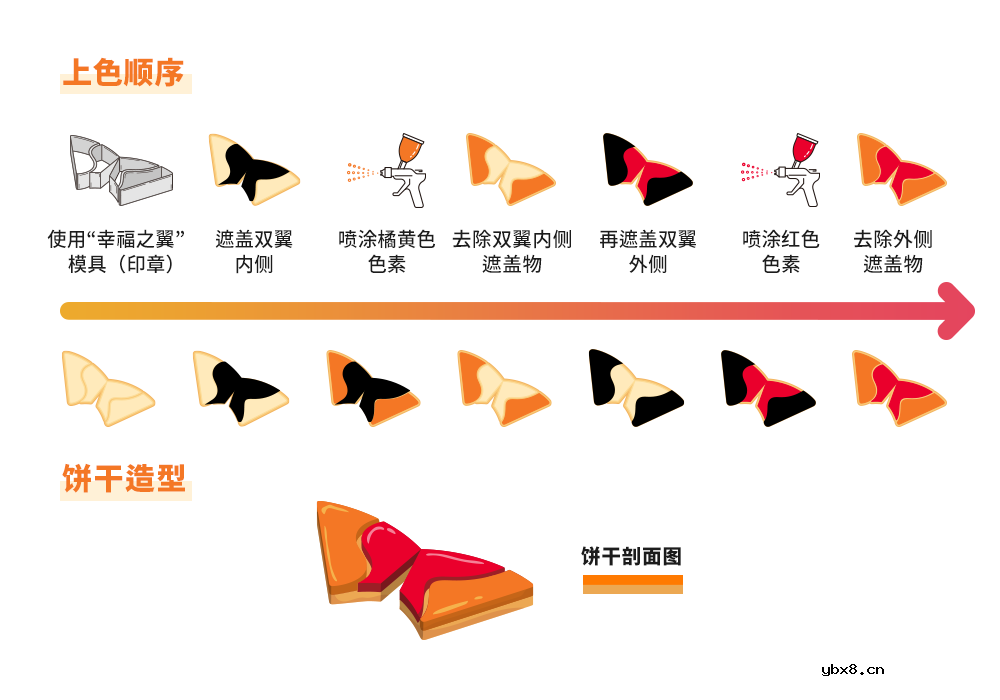

简单的上色装置

简单的上色装置

时间:2026-04-26

液晶屏对比度温度补偿

液晶屏对比度温度补偿

时间:2026-04-26

双输入视频多路复用的电缆驱动器

双输入视频多路复用的电缆驱动器

时间:2026-04-26

带有75Ω负载的抗阻匹配线路驱动器

带有75Ω负载的抗阻匹配线路驱动器

时间:2026-04-26

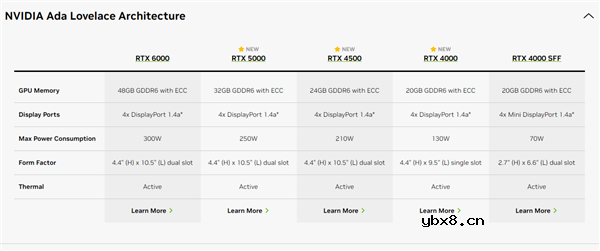

NVIDIA CPU+GPU超级芯片大升级!

NVIDIA CPU+GPU超级芯片大升级!

时间:2026-03-09

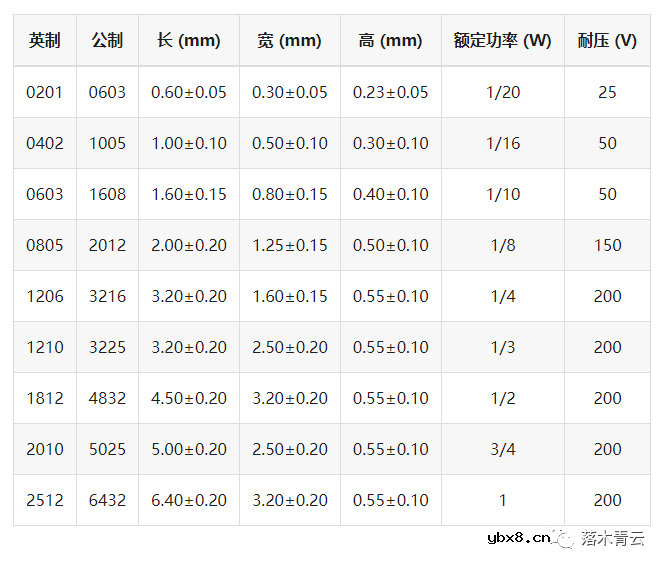

电阻的原理和作用 电阻色环识别图 电路中电...

电阻的原理和作用 电阻色环识别图 电路中电...

时间:2026-03-09

什么是室温超导?半导体时代将走向结束?芯...

什么是室温超导?半导体时代将走向结束?芯...

时间:2026-03-09

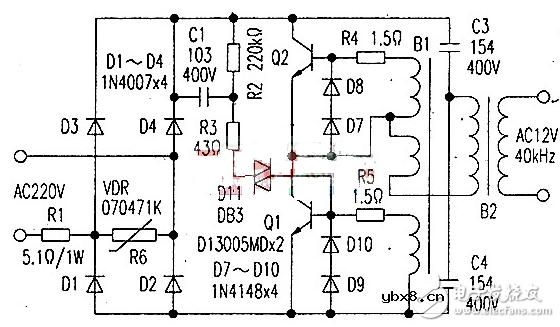

石英灯电子变压器电路原理

石英灯电子变压器电路原理

时间:2026-03-06

半导体光刻工艺 光刻—半导体电路的绘制

半导体光刻工艺 光刻—半导体电路的绘制

时间:2026-03-09

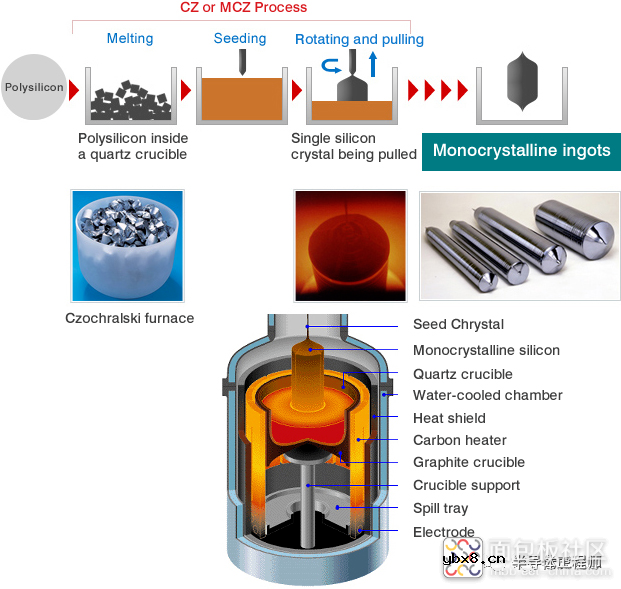

什么是硅片或者晶圆?一文了解半导体硅晶圆

什么是硅片或者晶圆?一文了解半导体硅晶圆

时间:2026-03-09

汽车芯片业应汲取的教训

汽车芯片业应汲取的教训

时间:2026-03-09

半导体行业之ICT技术简介

半导体行业之ICT技术简介

时间:2026-03-09

压敏电阻有正负极吗

压敏电阻有正负极吗

时间:2026-03-05

实用模拟电路小常识浅析

实用模拟电路小常识浅析

时间:2026-03-09