|

本文使用DDR SDRAM作为存储单元,在不改变系统时钟的情况下,利用时钟双沿传输数据,将同频率芯片的传输带宽在SDRAM基础上提高了一倍,很好地满足了高带宽缓存的需要。

1 DDR存储器简介

DDR存储器即双数据率同步动态随机访问存储器,它和早期的单数据率同步动态随机访问存储器一样,内部存储单元采用电容充电来保存数据,因此必须不断地对电容充电以保持数据,这就是所谓的“刷新”。SDRAM的数据总线在每个时钟的上升沿存取数据,而DDR SDRAM则在每个时钟的上升沿和下降沿都存取数据,这样在数据总线宽度和时钟频率不变的条件下数据总线带宽得到了一倍的提升。

2 系统设计

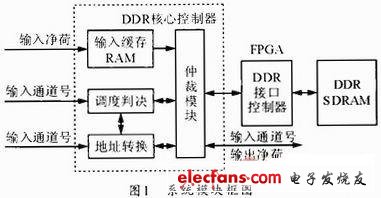

设计采用Xilinx公司的Sptan3a-dsp 1800a作为主控制器,使用Micron公司的MT64V32X16芯片作为存储介质,最大存储容量为512M。本系统的逻辑部分由仲裁模块、输入缓存模块、调度判决模块、地址转换模块和DDR接口控制模块等部分组成,结构框图如图1所示。

核心控制器中的仲裁模块产生相应的控制命令。完成上电后的初始化复位,并在系统运行过程中,针对工作优先级,发出刷新指令、写操作指令和读操作指令;DDR接口控制模块根据DDR芯片操作的基本时序,实现核心控制器指令的针对物理芯片的信息传输;南于DDR芯片具有不可实时操作特性,必须使用内部输入缓存RAM进行基本的实时数据缓冲;而地址转换模块、调度判决模块则和内部输入缓存RAM配合,完成对DDR芯片内部存储空间的映射工作。

3 DDR核心控制器设计

DDR存储器是一种指令相对复杂的高速存储芯片,它在上电后必须完成初始化才能进行其它操作;而且不支持单周期读写操作,只支持周期为2、4、8突发读写操作。另外,DDR芯片由于其电容特性,数据保存在其中是不稳定的,需要在一定时间周期内对其进行刷新操作,以保证数据不会丢失,因此,在DDR操作过程中有数十条指令。但在本设计中DDR接口控制器采用的是Xilinx提供的DDR IP,这样核心控制器中的仲裁模块只需要使用空闲、初始化、读操作和写操作等4个指令就可以完成对DDR-SDRAM的操作,大大降低了设计难度。由于设计目的在于消除来自网络对IP数据的抖动,并且最终要将IP数据分发至512个通道,大大超出了以往设计对DDR的使用需求,因此本文在这里提出图1所示设计,即可完成DDR存储器对高速大容量多通道的设计应用:

(1)输入缓存模块

输入缓存器由一个RAM加外部逻辑电路构成,缓冲已输入但还没来得及写到DDR中的TS分组净荷。待仲裁模块发出允许写入的信号后,再将输入缓存中的数据包传递给仲裁模块,并且释放相应的存储空间。根据DDR的工作模式和DVB-C特性,输入缓存的数据传输以TS包为单位,实现192个字节连续突发传输。

(2)调度判决模块

调度判决模块接收读请求队列信息,实现读数据时将同一个bank内数据量最大的FIFO进行调度出队列的判决。该模块保存各个通道FIFO当前的数据包数量。

(3)地址转换模块

地址转换模块负责实现通道号和DDR SDRAM芯片内部存储空间的映射。该模块中保存的变量包括各个通道在DDR SDRAM中的块起始地址、块终止地址、FIFO头偏移量、FIFO尾偏移量。

(4)仲裁模块

仲裁模块产生相应控制命令,针对工作优先级,发出空闲指令、初始化指令、写操作指令和读操作指令。 (责任编辑:admin) |