|

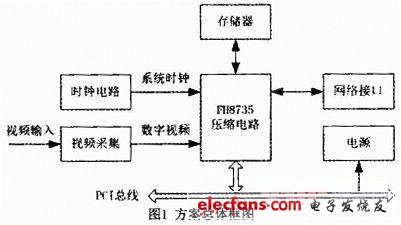

本文提出了一种基于FH8735视音频编码器的高分辨率图形图像压缩方案,可完成视频的采集、压缩,及将压缩后的视频数据通过PCI总线发送到主机存储,或通过以太网络接口输出以实现远端实时监控。

1 总体设计

基于FH8735视音频编码器的高分辨率图形图像压缩方案由采集电路、时钟电路、FH8735压缩电路、网络接口和电源电路等组成。方案总体框图如图1所示。

图1内各部分电路介绍如下:

(1)视频采集电路。由输入匹配和视频采集电路组成,完成高分辨率视频的采集;

(2)时钟电路。由高性能晶振组成,为视频采集电路和FH8735提供稳定的时钟;

(3)FH8735压缩电路。由FH8735音视频编码器、DDR存储器组成,完成视频的压缩处理,并提供PCI接口和网络接口控制;

(4)网络接口。外置PHY芯片,提供以太网接口;

(5)电源电路。为各功能电路提供所需电源。

2 主要设计

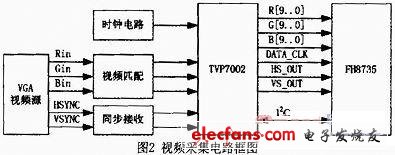

2.1 视频采集电路

视频采集电路以TI公司视频图像解码器TVP7002为核心组成,TVP7002作为一款高性能的视频图像解码器,具有以下一些主要功能和性能特点:

(1)DC精度:8/10位;

(2)模拟增益范围:-6~6dB;

(3)输入分量视频信号分辨率:480i/576i~1080p;

(4)输入图形信号分辨率:VGA~UXGA;

(5)数字视频输出格式:YCbCr 4:2:2及RGB/YCbCr 4:4:4;

(6)I2C总线接口。

以视频图像解码器TVP7002为核心组成的视频采集电路设计如图2所示:

VGA视频输入后,经过信号匹配与滤波,即可接入TVP7002解码器。TVP7002解码器的工作状态由FH8735视音频编码器通过I2C总线根据信号特性和处理要求设置。

2.2 FH8735视频压缩

FH8735是富瀚微电子公司开发的一款高性能的音视频编码芯片,其主要技术特点如下:

(1)编码标准:ITU-T rrcommendation H.264 ISO/IEC 14496-10 advanced video coding standard(MPEG4 Part 10),支持H.264 Main Profile和Baseline Profile;

(2)支持最大分辨率:2048×1024;

(3)支持1路1080i高清/2路720pi高清/8路D1输入;

(4)8路I2S输入接口;可配置为主模式和从模式;

(5)PCI接口,32bit,时钟频率33/66MHz;

(6)2个独立的DDR SDRAM控制器,每个控制器字宽为32bit;

(7)一个MII/RMII接口支持100/10Mbps两种速度,完全兼容IEEE802.3规范;

(8)一路视频输出接口,符合BT.656视频标准;

(9)2个独立的I2C接口;

(10)JTAG下载调试接口;

(11)16根双向GPIO。

FH8735支持H.264 Main profile和Baseline profile视频压缩格式,可以进行8路标清480i/576i实时编码,也可以对一路1080i、两路720p的高清信号实时编码。除了高性能的视频编码能力,FH8735提供了丰富的视频预处理功能,对输入视频进行deinterlace、de-noise、OSD叠加、缩放、移动侦测等处理。为了配置外接的视频和音频接收芯片,FH8735提供两路完全独立的标准I2C接口,以应对可能出现的外部设备I2C地址冲突。作为编码协处理器,FH8735配备了灵活的主机接口,主机可以通过PCI或者HPI接口与FH8735进行控制和状态信息的通信,或访问FH8735外接DDR SDRAM。FH8735内部有两组独立的DDR控制器,可以根据实际系统对编码器性能的需求配置一组或两组外部DDR SDRAM。

为了满足某些应用对预览视频的需求,FH8735有一组标准的BT.656视频输出端口,可以把经过视频预处理单元输出的多路预览视频根据需要分割和合并,并编码为一路BT.656格式的视频输出。 (责任编辑:admin) |