|

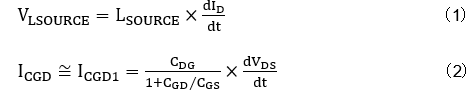

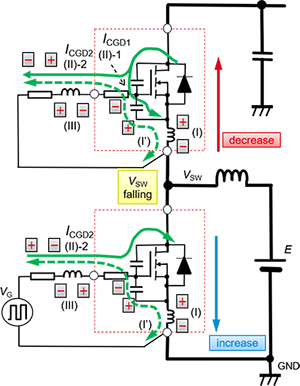

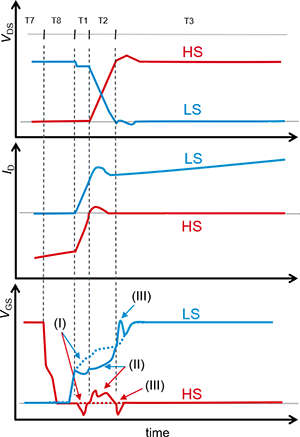

当SiC MOSFET的LS导通时,首先ID会变化(下述波形示意图T1)。此时LS的ID沿增加方向、HS的ID沿减少方向流动,受下述等效电路图中所示的事件(I)影响,在图中所示的极性产生公式(1)的电动势。公式(1)与上一篇文章中使用的公式相同。该电动势引起的电流将源极侧作为正极对CGS进行充电,因此在LS会将VGS向下推,在HS会将VGS向负极侧拉,使之产生负浪涌(波形示意图VGS的T1)。

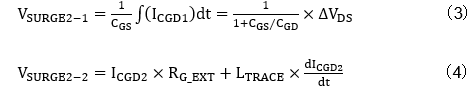

当ID的变化结束时,LS的VDS的电位降低(波形示意图T2)。所以,公式(2)中的电流就像等效电路图中的(II)-1、(II)-2那样流动,并且VGS会分别引发下列公式(3)、(4)中的电压上升。

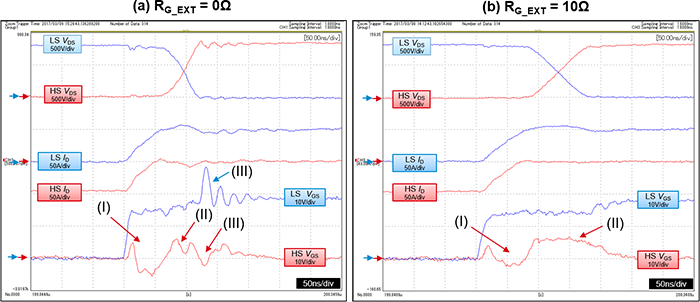

VDS刚刚开始变化后,公式(3)的VGS上升为主,随着时间的推移,公式(4)的VGS也开始上升。也就是说,MOSFET的CGD/CGS比、驱动电路的RG_EXT、栅极驱动信号图形布线的电感值LTRACE具有很大影响。 如等效电路图所示,HS中的(II)-2的电流ICGD2处于VGS提升方向。因此,本来应该处于OFF状态的HS因VGS的提升而开始了导通工作。这种现象称为“误启动”。当HS发生误启动时,就会与LS的导通工作重叠,致使HS和LS的MOSFET同时导通,从而引发直通电流。 ICGD2会持续流动到LS的导通工作结束,并被积蓄在LTRACE中,但会在VSW变化结束的时间点消失,LTRACE产生电动势。这就是事件(III)。受RG_EXT等开关条件影响,ICGD2可能会达到几安培,并且该电动势可能会增加。 受上述事件(I)、(II)、(III)的影响,LS导通后的Gate-Source电压呈现出波形示意图中所示的动作。波形示意图和等效电路图的相同编号表示同一事件。另外,图中VGS的虚线波形表示理想的波形。 外置栅极电阻的影响 下面是SiC MOSFET桥式结构的LS导通时的双脉冲测试结果。(a)波形图的外置栅极电阻RG_EXT为0Ω,(b)为10Ω。图中的(I)、(II)、(III)同前面相应编号的事件。

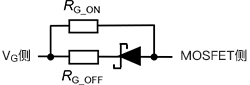

比较(a)和(b)的波形可以看出,RG_EXT越小,由事件(I)引起的VGS下降就越大。此外,由于开关速度非常快,因此事件(III)在(a)中很突出;但由于RG_EXT为0Ω,因此几乎没有观察到事件(II)的波形。另一方面,在(b)中,事件(II)-2和RG_EXT引起的VGS升程明显。 从该结果可以清楚地看出,要想降低诱发LS导通时HS误启动的事件(II)-2的VGS升程,就需要减小HS关断时的外置栅极电阻RG_EXT。然而,多数情况下,HS和LS的RG_EXT是相同的,因此,当减小RG_EXT时,LS的dVDS/dt将增加,如公式(1)所示,HS的ICGD会增加。从公式(4)可以看出,结果会导致HS浪涌升高。 有一种对策方法是,使导通时和关断时的RG_EXT分离,并且仅减小关断时的RG_EXT。常规方法是使用二极管的方法,如右图所示。使用这种方法,在导通状态下工作的电阻只有RG_ON,而在关断状态下,二极管导通并成为RG_ON和RG_OFF的并联电阻。因此,相对于导通时的电阻值,关断时的电阻值变小。

另外,与最前面说明中使用的波形示意图不同,HS的VGS波形之所以在紧靠事件(I)之前的位置向正极侧振荡,是因为事件(I)的电流开始流动的瞬间LSOURCE引起的电动势在通过CGS后立即被观测到了。 审核编辑:郭婷 (责任编辑:admin) |