|

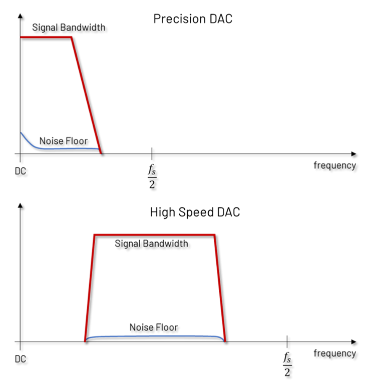

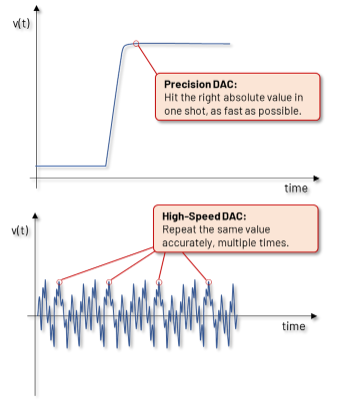

直流精度是高速DAC和快速精密DAC之间的主要区别。通常很难解释这种差异的原因和影响,而且当两种类型的DAC提供相同的分辨率和相同的线性度时。甚至令人失望的是,快速精密DAC在更新速率方面仅触及了高速DAC的下限。本博客介绍并分析了这两种类型的DAC的异同。 事实上,快速精密DAC和高速DAC专为不同的应用而设计。图 1 描述了它们的工作方式。 快速精密DAC旨在提供出色的直流精度,并在代码之间快速、干净地转换。信号的“信息”包含在直流值中,优点在于变化的速度。信号频谱范围从直流到几十MHz;带宽越高,DAC越快。然而,更高的带宽意味着更多的噪声添加到直流信号中,最终会使LSB无法辨别。 高速DAC设计用于在数百MHz宽甚至几GHz的通带内提供出色的频谱清洁度。信号信息包含在频谱中,优点是样本的相干性。信号的频谱被限制在某个频段内,只有该频段的噪声是相关的。只要噪声密度保持不变,带宽就可以增长以容纳更多信号。

图1. 快速精密DAC和高速DAC之间的频谱差异 让我们探讨每种类型的转换器如何面对常见的设计挑战。 噪声 虽然快速精密DAC可用于产生非常干净的谐波信号,但在许多应用中,目标是一次性达到正确的值。如图2所示,DAC在两个代码之间切换的信号具有快速步进,然后缓慢收敛到所需值,称为建立时间。为了充分利用DAC的分辨率,当输出达到稳态时,峰值噪声电平必须小于1 LSB。

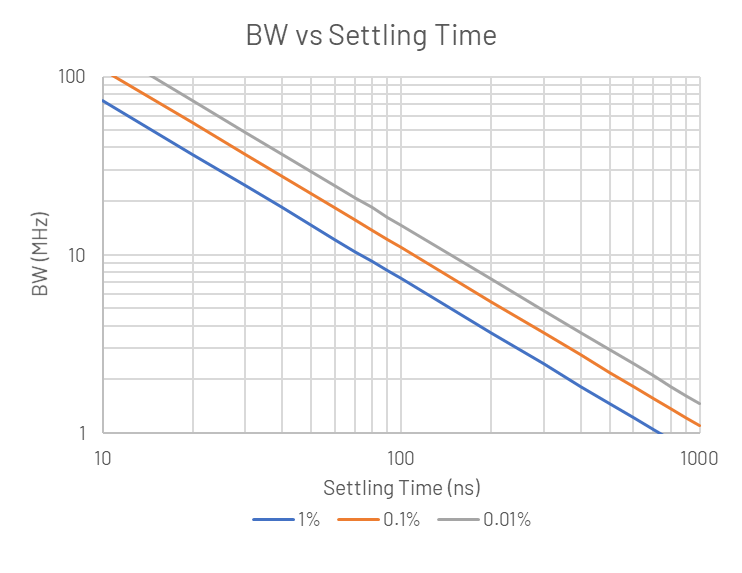

图2.快速精密DAC的建立和收敛。 如前所述,精密DAC将直流的所有噪声累积到器件的带宽,其中包括1/f噪声和宽带噪声。更快的DAC需要更多的带宽才能更快地建立,这意味着更多的噪声,使得保持LSB的可辨别性变得更加困难。因此,快速精密DAC试图将总噪声功率降至最低,而高速DAC则试图在目标频带内保持较低的噪声密度,如图1所示。 如果我们假设快速精密DAC中的峰值噪声必须小于1 LSB,则可以得出结论,对于给定分辨率,峰值噪声的速度是有限的。我们无法将噪声降低到本底热噪声以下,因此这会限制信号的带宽。 输出信号与最终值的收敛最终遵循指数方法,而不管输出驱动器具有单极点或共轭极点。这是一个忽略非线性效应的近似值,但了解预期性能的大致概念很有用。基于这种方法,我们可以估计在给定时间内建立到定义精度所需的带宽。结果如图3所示。例如,如果我们希望AD3552R在0 ns内建立至1.100%精度,则需要外部TIA具有3 MHz的10dB带宽。AD3552R是一款双通道、33 MUPS精密DAC,采用外部TIA进行I/V转换。

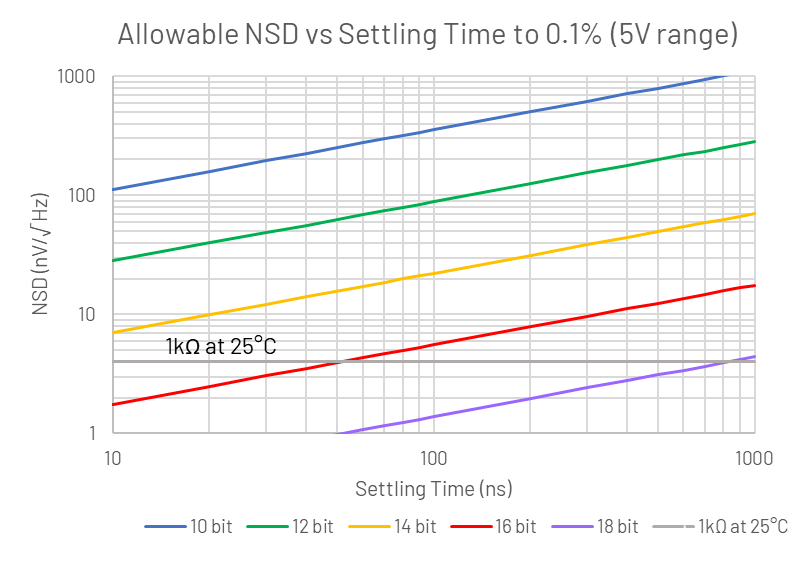

图3.1 所需的带宽圣对电路进行排序,以达到给定的建立时间,并具有指定的精度。 带宽越大意味着噪声越多,而且当收集的噪声远远超过3 dB截止频率时。如果我们要求该噪声的峰值必须小于1 LSB,我们可以计算出在给定的建立时间和DAC分辨率下我们可以承受的噪声密度。这是使LSB可识别的要求。图4中的曲线假设没有1/f噪声,等效噪声带宽(ENBW)对应于一阶电路。在 0V 范围内,建立时间精度为 1.5%。

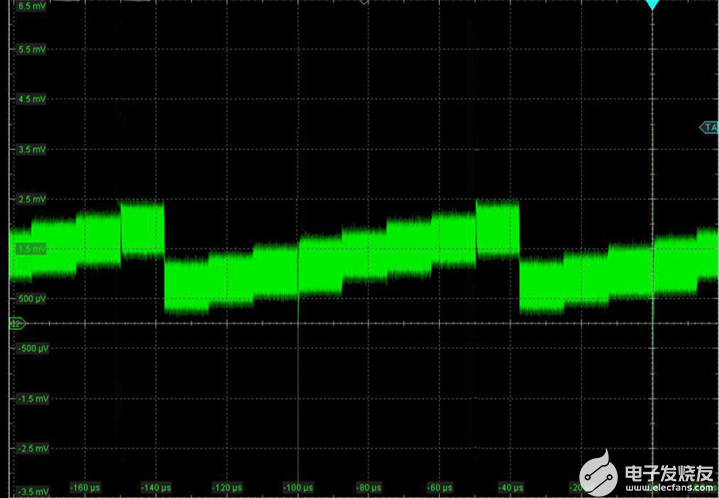

图4.DAC的最大噪声密度,以便在给定分辨率下可辨别LSB。 图4中的水平线表示1 kΩ电阻在25 °C(即4.1 nV/√Hz)时的热噪声密度。使用具有精密DAC的低阻值负载很困难,因为电压跨度很高,这意味着功率很大。 根据图4中的曲线,在16 ns内建立至0.1%的100位DAC需要低于5.6 nV/√Hz的噪声密度,才能在5V范围内识别LSB。相反,如果DAC的噪声密度为10 nV/√Hz,则为了保持LSB的可辨别性,它只能提供300 ns的建立时间。 图5显示了一个带宽过大的DAC示例。从代码更改为代码足够快,但总数会导致 LSB 步骤部分重叠。

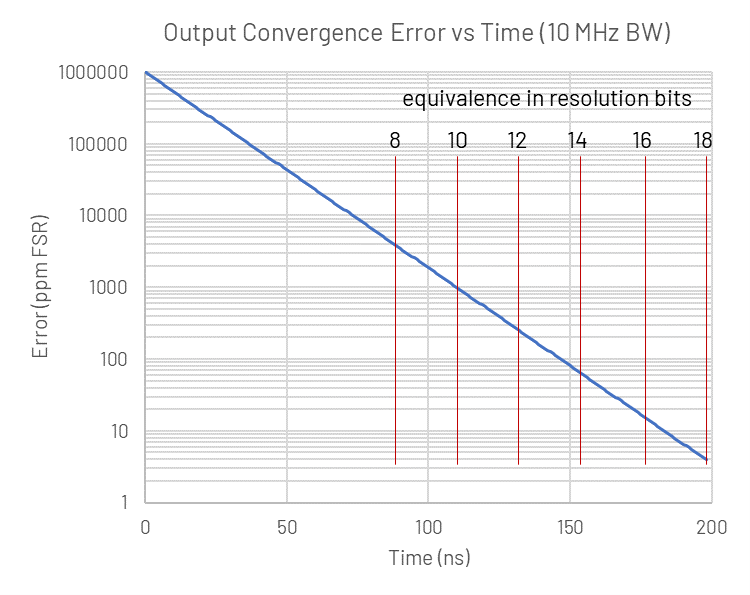

图5.在带宽过高的DAC中,宽带噪声会导致LSB阶跃部分重叠。 对于高速DAC,情况有所不同。这些器件设计用于在相干时间内产生带限和周期性的信号。多音调制对每个载波带宽内的噪声很敏感,因此总噪声无关紧要。解调发生在一定时间内,因此在此期间对信号和噪声进行平均,因此信号的点值无关紧要。调制信号通常是通带,甚至看不到1/f噪声。总之,高速DAC更关心噪声密度,而不是总噪声功率。 建立时间 查看速度/精度权衡的另一种方法是,在给定带宽下,信号在1 LSB以内所需的时间。具有10 MHz带宽的DAC的指数收敛误差如图6所示。 如果具有10 MHz带宽的DAC产生满量程步进,则90 ns后的精度仅在1 LSB以内8.如果我们希望信号精确到1 LSB16,我们必须等待 180 ns。如果我们希望DAC收敛得更快,我们需要更多的带宽,这意味着更多的噪声。在某些时候,增加带宽是没有回报的,因为噪声使LSB无法辨别,从而导致有效位数的减少。

图6.信号在给定分辨率的1 LSB以内所需的时间,带宽为10 MHz,不包括噪声。 通常不需要高速DAC来产生全阶跃响应,因此数据手册中通常不提供此数据。它们主要用于多音调制,其中信号具有高斯幅度分布和有限的频谱,因此不需要满量程转换。高带宽允许在小信号中快速建立,但满量程上升时间可能相当大。表1显示了AD3552R和AD9726之间的比较,AD9726是少数引用这些数据的高速DAC之一。AD16是一款400位、<> MHz宽带DAC。 AD3552RAD9726单位更新速率33400MUPS小信号建立时间6510.5ns上升时间 (10%-90%)25500ns

表 1.上升时间和建立时间比较 准确性 精密DAC旨在驱动电路,其中信号的直流值转换为现实世界中的绝对电平或定位。此外,我们可以要求DAC快速,但最终必须保持精确。这在开环应用中尤其重要,因为开环应用中没有反馈来执行校正或没有时间进行此类操作。作为一次性应用,DAC必须以绝对精度产生首次正确信号。 另一方面,高速DAC利用解调过程,其中信号不是在点上,而是在相干时间内。因此,DAC需要产生具有良好精度的信号,但不一定是绝对的。在解调过程中,目标频带外的噪声将被忽略。信号在时域中可能看起来很嘈杂,但在频域中仍然具有合理的噪声水平。 图 7 显示了这两个概念的比较。

图7.快速精密DAC和高速DAC的精度要求。 结论 在处理快速精密DAC时,需要在速度和精度之间或带宽和噪声之间进行权衡。建立速度越快意味着带宽越大,从而将更多的噪声传输到输出信号中,最终使LSB无法辨别。 此外,快速精密DAC需要在单次中再现准确的信号,而高速DAC产生在较长时间内进行评估的信号。前者需要低总噪声和满量程捷变性,而后者需要低噪声密度和良好的小信号带宽。 审核编辑:郭婷 (责任编辑:admin) |