|

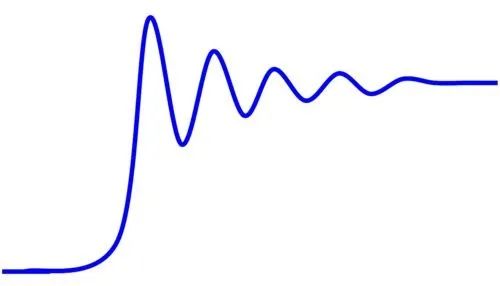

将阻抗匹配之前,先给大家引入几个名词: 传输线:由两条有一定长度的导线组成,比如同轴电缆、微带线、带状线(PCB板子中的铜走线)等等。 均匀传输线:如果导线上任一处的横截面都相同,比如同轴电缆,这样的传输线为均匀传输线,即阻抗处处相等。 瞬时阻抗:信号从在传输线上进行传输时,电流经过每一个地方所受到的阻抗为瞬时阻抗,对于均匀传输线,当材料相同,横截面积相同,则信号受到的瞬时阻抗也是恒定的。 特性阻抗:对于均匀传输线,信号在上面传播时,在任何一处受到的瞬时阻抗都是相同的,这个瞬时阻抗称为传输线的特性阻抗。 传输线的时延TD:通俗易懂的理解为信号从传输线的源端到终端所用的时间 以上基本概念介绍完了,我们开始步入正题。 我们大家在测试信号波形中遇到很多过冲,下冲,振铃现象,这些都属于信号完整性的问题。当然,这些现象产生的原因就是因为阻抗不匹配,因为有反射信号来回反弹。 阻抗不匹配的现象例如图1:

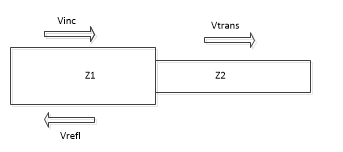

图1 那小编想问一下大家:为什么有反射信号? 根本原因:为了维持系统的平衡,边界处不可能出现电压不连续,否则会出现一个无限大的电场,也不可能出现电流不连续,否则会先交界面出产生净电荷。 下图2中: Z1:左边的阻抗 Z2:右边的阻抗 Vinc:入射信号 Vtrans:穿过交界面的传输信号 Vrefl:反射信号 其中,ρ为反射系数

图2 信号在传输过程中,如果遇到了阻抗不匹配,如图2则会出现反射信号,入射信号的一部分穿过突变处进入Z2,一部分反射回源端。 交界面两侧电压相同的条件为:Vinc+Vrefl=Vtrans 交界面两侧电流相同的条件为:Iinc-Irefl=Itrans 那么为什么我上面提到:出现阻抗突变时,为什么会出现反射信号,我们用公式来证明 一下: 假如没有产生反射电压,并且要保持电压电流连续,是不是会有V1=V2,I1=I2 Z1=V1/I1 ,Z2=V2/I2,那么如果出现了阻抗突变,即阻抗不匹配,那么Z1≠Z2,那么此时V1还等于V2吗?I1还等于I2吗?显然,肯定不相等。为了继续保持这种系统平衡,就出现了反射电压。 以上我就把为什么出现振铃的原因,为什么出现反射信号的原因解释清楚了。 小编还想给大家从原理上分析一下为什么会出现图1中的忽高忽低的波形。 先给大家上一个反弹图,如图4:

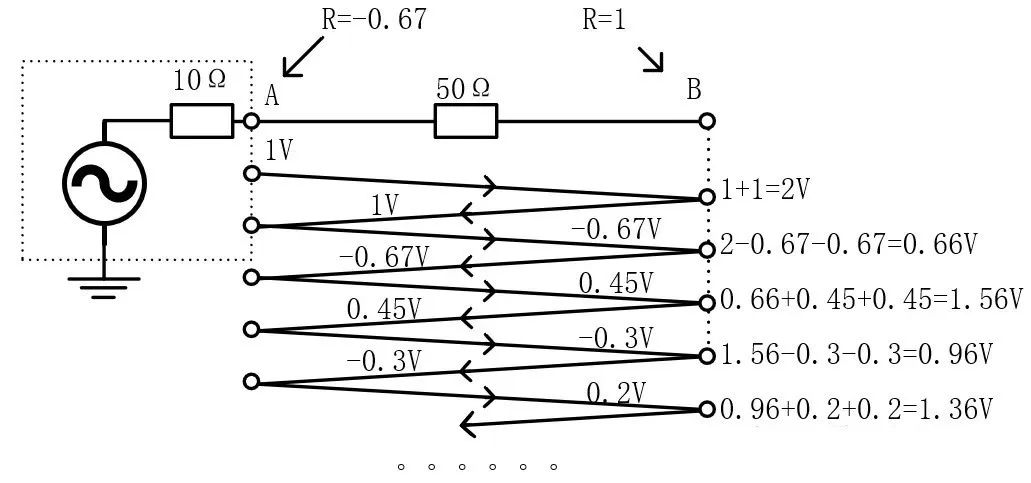

图4 图4中10R为驱动器内阻,我们常见的驱动器内部一般都是TTL电路,它的内阻或者说输出电阻很小,一般十几欧姆。 图4中50R为传输线的特性阻抗,就是说传输线上阻抗处处为50R 图4中R=-0.67,指的是信号从末端反射回源端的反射系数R=10-50/10+50=-0.67 图4中R=1,此图是我们没有加任何端接电阻,末端我们理解为开路,即阻抗无穷大。 R=无穷/无穷=1,即全反射。 我们入射信号为1V,即A点的信号幅值为1V,信号从A点到B点后会发生反射,因为B点处出现了阻抗突变,传输线为50R,终端为无穷大,因此发生了全反射,那么B点电压=入射信号+反射信号,其中反射信号为1V*R(R=1)=1V,入射信号为1V,那么B点第一次出现的电压为2V。 B点处的反射信号1V返回A点后又会遇到阻抗突变,因为驱动器内阻10R和传输线50R不相等,那么反射回B点的电压为:1V*(-0.67)=-0.67V,-0.67V电压又会到B点,在B点遇到阻抗突变,又会出现全反射,-0.67V又反射回A点,那么此时B点电压为:Vb=之前的2V+反射电压+入射电压=2-0.67-0.67=0.66V,以此类推。 大家将Vb点波形在时间-幅度坐标中画一下,就会发现为什么振铃是忽高忽低的波形了。就是这个反射信号的原因。 那么接下来我就给大家讲一下出现这种现象的时候,怎么解决,或者通常有几种解决方法。 Layou工程师解决+硬件工程师解决 Layout工程师能在尽可能优化的前提下:走线时尽量少打孔以及换层走线,因为打孔,就一定会出现阻抗不匹配,并且走线的时候尽量走Fly-by或者菊花链拓扑型走线。见图5

图5 菊花链走线或者Fly-by走线缺点就是不容易做等长,比如DDR走线,T型容易做等长,这个就需要根据自己实际问题去选择。 走线不要出现直角,锐角,这个为什么不能这样干,这两种方式走线,在拐角处一定会出现阻抗不匹配,大家在纸上画一下就很容易理解,就当是做初中数学题了。 硬件工程师:加端接电阻 端接电阻:有5种(源端串联端接、终端并联端接、戴维南并联、RC端接、二极管端接)。我在工作中比较常用的是源端串联端接,RC端接,二极管端接。我们大家可能最常用的其实就是第一种,下期给大家讲一下这五种端接方法,各自的特点以及应用的场合。 编辑:黄飞 (责任编辑:admin) |