|

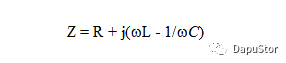

业界经常流行这么一句话:“有两种设计师,一种是已经遇到了信号完整性问题,另一种是即将遇到信号完整性问题”。固态硬盘作为一种高集成度的高时钟频率的硬件设备,信号完整性的重要性不言而喻。借着这句话本文主要跟大家聊下信号完整性的一些基本内容。 什么是信号完整性?通俗来讲,信号在互连线的传输过程中,会受到互连线等因素的相互作用而使得信号发生波形畸变的一种现象,这时可以说信号在传输中被破坏了,变得“不完整”。信号完整性没有一个唯一的规范定义,从广义上讲,指的是信号在高速产品中由互连线引起的所有问题。 高速数字系统中,信号完整性起着重要作用。如果信号完整性有问题,可能会造成电路无法正常工作。影响信号完整性的关键电气特性就是互连线的阻抗,它是解决信号完整性的方法核心。 1. 阻抗 电路中电流所起的阻碍作用叫做阻抗。阻抗单位为欧姆,常用Z表示,表达式是复数:

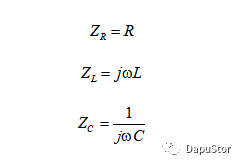

其中实部为电阻和虚部表示电抗(容抗和感抗)。为什么用复数?电阻代表对信号幅值的衰减,电抗代表对信号相位的改变。以下分别为电阻,电容,电感部分的阻抗:

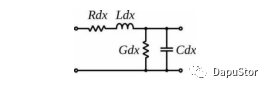

1.1特性电阻 特性电阻是与传输线相关的概念,信号在传输线上的实际传输过程中,会受到传输线上寄生参数(如寄生电感、寄生电阻、寄生电容)的影响,特性阻抗就是综合传输线场景下跟这些寄生参数合成的阻抗。 用下图模型来表示单位长度的传输线:

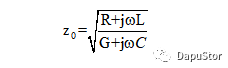

此模型下的阻抗表达式为:

在实际的PCB应用中传输线的电阻部分,可以忽略不计,即上式中的R和G为0,PCB传输线特性阻抗的一般表达式:

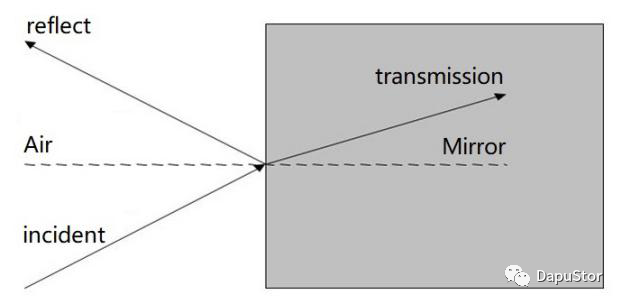

L是单位长度传输线的固有电感,C是单位长度传输线的固有电容 传输线阻抗在PCB行业通常将传输线的特性阻抗简称阻抗。 1.2阻抗匹配 信号在传输线上传输过程中会受到传输线的阻抗,任何阻抗的突变都会引起信号的反射和失真,过度的反射和失真会引发信号完整性问题。阻抗匹配是指信号源或者传输线跟负载之间达到一种适合的搭配。所以说,阻抗匹配对于一个高速数字系统是十分重要的。阻抗匹配主要有两点作用,一是调整负载功率,一是抑制信号反射。 可以用水在管道流动来类比信号在传输线上传输,管道粗细不一致会导致在关节处损失水流的动能,同样的,传输线阻抗不匹配会造成电路能量严重浪费。 2. 反射 在上文中提到了因阻抗不匹配而引起信号反射,为了解释信号反射我们可以用光在不同介质中传播来形象的介绍,光从空气射向水面或者玻璃时,有一部分光被反射,另一部分光会折射进入另一种介质,如下图:

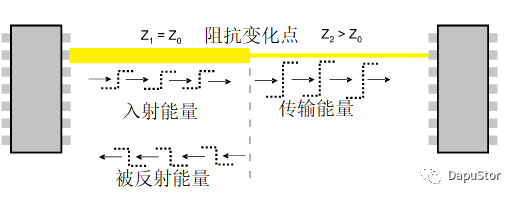

同样的,信号也一样,如果传输线的阻抗不一致,在阻抗跳变的地方,一部分能量继续传输,一部分能量会被反射回去,如下图:

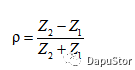

反射系数的表达式为:

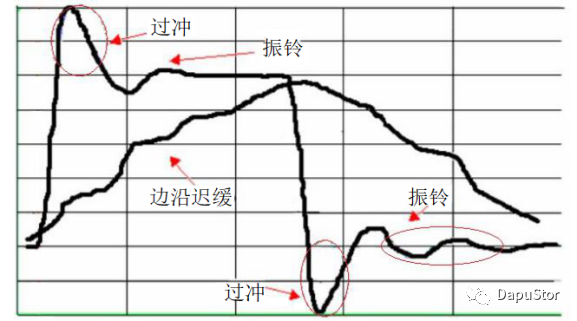

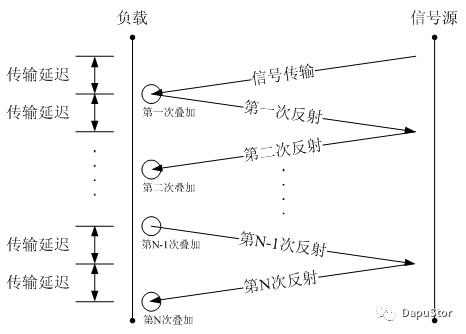

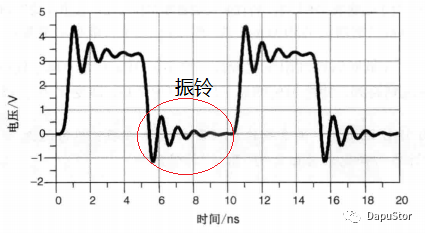

反射会造成信号出现过冲(Overshoot)、振铃(Ringing)、边沿迟缓(回勾现象)。过冲是振铃的欠阻尼状态,边沿迟缓是振铃的过阻尼状态。下图为信号反射的三种表现形式:

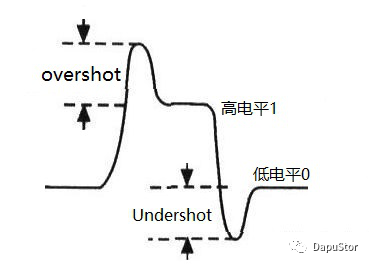

2.1过冲和下冲 过冲指的是第一个峰值或谷值超过设定电压值,下冲是指下一个谷值或峰值,对于上升沿来说,过冲是指最高电压;对于下降沿来说,过冲是指最低电压。如下图所示:

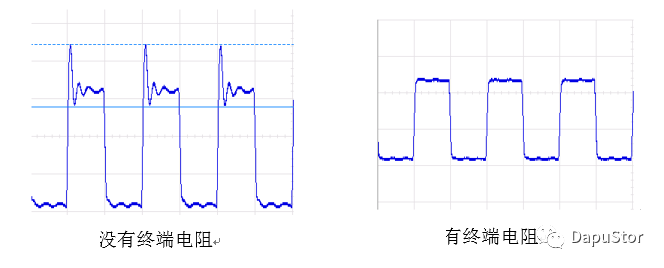

过冲严重时会引起保护二极管工作,导致过早的失效,严重时还会损坏器件。而过分的下冲,能够引起假的时钟或数据的错误,这样可能会给器件带来潜在的累积性伤害,缩短其工作寿命,从而影响产品的长期稳定性。一般信号的发送端的阻抗较低,信号接收端的阻抗较高,如果发送端的与接收端的阻抗不匹配,发送的信号会在发送端和接收端之间来回反射,从而导致信号的反射出现过冲和下冲。 解决过冲的一般方法是匹配,或叫端接( Termination)。匹配的中心思想是消灭信号路径端点的阻抗突变。 下图是没有终端电阻和有终端电阻的波形图对比:

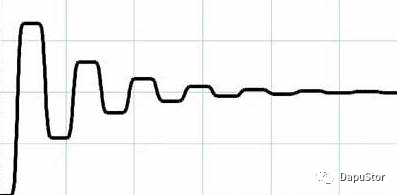

2.2振铃 上面小节介绍了过冲和下冲,如果过冲和下冲反复就会出现振铃现象,过冲往往伴随有振铃,或者说,过冲是振铃的一部分。振铃产生的第一次峰值电压,就是过冲。为什么要将过冲和振铃分开来讲,是因为他们的危害不同,振铃除了具有过冲的危害之外还有它的波动可能会多次超过阈值判定电压造成误判,并且会急剧地增加功耗,影响器件寿命。下图是振铃产生的原因:

下面是振铃的波形的表现形式:

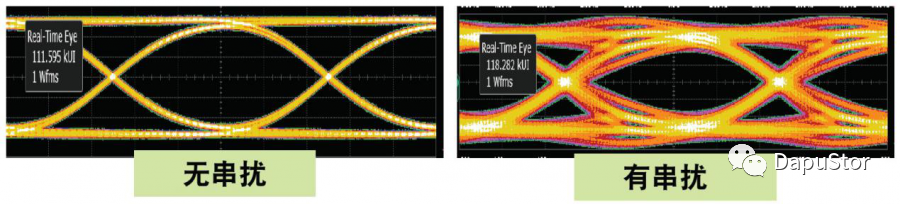

振铃现象的根本原因是由信号反射引起的,其本质仍然是阻抗不匹配,所以减小或者消除振铃的解决方式跟处理过冲和下冲无异,必须要进行阻抗匹配端接。 在实际的应用场景中,会遇到多种信号完整性问题,典型问题有如下几种:反射、串扰,电源/地噪,时序等。其中,发射和串扰是引起信号完整性问题的两大主要原因。 3. 串扰 在上面我们介绍了信号反射是因为传输线的阻抗突变导致的,而串扰是信号线间互感和互容引起的噪声,是由同一PCB板上的两条信号线与地平面引起的,原理是在高频时PCB上的任何两个器件或导线之间都存在互容和互感,当一个器件或一条信号线上的信号发生变化时,其变化会通过互容和互感耦合到其他器件或信号线,即串扰耦合。当耦合信号或串扰信号足够大时,接收串扰信号的信号线上就会出现信号完整性问题。 一个信号受到干扰信号的串扰影响会发生变形,让其眼图闭合,在工程中我们希望能够尽量张开的眼图,因为这样才能有足够的余量保证无误的传输数据,相反的,如果眼图闭合会使得余量变得很小而出现结果错误。

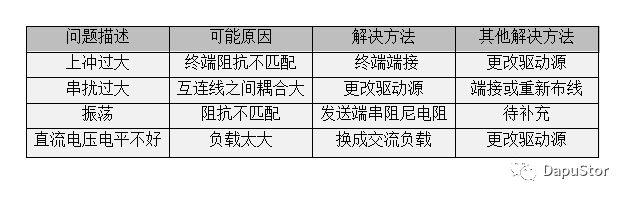

引起串扰的原因有很多,例如PCB布线的长度、间距、层叠、参考地平面的状况、端接方式、驱动/接受端的电电气特性等因素。解决方式也主要针对上面提到的这些因素来处理。 4. 信号完整性问题解决方法 在介绍如何解决信号完整性问题前首先回顾下引起信号完整性的因素,基本因素就是阻抗不匹配,然后是串扰,电源完整性,时序等。在实际的信号完整性分析中,需要对引发信号完整性的根源进行描述,例如: a.信号上升沿过短 b.阻抗匹配不合理 c.PCB结构设计不合理 d.电源完整问题 ... ... 以下简单汇总了常见的信号完整性问题,并列出了引起问题的原因和相应的解决方法:

编辑:黄飞 (责任编辑:admin) |