|

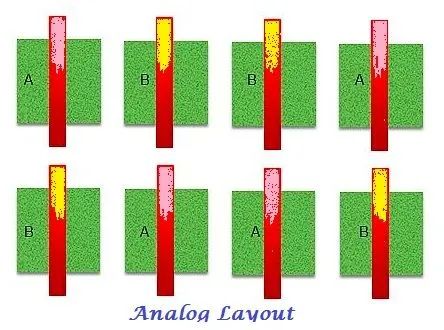

最近刚交gds,趁热打铁总结一下需要跟layouter沟通的注意事项。略过内心吐槽一万字……我琢磨着下次先弄一个checklist,然后每日三省吾身才好…… A. 先说说信号通路有关的: 重点需要matching的管子标注在schematic上面;(common centroid)

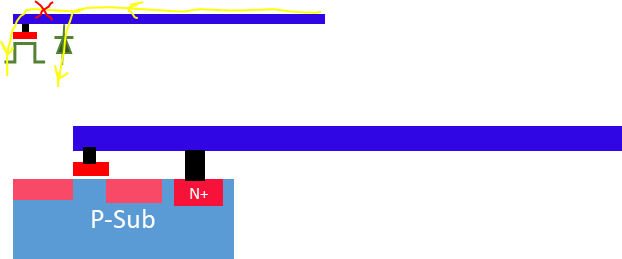

保证信号通路尽量笔直而且够短;(如果是走电流的通路,拐角的地方可以走45°。如果出现off grid的drc error,layouter会加一点东西,改起来不难) 特别敏感的通路记得加上shielding,比如用m4走线,那就左右各加一条m4,上下m3和m5都加上,然后把shielding的线连到vss去;

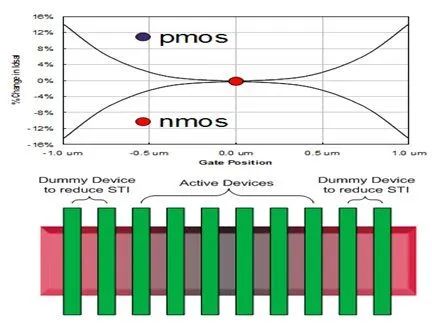

有时候layouter加的dummy还是不够。我记得好像为了防止STI,dummy最好大于1um宽。面积够用就多加点,反正最后为了过drc的density check还得加dummy filling呢!

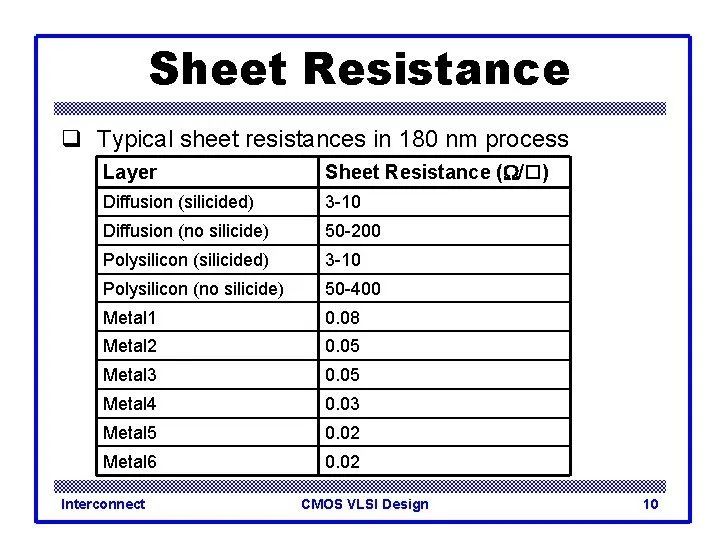

B. 再说一下电源和地的走线: 大电流自然是需要用高层金属走线(高层金属比底层的厚很多),能宽一点就宽一点,毕竟算导线的电阻是用方块电阻的,两条线一样都是10um,一条是1um宽,一条是0.5um宽,后者的方块电阻就是前者的两倍了。(老大前天跟我说之前遇到过从pad到core,vdd降低了1V的情况……可怕极了)

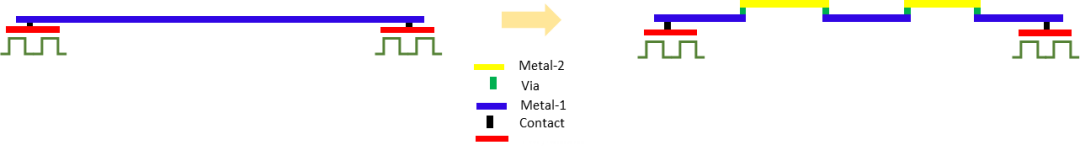

layouter很习惯在device上面盖一层一层的vdd和vss走线,然后用多层的via垂直打孔下来,因为可以缩短走线的长度而且让版图更加紧凑;对于不那么敏感的模块,这样子问题不大;但是有一些很敏感的模块就别这样了,记得提前告知layouter; 电流很大的话,core尽量离vdd,vss的pad近一些,不用非把core放在正中间; C. 其他需要注意的地方: 如果不想让dummy filling加在chip core上面,记得让layouter加block marker;当然有可能同时带来drc的density过不了的情况。有必要的话问问能不能waive掉,说不定可以呢? 其实不想浪费面积,可以让layouter在多余的地方加上mosfet做去耦电容放在电源和地之间(或者reference电压和地之间),先画一个基本涵盖了全部层的unit,然后把空地都摆上好了; 提前注意一下可能出现antenna问题的地方:解决办法除了大家都知道的跳线,还有加buffer,还有在走线旁边挂一个反偏的diode;哪种容易就用哪种吧^_^参考解决方法

LDO的话,如果同时给几个block供电,记得用star connection,别一条线先到block a再到block b……尽量保证LDO到各个block的距离差不多; 有时间的话,其实可以自己先摆好device,再让layouter在上面画各种连线,毕竟我们designer其实只相信自己对吧?^_^ 越是靠近deadline越不能慌,肯定有人一直赶着push,但是一旦发现layout需要改的地方,就立刻联系layouter改,毕竟chip回来能不能work都是designer的锅,layouter可不会背锅呢。都是layout review过的,designer当时没看到问题那就是designer的事情……(作者君干过最后差点误删自己的working directory的可怕错误,吓死宝宝了,手贱再来一次心脏病就要发作了)

|