|

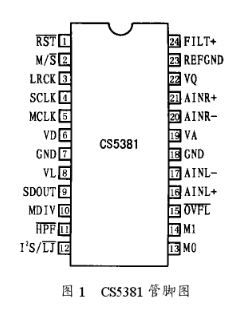

1、引言 在弱信号检测仪器开发过程中,选用高精度的A/D转换芯片往往可以给设计带来方便。一般情况下,在对宽频带弱信号进行检测时,不仅要求ADC具有大动态范围,同时对ADC的采样速率也提出了更高的要求。CS5381是目前市场上动态范围和采样速率两项指标都很突出的一款24位ADC,它的推出为设计高速高精度采集系统提供了一个较好的解决方案。 2 CS5381的主要性能特点 CS5381是Cirrus Logic公司推出的120dB、192kHz高性能立体声模数转换芯片。该芯片采用24引脚TSSOP或SOIC封装,其引脚排列如图1所示。该芯片采用5V工作电源。它的内部集成了一个可直接与5~2.5V逻辑电平接口的电平转换器、一个可消除直流偏移量的高通滤波器、一个线性相位数字抗混叠滤波器和溢流监测器。CS5381所具有的这些特性使其在高品质音频处理和精密测控等领域都得到了很好的应用。

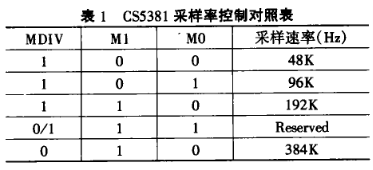

CS5381的主要性能特点如下: ●具有24位转换精度; ●采样速率可以达到192kHz; ●具有120dB动态范围; ●可工作于5V模拟电压和3~5V逻辑电压; ●兼容2.5~5V逻辑电平; ●带有线性相位抗混叠滤波器; ●采用差动模拟信号输入方式; ●具有主、从两种工作模式;●内置数字高通滤波器。 CS5381使用起来非常方便,可工作在主、从两种模式下。模式选择可通过管脚2(M/ S)来进行。当M/ S引脚为高电平时,CS5381工作在主模式(Master Mode),此时LRCK(其频率等于采样速率)和SCLK是输出管脚;而当M/ S为低电平时,CS5381工作在从模式(Slave Mode),该模式下,LRCK和SCLK变成输入管脚。如需改变CS5381的采样率,只需控制芯片的MDIV、M0和M1这三个管脚的逻辑电平即可。表1所列是主时钟为24.576MHz时,不同控制方式时采样速率的对照表。

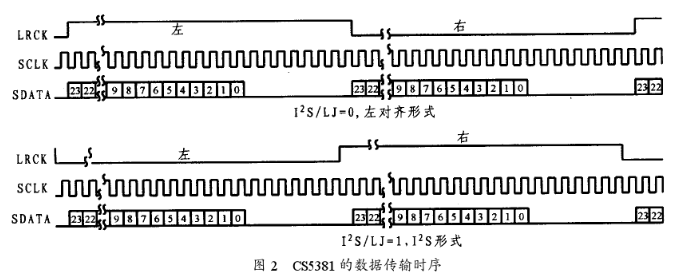

通常24位ADC都会产生一个微小的直流偏移,在CS5381内部有一个数字高通滤波器,可以通过给管脚HPF提供一个低电平使该滤波器有效,这样,芯片可以消除直流偏移。另外芯片还带有溢流监测器,当模拟信号的输入电压幅度过大而致使ADC转换溢出时,相对应的管脚LFV变低,因此,在该管脚与电源之间接一个发光二极管,就可以直观地显示出模拟输入是否溢出,从而根据需要调整前端放大电路的增益。 CS5381的模拟信号为差动输入方式,因此,它的前端要有一个简单的模拟调理电路。CS5381的转换结果是24位补码形式的串行数据,且左右通道交替输出,可用LRCK的高低电平来进行区分。输出数据有两种格式:左对齐和I2S。图2是CS5381的两种数据传输时序。

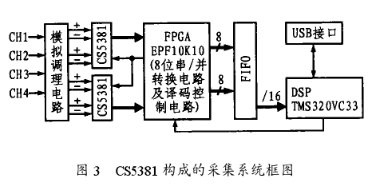

3、四通道并行采集系统的设计 图3所示是一个四通道并行采集系统的整体框图,该系统主要由TMS320VC33(以下简称VC33)、两片CS5381、一片FPGA(EPF10K10)和一个大容量FI-FO存储器构成。采集系统与主机的通讯采用USB接口。系统中的一片CS5381工作于主模式,另外一片则工作在从模式下,这样可以保证两片ADC工作时严格同步。

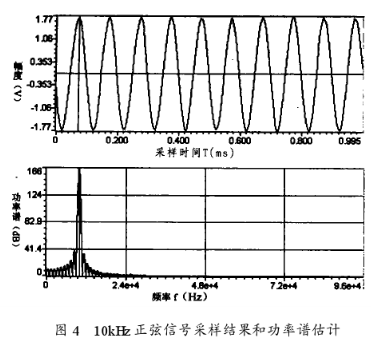

在基于CS5381的采集系统中,如何实现CS5381与TMS320VC33的接口是一个关键问题。具体的设计方案有两种:其一,由于CS5381采用同步串行数据输出方式,而TMS320VC33具有多通道缓冲串口(McBSP),因此,可以较为容易地实现二者的硬件连接。其二是通过CPLD/FPGA设计串并转换电路,并把CS5381输出的串行数据转换为并行数据,然后由TMS320VC33通过扩展IO对数据进行读取。这两种方案相比,第一种方案比较简单,但系统要设计四个独立的同步采集通道,并要使用两片CS5381,而TMS320VC33只有一个McBSP,所以此方案无法采用。第二种方案实现起来相对比较麻烦,硬件成本也较大。它通过把每片CS5381的串行数据转换成8位并行数据并经FIFO缓存,然后由TMS320VC33通过中断和DMA方式对四个通道的转换数据进行读取。 串并转换电路设计是CS5381和TMS320VC33接口电路的核心部分,它负责将CS5381输出的串行数据转换为并行数据并存储在FIFO中,同时产生相应的FIFO写信号。具体设计时,应当考虑以下三个问题: (1) 对于CS5381在左右通道的数据,除了24位转换结果数据外,还应输出一个8位的附加信息,因此,输出一道数据时,总共有32个时钟输出,而最后8位数据是无用的,这样,就需要有一个禁止逻辑来防止8位附加数据也写入到FIFO中。 (2) 由于串行输出时钟SCLK在CS5381工作期间是一直存在的,因此,在启动和结束串并转换时,应该有一个控制逻辑来使串并转换电路只有在LR-CK的上升沿(或者下降沿)触发下才能进行数据转换,以保证左右通道数据顺序的确定性。 (3) 转换电路要有使能控制,以便控制信号的采集时间。 4、测试结果 该采集系统利用标准信号源进行正弦信号采集测试,下面是对两种频率的正弦信号进行测试的结果分析。其中第一种测试结果如图4所示。对于10kHz的正弦信号,CS5381的主时钟MCLK为24.576MHz、它具有64倍的过采样率(采样速率fs=MCLK/64=192kHz),采样时间T为1ms。由采样结果和功率谱可以看出:系统中的CS5381采样数据在频率域的动态范围在120dB以上。

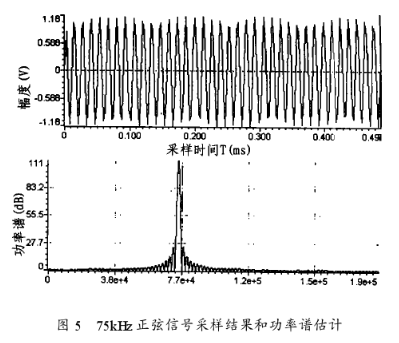

把系统采样速率fs设置为384kHz时,对75kHz正弦信号的采样结果及功率谱估计如图5所示,由采样结果可以看出:CS5381可以在384kHz的采样速率下对更高频率的信号进行采样,但从功率谱可以看出,此时动态范围及信噪比都在80dB左右,可见采样精度有较大幅度的降低。若要完成更高频率信号的采样,在对采样精度要求不是特别高时,可以考虑采用这种方式。

由此可以看出,由CS5381构成的这种采集系统具有分辨率高、动态范围大等特点,在混场源电磁法接收机中得到了很好的应用,可以对带宽为DC~75kHz、动态范围为120dB的电磁信号进行高精度数据采集。 责任编辑:gt (责任编辑:admin) |