|

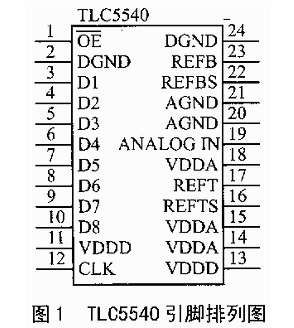

在高速数据采集卡中,核心部分是高速模数转换器。随着制造ADC的技术不断技术,美国的TI公司和ADI公司都开发出采样速度在100Msps,但价位低廉的器件。本设计采用TI公司的TLC5540,其特点是: *8位分辨率; *最高转换速率达40Msps; *内部采样和保持功能; *模拟输入带宽≥75MHz(典型值); *内部基准电压产生器。 它的引脚排列和功能如图1所示。

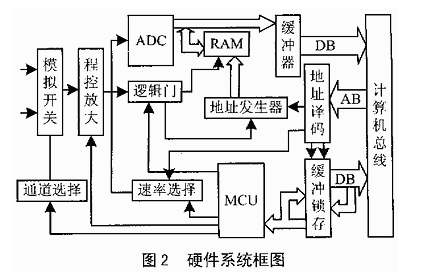

其中OE端是输出允许端。当OE为低电平时,允许数据输出;反之,D1~D8为高阻状态。ANALOG IN为模拟输入端,CLK为时钟输入端,其它一些引脚为一些地线、电源线、基准电压的输入调节端等。整个芯片的控制非常方便。 在数据采集中卡中,它的采样频率不仅仅取决于ADC的转换速率。在计算机数据采集系统中,采样频率可表示如下: fs=1/(tCONV+tACQ+tAID) 式中,tCONV是A/D转换的时间,tACQ是采样保持时间,tAID是数据传输与处理等辅助操作时间。可见,所谓高速,除了要求提高A/D转换的速度外,更重要的是设法减少tAID的时间。 设计中,在扩展板上增加1个或多个微控制器,作为前端从机,主要负责采样过程控制和数据存储时序的控制。微控制器与主机之间必须有专用的联络通道,以便主机能对从机实行控制及主从机之间的状态信息交换。这样,在高速采样的过程中,CPU不需要参与,采样数据存储完全由外部电路自动进行。在采样期间,CPU可以做自己的数据处理和其它工作。采样结束后,再由CPU读出数据进行存储和处理。完成后,又继续采样。数据采样与处理是交替进行的,即所谓的“间隙式采样方式”。当然,这是针对高速数据采样时采用的方法。在慢速采样时,可以完全由主机自行采样,实现边采样、边读数、边处理的真正同步方式。 整个硬件电路的设计原理如图2所示。

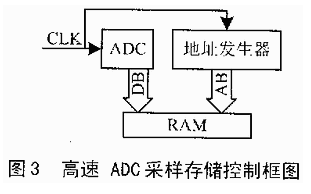

在本设计中采用AT89C51作为高速数据采集卡的控制核心。它的主要功能是: ①使用P1口与主机通信,接收PC机的命令及数据并纠错、解释、存储、执行; ②送出MCU当前状态信息,以便主机查询; 前面已经提到,在整个采样过程中,MCU负责全面的控制工作,主机与采样电路之间不需要任何的线路。主机只要把所要完成的任务编成规格化的指令,在每一次采样开始前全部发给从机。但它的数据只能送出,而不可以直接发送数据给主机的端口。从机的地位是被动的,送出的数据是否被接受由主机决定。 在本电路中,时序控制是非常重要的,尤其是ADC的采样时序和存储器的读取时序的配合很重要。TLC5540的时序控制比较方便,输出使能端OE一直置低,通过控制时钟输入端CLK来控制采样速率和存储速率。从图2可以看出,在扩展了1个存储器的同时扩展了1个地址发生器。地址发生器是由计数器组成的。也就是说,计数器计1个数,它的地址就改变一下。在本电路中,把外部输入的时钟作为TLC5540的CLK端和计数器的时钟端。 具体示意图如图3所示。

通过这样的电路,ADC的采样时序和存储器的存储时序就可以很好的配合,保证采样1个数据存储1个数据,不会发生丢失的情况。 以上所述,是采集卡需要采集高速数据时采用的控制方法。在设计中,为了提高卡的适用面,还特别设计了对于采集慢速数据的方法。 责任编辑:gt (责任编辑:admin) |