检测到高电平即认为已接收完一帧数据,继续等待下一帧起始信号低电平的到来,若接收完8比特数据后没有检测到高电平则认为这不是一帧有效数据,将其丢弃,继续等待起始信号。时序关系如图1所示,收发可同时进行,互不干扰。

图1 RS-232接口的工作时序

硬件电路原理图及说明

一个完整的RS-232接口是一个25针的D型插头座,25针的连接器实际上只有9根连接线,所以就产生了一个简化的9针D型RS-232插头座,常用的就是一个9针的D型插头座。通常只用到一根发送信号线、一根接收信号线和一条地线,其余的振铃指示、请求传送、清除传送、准备就绪及数据载波检测等线可以做悬空处理。

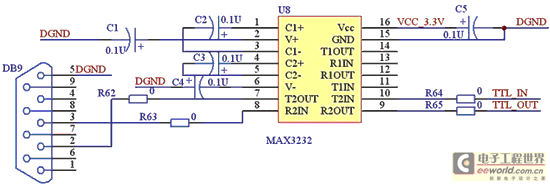

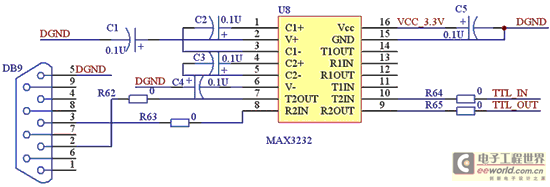

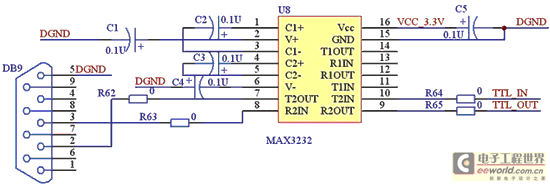

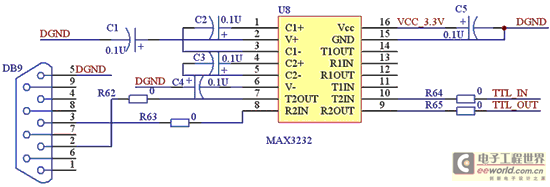

RS-232标准规定逻辑1的电平为 -15~-3V,逻辑0的电平为+3~+15V。CMOS电路的电平范围一般是从0V到电源电压,FPGA的I/O输入输出电压通常为0~3.3V,为了与FPGA 供电电压保持一致,必须加电平转换芯片。选用Maxim公司的MAX3232电平转换芯片,电路原理图如图2所示。

图2 RS-232接口电路

连线采用最简单的3 线制连接模式,即只需要两根信号线和一根地线来完成数据收发。而FPGA 只需要选择两个普通I/O引脚分别与接口芯片MAX3232 对应引脚T2IN、R2OUT相连即可完成将串口电平转换为设备电路板的工作电平,即实现RS-232电平和TTL/ CMOS 电平的转换。一个MAX3232芯片可以支持两个串口的电平变换,我们选择其中的一组接口,图中的4个电阻可以省去。在电路中加入了0Ω的跳线电阻,是为了在这组接口出故障时可以方便地跳线,使用另一组接口。

软件设计

异步收发器由波特率发生器、UART接收器和UART发送器三个模块构成。采用的是每秒9600波特的传输速度,而系统提供的时钟是 10MHz,这就要求进行速率变换。在实际中由于电路中存在干扰等因素,在数据边缘进行采样容易发生误判,只有在数据的中央进行采样出错的概率才能降到最低,所以使用16倍于波特率的时钟,即9600×16Hz=15600Hz。因此波特率发生器输出的时钟频率应为15600Hz,UART 收发的每一个数据宽度都是波特率发生器输出的时钟周期的16倍,采用Altera公司芯片内部自带的锁相环可以方便地实现。UART接收器和UART发送器均采用Verilog语言编程实现。

通常使用的数据多为并行数据,为了方便与系统中其他电路互连,UART接收器的输出数据和UART发送器的输入数据均为8比特并行数据。 UART接收器将串行数据接收下来并将其转化为并行数据送出,UART发送器将输入的并行数据转换为串行数据并按照UART的帧格式输出。

(责任编辑:admin) |