|

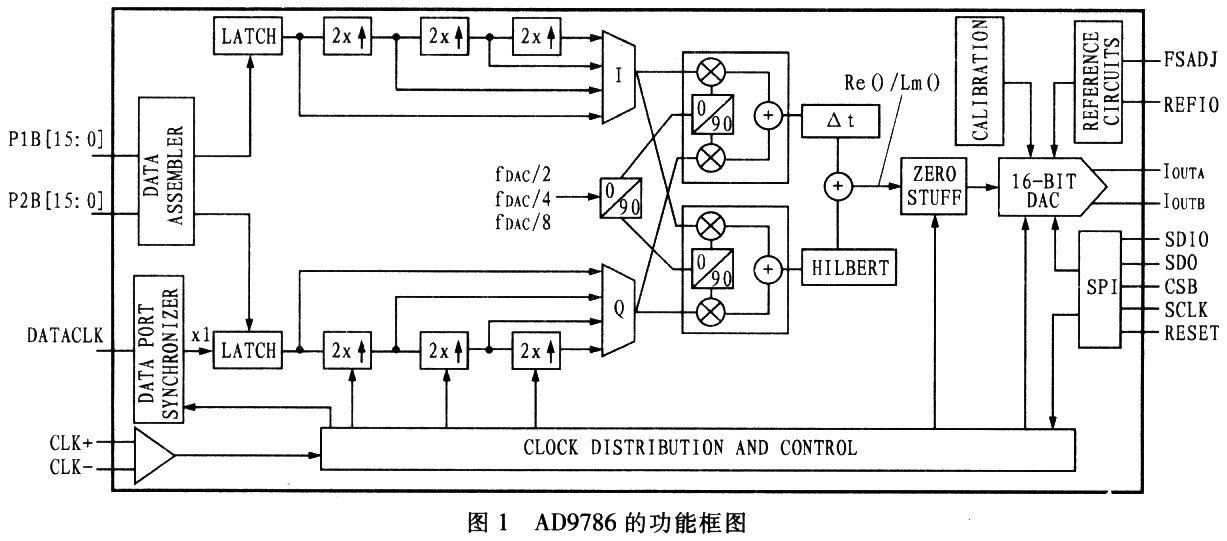

1、概述 AD9786是Analog Devices公司开发的一款面 向GSM、CDMA2000和WCDMA基站应用,基于 CMOS工艺的带有参数可调数据内插功能和信号处理特征的16bit高速、高性能数模转换器。该电路集成了数字中频调制模块和希尔伯特变换器,提供了方便的带宽设置和可选的边带抑制功能。可选的数据内插滤波器简化了对不同输入数据率数据输入的应用,同时也利用了过采样的性能增益。提供的2路数据通道可灵活地配置成1路或2 路输入,实部或虚部输出。灵活的时钟接口可以接收一系列输入类型的时钟信号,如1Vp-p正弦波、 CMOS和LVPECL电平信号,同时还有单端和差分 2种输入方式。内部的时钟模块可以产生所需要的数据接口时钟频率。同时提供了支持单端和差分应用的差分电流输出,满量程电流可达10mA~ 20mA。该器件还有1个串行控制接口,可提供方便的参数设置功能,通过对内部寄存器的操作实现了灵活多样的应用模式选择,可以根据用户的需求选择不同的应用模式。 2、AD9786的特性 图l示出AD9786的功能框图。

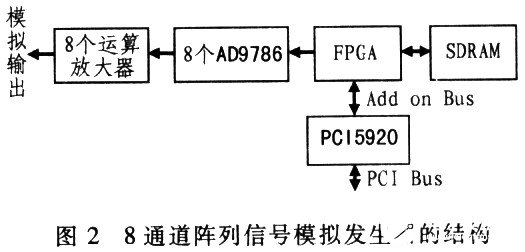

该电路具有以下特征: 16bit分辨率; 可选的2x,4x,8x内插滤波器; 可选的fDAC/2,fDAC4,fDAC/8调制模式; 2个输入数据通道,在具体应用中输入数据通道可以灵活配置; 可选的镜频抑制希尔伯特变换; 直接中频变换; 串行控制接口。 3、AD9786的工作模式 在实际应用中,大部分情况是2个或多个器件应用。在这种AD9786被用来合成多数据通路的场合,确保输入到AD9786中的数据被多个AD9786 同步锁定是十分必要的。同时在复信号的处理应用中,数字相位的调节也是2个AD9786工作所需要的。为了满足数据同步和相位合成的需要,只能有1 个AD9786被配置为主模式器件,为其他配置成从模式的AD9786提供1个参考时钟。在同步使用过程中作为主模式器件输出参考时钟的引脚和从模式的AD9786的DATACLK/PLL_LOCK引脚必须直接相连。同时所有的主模式和从模式AD9786都必须使用同一差分时钟源。 当AD9786被配置成主模式器件时,生成的参考时钟有DATACLK Master和:Modulator Master模 式。在这2种模式下DATACLK/PLL_LOCK引脚都作为时钟输出引脚。AD9786的默认工作模式是 DATACILK Master模式。在该模式下,差分时钟输入 脚(脚5,脚6)作为DAC的采样时钟输入。DATA- CLK/PLL_LOCK引脚被作为同步数据输出时钟引脚使用。其输出是输入差分时钟除以内插倍数。而在 Modulator Master模式下,DATACLK/PLL_LOCK引 脚输出的是1个输入差分时钟经过16倍分频之后的方波。 工作在Modulator Master模式下的AD9786内 部有1个工作在DACCLK时钟频率的拥有16个有限状态的状态机。该状态机产生所有的内部、外部时钟和调制相位。这时DATACLK/PLL_LOCK引脚输出的时钟称为MODCLK。该时钟的上升沿是设置内部状态机状态为零的时刻。 当AD9786工作在Modulator Master模式时,输入数据必须和MODCLK时钟、差分输入CLKIN同步。在8x内插模式下,每8个CLKIN时钟的上升沿锁存1个数据;在4x内插模式下,每4个CLKIN时钟的上升沿锁存1个数据;在2x内插模式下,每2 个CLKIN时钟的上升沿锁存1个数据。为了满足数据建立时间和保持时间的需要,同时也为了数据同步的需要,AD9786提供了1个DATAADJ寄存器用来将MODCLK时钟输出前移或后移1个或几个 DACCLK时钟周期,最大可移动的具体时钟周期数和所选择的内插倍数有关。在Modulator Master模式 下,锁数据的CLKIN时钟时刻固定,输出的MOD- CLK根据所选择的DATAADJ参数而前后移动。 当AD9786被设置为从模式器件时,根据所处工作模式的不同可以分为Modulator Slave模式和 DATACLK Slave模式。在这2种工作模式下DAT- ACLK/PLL_LOCK引脚作为时钟输入脚。当AD9786 工作在Modulator Slave模式时,根据主模式器件生 成的参考时钟MODCLK来设置状态机的零状态从而使得从模式器件的数据锁存和调制相位能够和主模式器件同步。通过AD9786中的MODADJ寄存器设置调制系数来调节AD9786的调制相位,可调的相位数和所选择的调制倍数有关。 和Modulator Master模式的情况相同,在Modu- latm Slave模式下的从模式AD9786的输入数据必 须和差分时钟输入CLKIN以及输入的MODCLK同步。在Modulator Master模式下,输入数据锁存的 CLKIN时刻是不变的,输出的MODCLK时钟前后移动。而在Modulator Slave模式下MODCLK时钟作为 输入是不变的,通过改变DATAADJ寄存器的数值将会改变锁数据的CLKIN锁存数据时刻。在DAT- ACLK Slave模式下,从模式器件使用从DATACLK/ PLL_LOCK输入的时钟作为它们的数据输入时钟。 4、在8通道阵列信号发生器中的应用 实际设计中需要模拟的是8路的阵列信号。根据设计需要,在本阵列信号模拟发生器电路中使用了8个工作在Modulator Slave模式下的AD9786, 同时使用1个Xilinx公司的Spartan IIE FPGA作 为主模式器件。在系统中,主机负责模拟并产生65 536点的周期通信基带信号数据。FPGA主要负责与PCI桥路PCI5920的接口通信以读取主机的命令和来自主机的通信基带信号数据,并将所读取的数据存储在模拟器上的大容量SDRAM中。当系统工作时,FPGA将SDRAM中存储的数据输入到 AD9786并提供1个MODCIJK时钟作为AD9786 的调制同步时钟,同时它还负责对AD9786的控制模式寄存器进行配置。AD9786工作在8x内插模式下,使用80MHz的DACCLK差分时钟,通过设置 MODADJ来改变调制相位,通过DATAADJ来改变数据锁定的时刻以保证多路输人数据之间的同步关系。8通道阵列信号模拟发生器结构框图如图2 所示。

用AD9786设计的多通道阵列信号产生器利用了AD9786高精度、高速、直接中频调制等特性,实践证明能够很好的模拟空间阵列信号,具有较高的精度,较好的灵活性和可靠性。 责任编辑:gt (责任编辑:admin) |