|

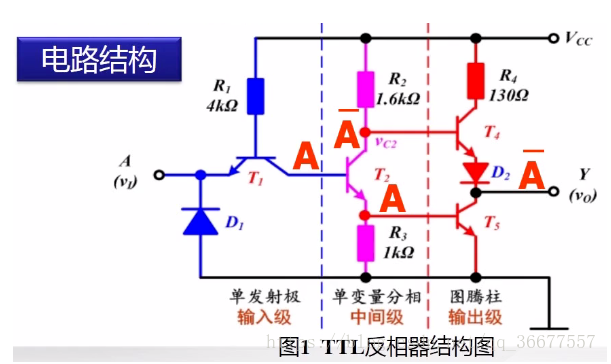

一、TTL集成门电路的结构 1.总体结构

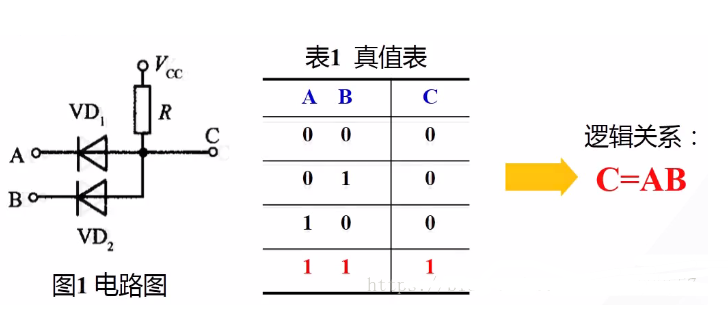

所谓TTL就是transistor transistor logic,就是说是由晶体管和晶体管之间构成电路。 2. TTL集成门电路典型输入级形式 1)二极管与门输入

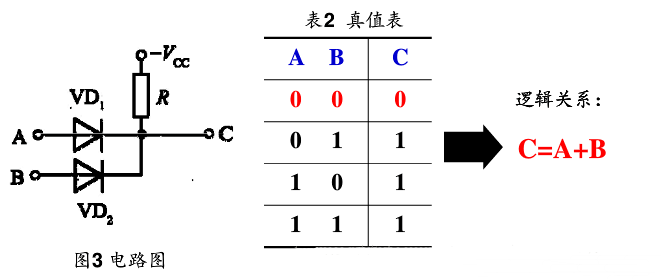

2)二极管或门输入

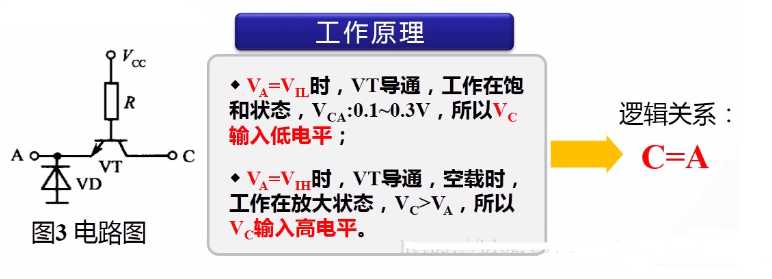

3)单发射级输入

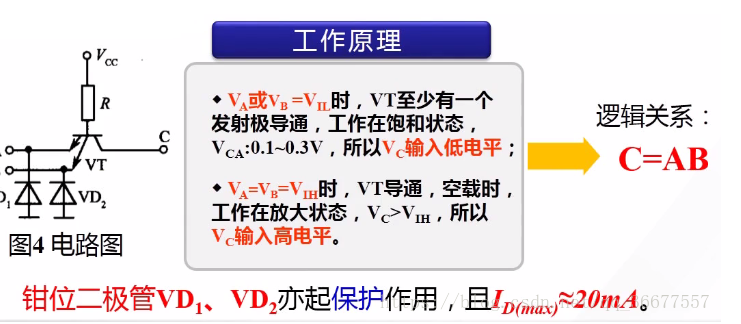

跟随输入的同相关系 钳位二极管VD:左下角并有二极管,既抑制输入端可能出现的负极性干扰脉冲,又可以防止输入电压为负时,VT的发射极电流过大,起保护作用。 电路中经常有干扰信号,当A端出现了一个比较大的负极性脉冲的干扰信号,假设有-20V,那么压降Vcc-(-20V)就有25V了,晶体管的发射结会烧坏。然鹅并联二极管之后,由于二极管电阻很小会迅速导通,将A点电压钳位在-0.7V. 4)多发射级输入

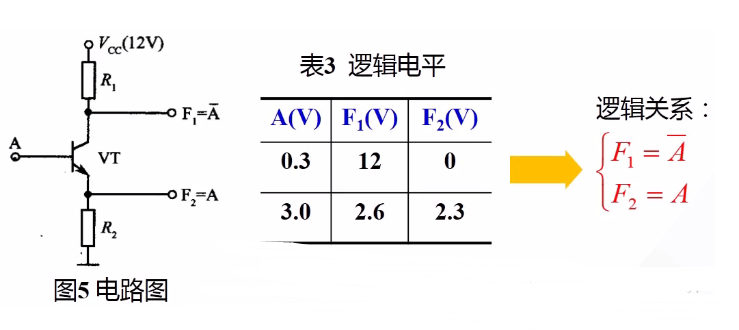

3. TTL集成门电路典型中间级形式 1)单变量分相器

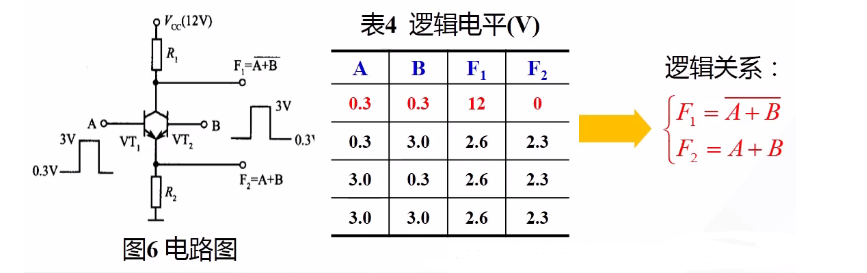

三极管基极输入,发射极和集电极作为输出。 A=0.3V,三极管截止,F1=Vcc=12V,F2=0V. A=3.0V,三极管导通,F2=3.0-0.7=2.3V;F1-F2范围是0.1~0.3V,F1是2.4~2.6V. F1称为反相输出端,F2称为同相输出端。 2)两个变量相或的分相器

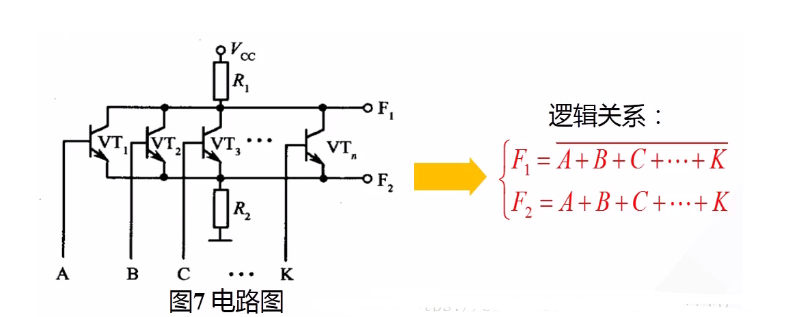

两个三极管的基极分别作为输入,发射极相连,集电极相连作为两个输出 3)多个变量相或的分相器

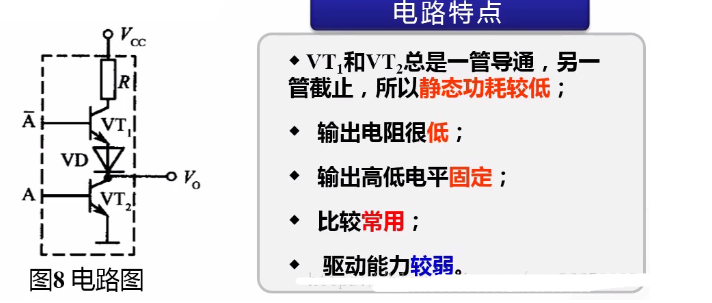

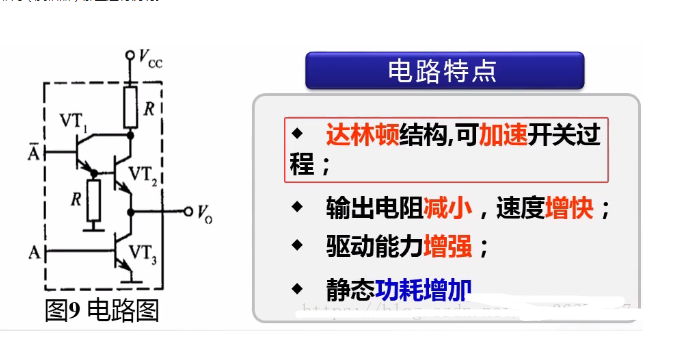

4. TTL集成门电路典型输出级形式 1)图腾柱输出电路

A’为高电平,A为低电平,VT1导通,VT2截止,Vo=A‘-0.7-0.7为高电平; A 为高电平,A’为低电平,VT2导通,饱和导通,VT1截止,Vo是ce间压降,约为0.1~0.3V,为低电平; 所以结论就是 —— 输出和A‘(前提:A’是上面的变量)一致 。 VD这个二极管作用,使得VT1至少要1.4V才能导通,保证了只有一管导通的可靠性,在下面TTL非门(反相器)那里还有说明。 2)图腾柱和复合管输出电路

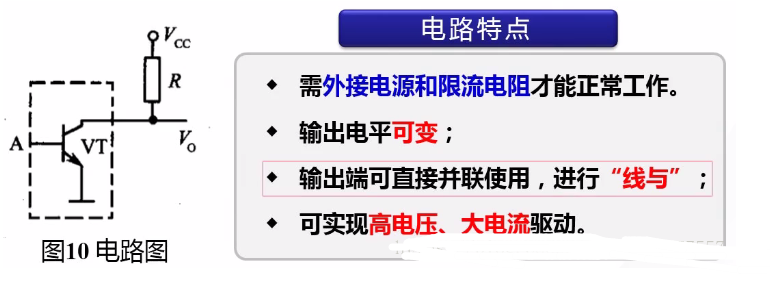

3)集电极开路(OC)门输出电路

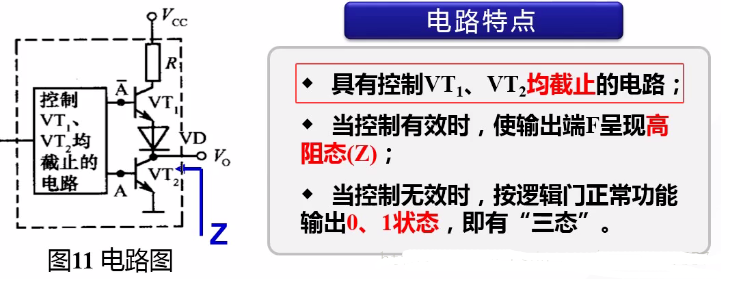

4)三态(TS)门输出电路

二、几种典型的TTL集成复合门电路 1. TTL非门(反相器)

分析:由上面单个的分析(翻到上面回忆一下。..。..。),输入级是跟随的,A是低电平,集电极输出低电平A;A是高电平,集电极输出高电平A。中间级是单变量分相器,下面发射极是同向得到A,上面集电极是反相得到A’。输出级是和上面的变量,也就是和A’保持一致。 D2的作用: 当A为高电平,T2、T5会饱和导通,V(C2)是0.7+(0.1~0.3)=0.8~1.0V,而T5的集电极在0.1~0.3V,如果没有D2就可能导致T4导通,加了D2就等于多了0.7压降才能使T4导通,可靠性增加。

继续分析: Vcc=5V,A=0.2V时,T1导通,T1基极=0.9V,大约有4V的电压加在R1上,电流为1mA,大于基极临界饱和电流,T1是饱和导通。T1的饱和导通会使ce间压降特别小,T1的集电极电压会被钳位在0.3~0.5V之间,而T2至少要1.4V才能导通,所以T2和T5都是截止的。T2截止使得V(C2)在Vcc附近,R2上通过的电流很小,Vcc经过1.4V压降到Vo大概在3.6V。

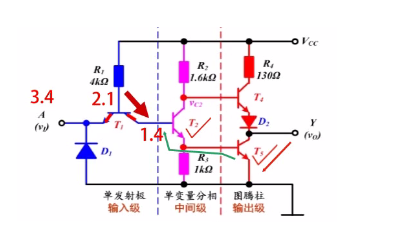

电压传输特性:

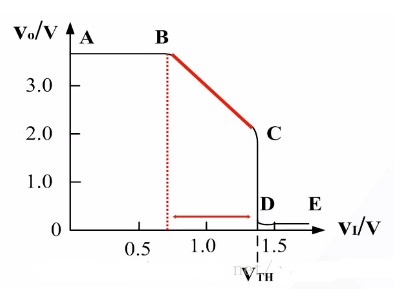

BC段是R2的压降影响的。 噪声容限:在保证输出高、低电平基本不变(或者说变化的大小不超过允许限度)的条件下,允许输入电平有一定的波动范围。 74系列门电路输入高电平和低电平时的噪声容限分别为: V(NH)=VOH(min)-VIH(min)=0.4V; V(NL)= VIL(max)-VOL(max)=0.4V; ps:CMOS反相器的噪声容限可以达到电源电压的45%. 2. TTL集成与非门

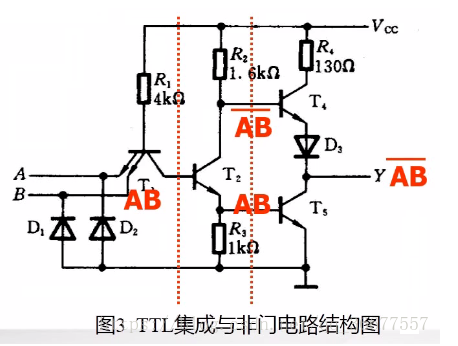

多发射极输入——单变量分相器——图腾柱输出 悬空: A悬空,相当于接了一个无穷大的电阻接地,A、B输入只有B输入有效,AB=(1与B)=B 。 TTL某个引脚悬空,相当于是接了高电平。 输入端接电阻接地: 要关注电阻的阻值大小,Ron开门电阻比较大,相当于接高电平;Roff关门电阻比较小(小于1KΩ),相当于接低电平。 3. TTL集成或非门

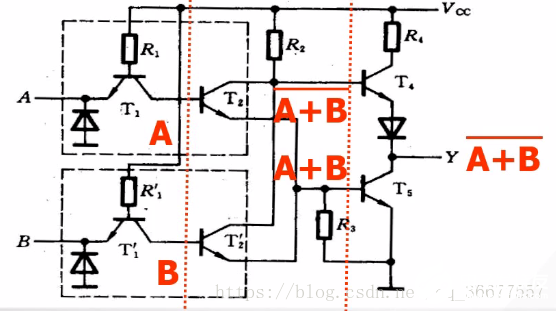

两个单发射极输入——两变量相或的分相器——图腾柱输出 4. TTL集成与或非门

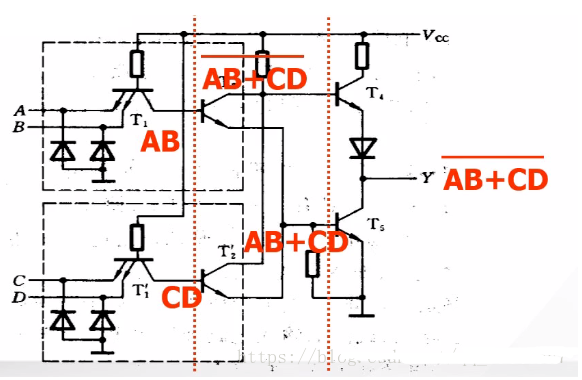

两个独立的双变量输入——两变量相或的分相器——图腾柱输出 5. TTL集成异或门

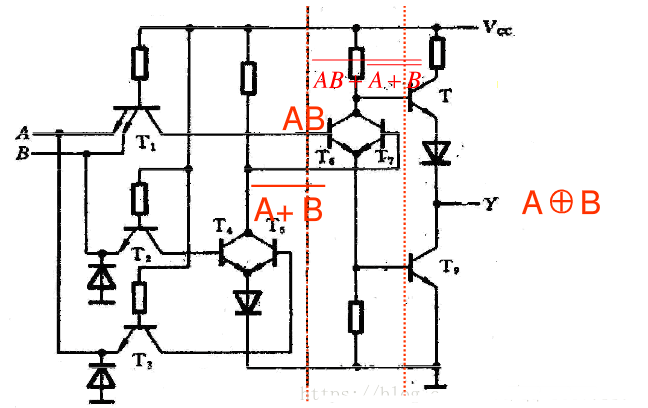

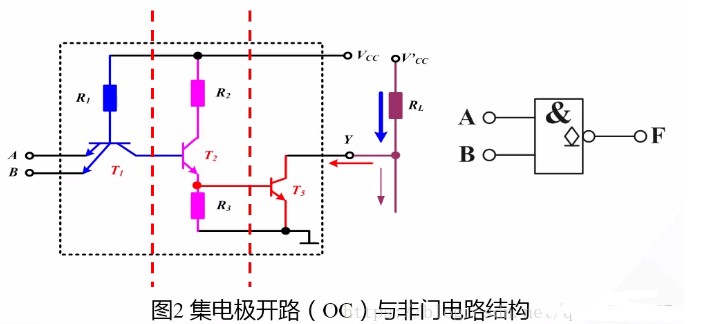

三、集电极开路(OC)门 1. 集电极开路(OC)与非门

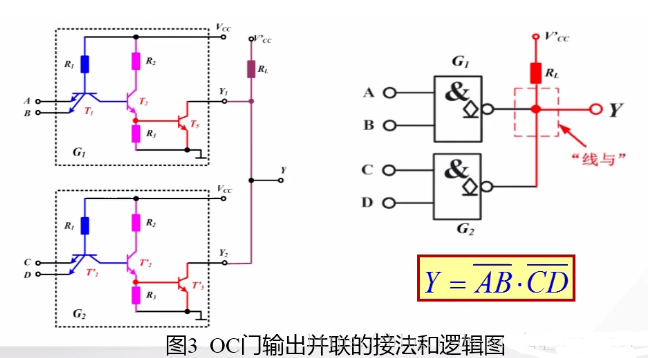

1)功能 输入A、B,输出(A+B)’; 2)分析 A、B中有一个是高电平,T2、T5导通,输出低电平; A、B都是低电平,T2、T5截止,输出高电平。 3)电路工作时需要外加Vcc和限流电阻RL. 当T5导通的时候,不会使电流过大;当T5截止的时候,等效为一个大电阻,电压大部分降在T5上,Y输出为低电平。 注:右边那个菱形下面加一横,代表OC门 2. OC门输出并联使用

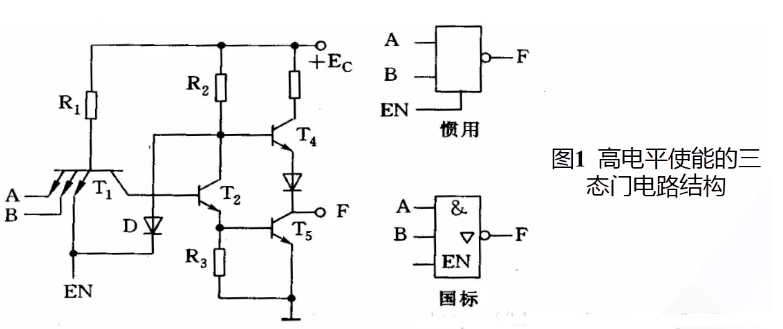

T5的尺寸比较大,可以承受大电流、大电压。 3. 小结OC门的特点 1)工作时需外接负载电阻(RL)和电源(Vcc) 2)可根据要求选择电源,灵活得到下级电路所需电压 3)可将OC门输出端直接并联,进行“线与” 4)有些OC门的输出管设计尺寸比较大,足以承受较大的电流和较高的电压,可直接驱动小型继电器 四、三态(TS)输出门 1. 高电平使能的三态门

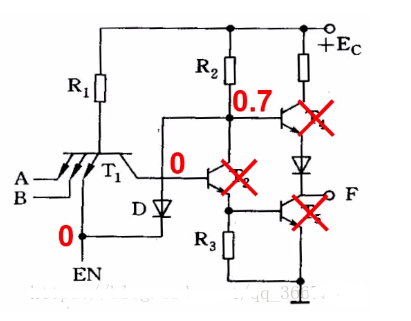

分析: 输入级是三变量的多发射级输入,结果是AB(EN),EN是高电平的时候,A、B有效,就是一般的与非门,也就是所谓的高电平使能。 当EN=0,T2、T5是截止的,T4的基极也被钳位在0.7V左右,由于T4下面还有一个二极管,至少要1.4V才能导通,所以T4也是截止的,这时的等效电阻很大,电路呈现高阻态。

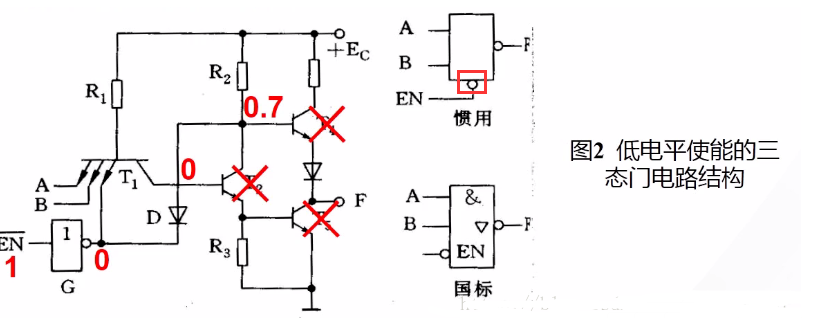

2. 低电平使能的三态门

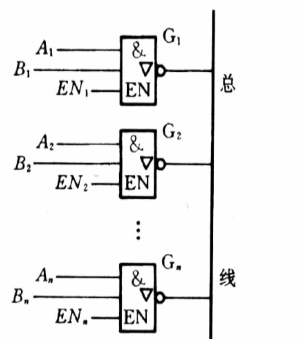

正常工作时,EN 是低电平。 3. 三态门的应用 1)三态输出门接成总线结构

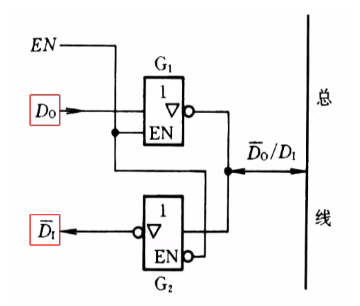

通过控制EN,使数据分时传输,挂载在一条总线上 2)三态输出门实现数据的双向传输

G1高电平使能,G2高电平使能 4. 小结三态门的特点 1)三态:低电平、高电平、高阻态 2)可实现在同一根导线上分时传送若干门电路的输出信号(即接成总线结构) 3)可做成单输入、单输出的总线驱动器 4)还可以实现数据的双向传输等 结束 1. TTL电路一般由输入级、中间级和输出级三级电路组成,其输入级和输出级都采用累了晶体三极管,所以称为晶体管-晶体管逻辑电路。TTL典型电路包括反相器、与非门、或非门、三态(TS)输出门、集电极开路(OC)门等。 2. 研究TTL电路主要是研究其外部特性(即输入与输出之间的逻辑关系)和外部电气特性(包括电压传输特性、输入特性、输出特性、动态特性等)两方面。 3. TTL逻辑电路基本系列为SN54/74系列,为满足提高工作速度和降低功耗的需要,随后相继出现了74H、74J、74S(肖特基)、74LS(低功耗肖特基)、74AS、74ALS、74F等改进系列。目前,TTL电路正朝着高速、低功耗、Bi-MOS工艺方向发展。 PS. CMOS的功耗低,但是不能像TTL那样输出端有有一个较大的电路。 (责任编辑:admin) |