使用达林顿继电器驱动器进行设计时降低 EMI 的

时间:2025-03-10 10:37 来源:[db:来源] 作者:admin 点击:次

|

电磁干扰(EMI)历来是让PCB设计工程师们头疼的一个问题,它威胁着电子设备的安全性、可靠性和稳定性。因此,我们在设计PCB时,需要遵循一定的原则,使电路板的电磁干扰控制在一定的范围内,达到设计要求和标准,提高电路的整体性能。

电磁干扰有传导干扰和辐射干扰两种。传导干扰是指通过导电介质把一个电网络上的信号耦合(干扰)到另一个电网络。辐射干扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络。在高速PCB及系统设计中,高频信号线、集成电路的引脚、各类接插件等都可能成为具有天线特性的辐射干扰源,能发射电磁波并影响其他系统或本系统内其他子系统的正常工作。 我们是否因为 EMI 问题而避免使用多通道继电器驱动器?这个 EMI 问题可以通过增加上升/下降时间来解决,这样到负载的电路板走线就不会像传输线一样起作用。降低输出压摆率将增加上升和下降时间。可以通过添加电阻器 (Rin) 和电容器 (Cint) 来控制驱动器压摆率,从而形成积分器。砰!问题解决了......这是如何做到这一点以及我们会发现的典型结果:

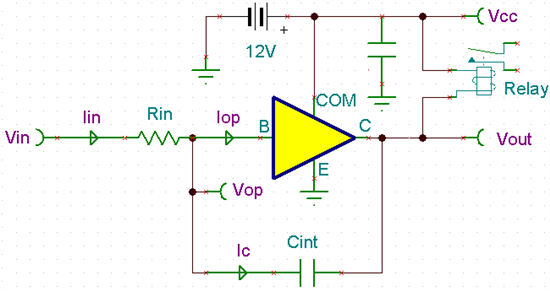

图 1:示意图 第 1 步:根据驱动器的工作点估算电容电流 驱动器输入电压 (Vop) 和输入电流 (Iop) 在输出压摆时间内几乎保持不变。对于输入电阻 (Rin) 的实际值,驱动器输入电流 (Iop) 将远小于电阻电流 (Iin)。因此,电容器电流 (Ic) 可以近似为与输入电流相同。 对于EMI传导部分,重点是充分利用旁路电容器和去耦电容器。旁路电容器(提供交流短路线)必须布置在晶片电源管脚和接地线(平面)上。去耦电容器应放置在电流需求变化较大的地方,以避免因电线阻抗(电感)而从电源和接地线上耦合干扰。当然,磁珠的合理串联可以吸收(转换为热能)。电感器有时也可以用来过滤干扰,但请注意,电感本身也有频率响应范围,包装也决定了其频率响应。以上是一些基本的经验,对于EMI设计,你需要真正了解自己的设计,需要关注哪里,问题会是什么现象,什么是替代方案,需要提前整理。 第 2 步:确定正压摆率和负压摆率 正输出压摆率(输入逻辑低电平)为 (Vop - Vin) / (Rin * Cint),单位为 V/S。负输出压摆率(输入逻辑高电平)为 (Vin - Vop) / (Rin * Cint),单位为 V/S。除以 10 6得到 V/uS 。Iop 和 Vop 随负载和温度而变化。它们还可以因设备而异。由于这些差异,速率控制很好,但精度不高。 (责任编辑:admin) |