带有基于 PCB 的变压器的 SiC MOSFET 隔离栅极驱动器(2)

时间:2025-03-10 10:37 来源:[db:来源] 作者:admin 点击:次

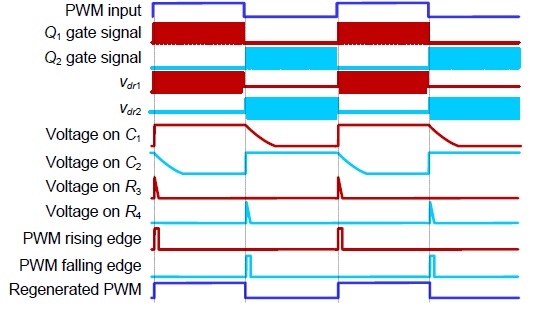

相关波形如图3所示。

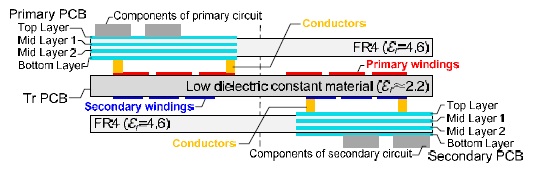

图 3:提议的 GD 的关键波形 变压器 基于PCB的空心变压器的设计,其优点是消除了磁芯损耗和绕组与磁芯之间的潜在绝缘问题,如图4所示。它采用堆叠 PCB 结构,包括初级 PCB、变压器 (Tr)-PCB 和次级 PCB。变压器绕组具有螺旋形状以简化设计。Tr-PCB 板只有两层,初级和次级绕组分别位于顶层和底层。使用此解决方案,绝缘特性完全由 Tr-PCB 板的介电材料(通常为低成本 FR-4)提供。

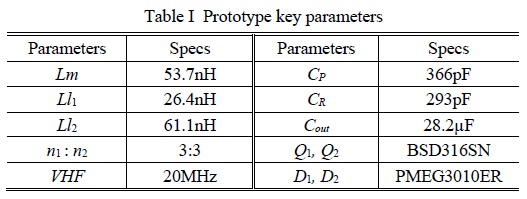

图 4:基于 PCB 的变压器的结构 为了提高介质击穿电压和降低耦合电容,可以使用高抗电强度和低介电常数的材料。作者使用了 Arlon-DiClad-880 材料,其介电常数为 2.2,介电强度大于 45kV/mm。借助 Ansys Q3D 提取器工具确定的模拟耦合电容对于几个变压器约为 5 pF。 带涂层的初级和次级绕组之间的爬电距离高于 30 mm × 2。根据 IEC-61800-5-1-2007 标准,这确保了 15 kV RMS的绝缘电压。 实验结果 图5显示了用于测试的原型的示意图,该原型使用表 I中列出的组件在实验室中构建。

表一:原型中使用的组件列表

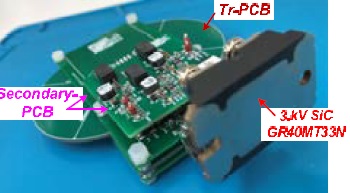

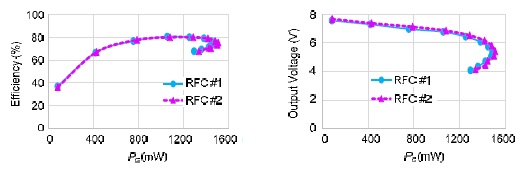

图 5:原型示意图 RFC的最大输出功率在1.5W@17Ω阻性负载下测得,足以驱动3.3kV SiC MOSFET(GR40MT33N)。效率和 RFC 输出电压 (V O ) 的图表如图 6所示。两个 RFC 在整个负载范围 (0.12W-1.5W) 上都保持稳定的输出特性。

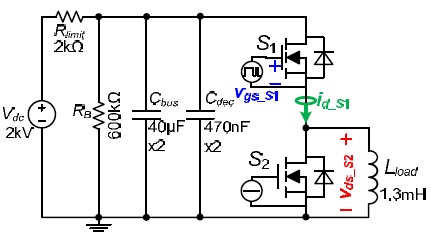

图 6:效率和 RFC 输出电压 此外,还实施了双脉冲测试 (DPT) 来评估提议的 GD 的性能。DPT 试验台的示意图如图 7所示。

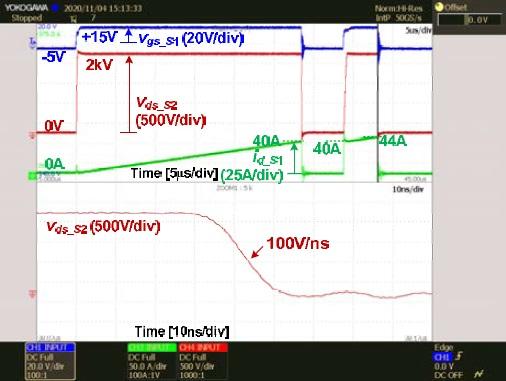

图 7:DPT 测试台示意图 GD 驱动开关S 1,其中需要绝缘电压和对高 dv/dtare 的抗噪性。Vdc=2kV,id_S1,max=44A,Lload=1.3mH,Rgon/Rgoff=2.2Ω/5Ω时的DPT实验波形如图8所示。可以看出,3.3kV SiC达到的最大dv/dt MOSFET 对应于 100V/ns 的安全值。相同的 GD 解决方案也可用于其他高压 SiC MOSFET 器件。  (责任编辑:admin)

(责任编辑:admin) |

- 上一篇:用于改善 EMC 的 PCB 设计的原理介绍

- 下一篇:微步步进电机时电流调节的技巧