|

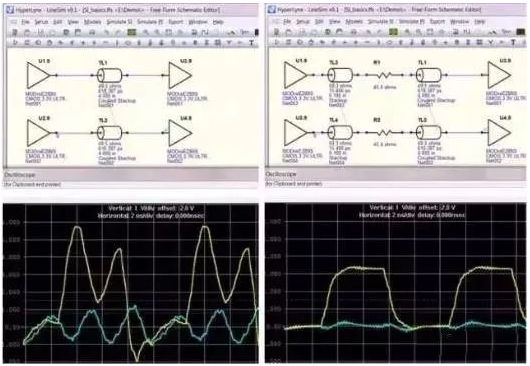

信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。 通常,可以通过添加某种类型的端接以使驱动器的阻抗与传输线的阻抗相匹配来解决这些问题。对于多点分支总线,并非总能匹配阻抗,因此,需要将端接和拓扑的长度变化相结合来控制反射,使得它们不会对信号质量和时序产生不利影响。

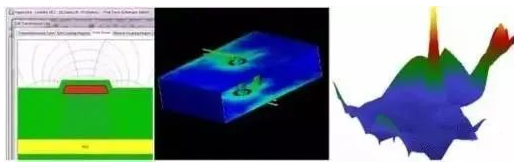

使用信号完整性分析和设计空间探索消除信号质量和串扰问题 可以运行这些相同的仿真,以确定信号经过电路板时的传输时间。电路板时序是系统时序的一个重要组成部分,并受线路长度、其在经过电路板时的传播速度以及接收器中波形形状的影响。由于波形的形状确定了接收的信号穿越逻辑阈值的时间,因此,它对于时序来说是非常重要的。这些仿真通常会驱动走线长度约束的变化。 通常运行的另一个信号完整性仿真是串扰。这涉及多条相互耦合的传输线。随着走线挤进密集的电路板设计,了解它们正在相互耦合多少能量对于消除因串扰产生的错误是非常重要的。这些仿真将推动走线之间的最小间距要求。 在信号完整性中,目标是消除关于信号质量、串扰和定时的问题。所有这些类型的分析都需要相同类型的模型。它们包括驱动器和接收器、芯片封装及电路板互连(由走线及过孔、分立器件和/或连接器组成)的模型。 驱动器和接收器模型包括关于缓冲器阻抗、翻转率和电压摆幅的信息。通常,IBIS 或 SPICE 模型用作缓冲器模型。这些模型与互连模型结合使用来运行仿真,从而确定接收器中的信号情况。互连将主要包括行为类似于传输线的电路板走线。此类传输线具有阻抗、延迟和损耗特性。它们的特性决定了所连接的驱动器和接收器与彼此进行交互的方式。 互连的电磁特性必须使用某种类型的场求解器进行求解,该场求解器通过可与信号完整性仿真器结合使用的电路元件或 S 参数模型来描述其特征。 大多数走线均可建模为一个均匀的二维横截面。该横截面足以计算走线的阻抗特性。阻抗将会影响信号线上接收器中的波形形状。最基本的信号完整性分析包括设置电路板叠层(包括适当的介电层厚度),以及查找正确的走线宽度,以实现一定的走线目标阻抗。 与过孔相比,对走线进行建模会相对比较容易。当对较快的信号进行信号完整性分析时,适当的过孔建模就变得非常重要。通常,千兆位信号需要通过三维场求解器对模型特征进行适当地描述。 这些信号往往是不同的,这使它们的影响相对局部化。穿过过孔的快速、单端信号与配电网络(PDN)进行强有力地交互。从这些过孔返回的电流穿过附近的缝合孔、缝合电容器和/或平面对(组成PDN且需要建模以进行电源完整性分析的相同元器件)。

编辑:黄飞 (责任编辑:admin) |