|

前言 大部分ADC均需要输入信号具有一定的驱动能力,以满足ADC内部采样电路的建立要求。然而在很多应用场景,类如传感器前端等,输入信号驱动能力极弱,因此需要在输入信号和ADC之间使用Buffer来提供ADC需要的驱动能力。Buffer通常用单位增益反馈的运放组成,而运放的增益,带宽影响着经过缓冲器后被ADC所采集的信号的精度,线性度,因此Buffer中运放的设计尤为重要。 除上述两点之外,根据奈奎斯特采样定律,为了防止输入信号被采样后发生混叠,一些应用中会将抗混叠滤波器与Buffer在一起实现,例如在电路中级联一个简单的串联RC组成的抗混叠滤波器。 上述情况均为运放组成的闭环负反馈放大电路,因此在对其中运放设计时主要考虑增益,带宽以及稳定性等指标,其中带宽和稳定性随着运放的反馈系数或者负载电容等在不同情况下的不同使得分析更为复杂一些。 本文对两种情况下运放的速度和稳定性进行浅析。 情况1:驱动器直接驱动ADC

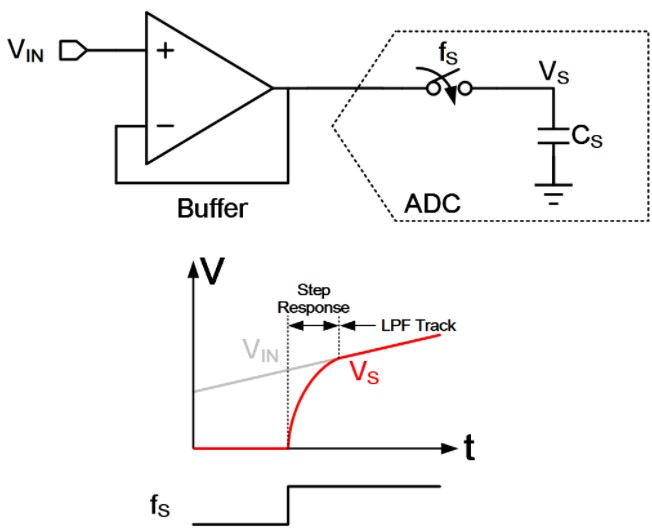

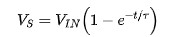

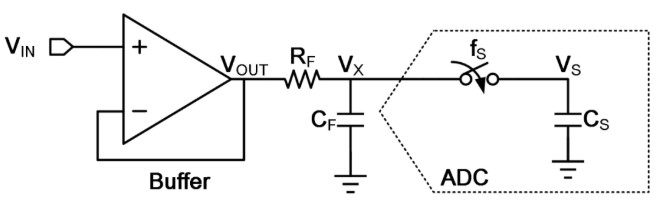

图1 Buffer直接驱动ADC 本文所讨论的第一种情况为Buffer直接驱动ADC,这种应用场景通常在ADC片上集成实现,因为信号输入ADC之前已经经过了抗混叠滤波,因此不需要在驱动器上再进行滤波。这种情况和我们之前的一篇文章中分析开关电容采样的过程类似,忽略采样开关的导通阻抗,运放在每次采样时需要处理两个过程: 开关导通瞬间的阶跃响应过程; 阶跃响应完成之后的低通滤波器跟随过程。 阶跃响应阶段采样电容上的电压随时间的变化可以表示为式(1):

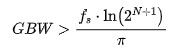

其中,τ为时间常数,即为运放的闭环带宽分之一,由于Buffer为单位增益负反馈,因此闭环带宽即为运放的增益带宽积GBW,τ因此可以表示为1/(2πGBW)。式(1)中t为半个时钟周期,即为1/(2fs),如果要求N位的建立误差,即建立误差小于半个LSB: VIN/(2^(N+1)),那么可以得到运放的GBW和N的关系如式(2):

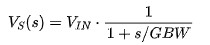

例如,如果设计模数转换的精度为16bit,在留有一定裕度的情况下我们要求经过Buffer的信号有17bit的精度,假如采样时钟为1M,那么根据式(2)可以算出对运放GBW的要求为3.97MHz。 在阶跃响应完成后,Buffer就变成了一个低通滤波器,假设运放为单极点系统,那么该低通滤波器的响应为式(3):

对于该低通滤波器,存在两个要求: 输入信号要在滤波器带宽内,在满足阶跃响应的建立要求后,这一点很容易满足(因为采样时钟频率通常会比信号频率高很多); 该滤波器具有很好的线性度,这一点可以通过将滤波器的带宽设置得足够高或者保证其频率响应不随输入信号变化来实现(参考之前关于开关电容线性度的文章)。 综上,之所以存在上述两个要求,本质上时因为Buffer在同时处理两个信号:输入信号和时钟引起的阶跃信号。后者频率更快,因此通常对Buffer提出了更高的要求。(但也不能一概而论,具体情况需要具体分析)。 情况2:Buffer+抗混叠RC滤波器驱动ADC

图2 Buffer+抗混叠RC滤波器驱动ADC 在一些ADC Buffer设计时,会在Buffer之后级联RC低通滤波器组成抗混叠滤波器,如图2所示。这种情况与情况1的不同为:由于滤波电容CF选取通常远大于ADC的采样电容,因此在采样发生时,运放输出发生的电压变化很小(电压变化的大小取决于CF与CS上的电荷分享),因此运放不需要处理阶跃响应,只需要处理输入信号(将输入信号低通传递至VX处),运放+抗混叠滤波器组合形成的低通滤波器只需要满足带宽大于输入信号的带宽即可。 假设Buffer运放输出阻抗为rout,没有抗混叠滤波时的输出电容为Cload,那么级联抗混叠滤波器后,运放的输出极点从1/(routCload)变为一个极点1/((rout+RF)CF)和一个零点1/(RFCF)。该极点和零点距离很近,因此在考虑运放的频率响应时应考虑二者的抵消作用。例如对一个单级运放,输出极点本身为其主极点,但级联抗混叠滤波后的零极点抵消使得输出极点被抵消,主极点变成了其他寄生高频极点,运放很容易不稳定;而对于一个密勒补偿的两级运放,主极点为第一级输出极点,输出极点通常为第二极点,级联抗混叠滤波后虽然让输出极点变小至低频(由于CF很大),但其被零点抵消,主极点仍为第一级输出极点,而输出极点“消失”,那么运放的稳定性不变或者变得更好。同时,VOUT处的带宽仍为运放本身的带宽。 而信号传递到VX处,除了主极点外,增加了一个极点:1/(RFCF),如果运放主极点远大于增加的极点,那么VX处的带宽由增加的极点决定,即为抗混叠滤波器的带宽。 由上述分析可知,在设计图2电路中的运放时,只需要保证两级运放自身的稳定性且闭环带宽远大于抗混叠滤波器的带宽,那么级联抗混叠滤波器后运放同样稳定,且输入信号的带宽由抗混叠滤波器决定。 总结 本文简单分析了ADC驱动器设计时的速度设计考虑,并针对两种常见的情况进行了单独的分析,希望可以为读者在设计或者选择ADC驱动器时提供一些设计参考。 (责任编辑:admin) |