|

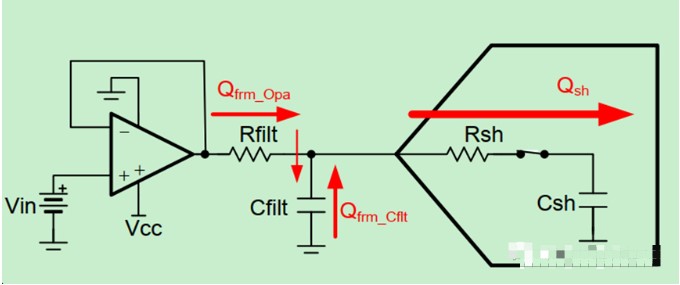

本文是以AD7689的SAR型ADC为例的驱动电路设计,其他类型的SAR 型ADC也是类似的。 首先简单提下,SAR型ADC的驱动电路设计得很随意会出现出现什么问题即它的重要性。上周的文章提过了以理想电压源驱动SAR型ADC时,由于ADC内部采样保持电容的存在,造成了电荷重新分配,引起的电压下冲;如果在采集周期结束前,ADC输入电压仍然没有恢复到1/2 LSB内,由于ADC量化误差的存在小于1/2LSB,也不会提高ADC的精度了。甚至只恢复到输入电压的1/2,那么就会造成很大的误差,这是第一点即RC电路的设计。第二,当输入电压不是理想的电压源,而是其他电路输入比如运放会怎么样呢?如图1。这时候就需要考虑运放的增益带宽积了,设计不当时可能会导致振铃频率过高幅值过大情况。这跟运放的稳定性有关系,运放驱动容性负载时需考虑稳定性。这也是为什么一般运放不会直接驱动ADC,而是要加个RC滤波器的原因之一;如果不加RC滤波器就需要选一个增益带宽积很大的运放,但通常这类运放的输入偏置电流、输入失调电压等参数都比较差成本还很高等。第三,Rfilt过大也会造成非线性误差,这跟电容的容值是电压的函数有关。 总结起来,SAR型ADC的驱动电路如果设计不当,会造成比较大的直流和交流误差,还会出现稳定性问题。因此,SAR型ADC的驱动设计还是需要特别注意的。

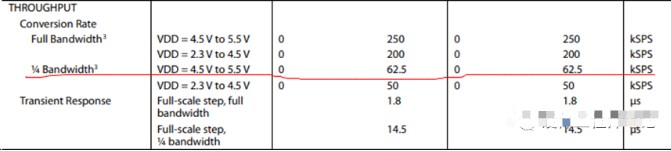

图1,典型的ADC驱动电路 开始AD7689的驱动电路设计。首先从手册中获取这四个参数:Csh,采集周期,参考电压和分辨率。分辨率为16位,参考电压3V,Csh=27pf。采样周期的确认要稍微麻烦些,从手册中得知,采样率有两个选择,全带宽和1/4带宽。如果系统应用时不需要那么高的采样率,那么可以设置在1/4全带宽的,这样RC滤波器的转折频率就可以小一下,能滤除更多的噪声,以及驱动放大器的增益带宽积也不需要那么大了。结合图2、3,我们可以算出来采集周期为13.5us。

图2,采样周期为62.5kSPS即15.3us

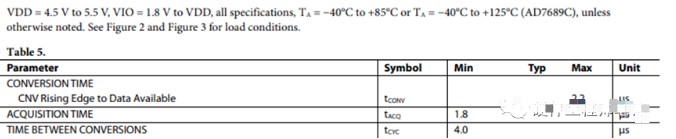

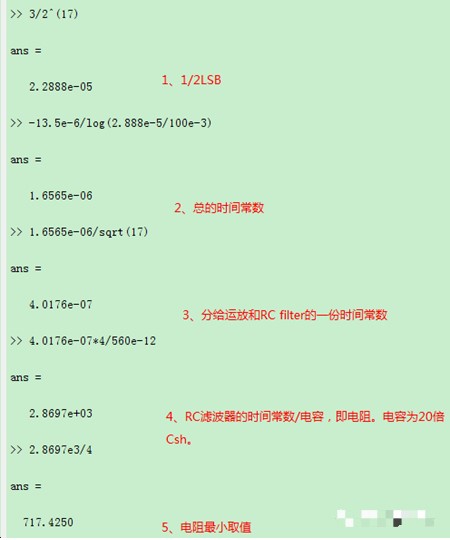

图3,转换周期为1.8us 我们把分辨率为16位,参考电压3V,Csh=27pf,采集周期为13.5us,这四个参考键入TI的Analog Engineer’s Calculator软件中可获得RC滤波器取值范围和运放的增益带宽积。非常遗憾,AD7689应该用ADI的precision ADC driver tool更合适的,但是在这里找不到这颗ADC芯片,而且我也觉得这个工具太“黑盒子”了。结果见图4。但这只是个开始,从这里得到取值范围后,需要用搭建仿真电路迭代仿真,由最好的仿真结果决定RC滤波器具体取值等。但有这个开始已经很好了。

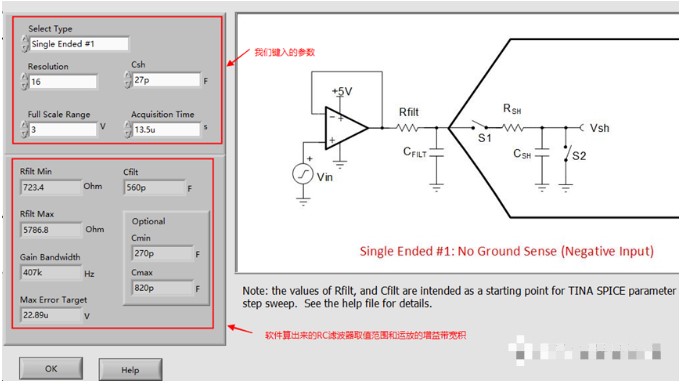

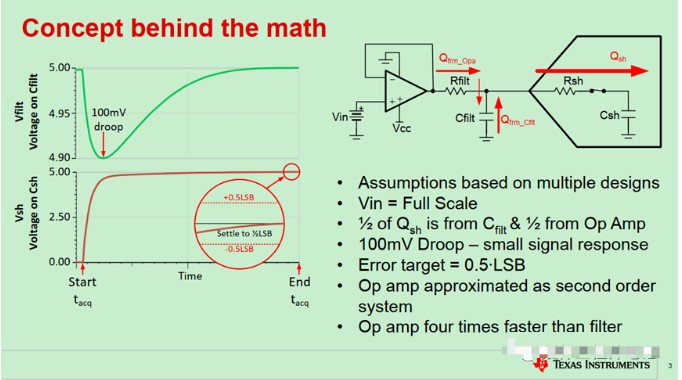

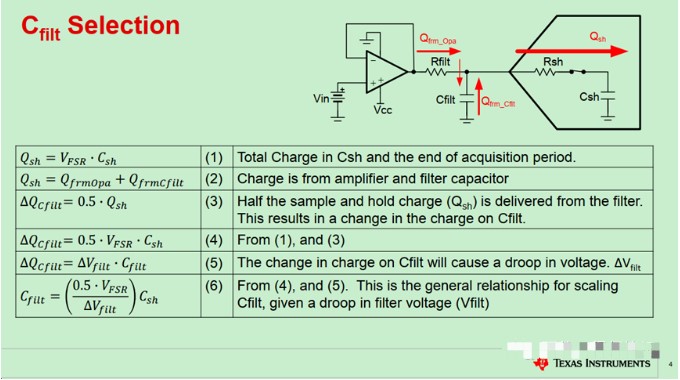

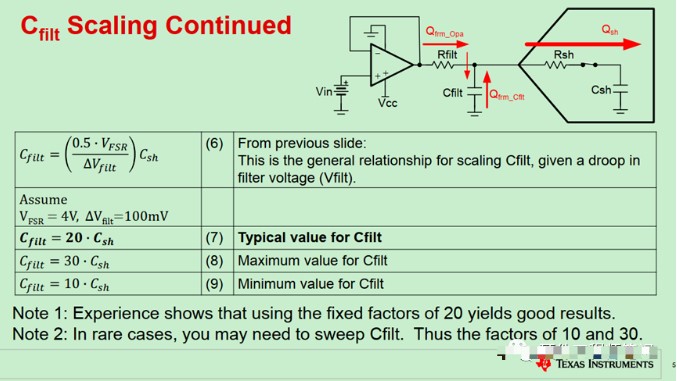

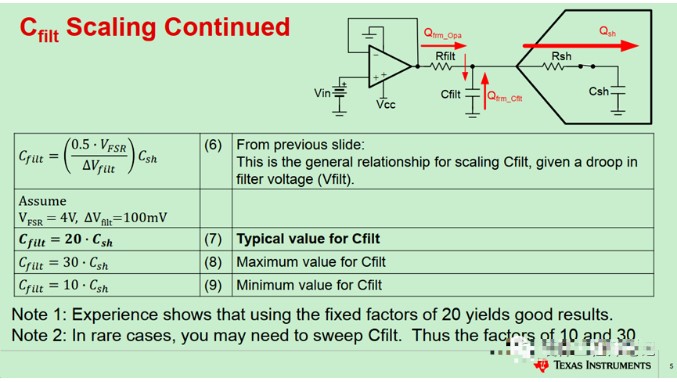

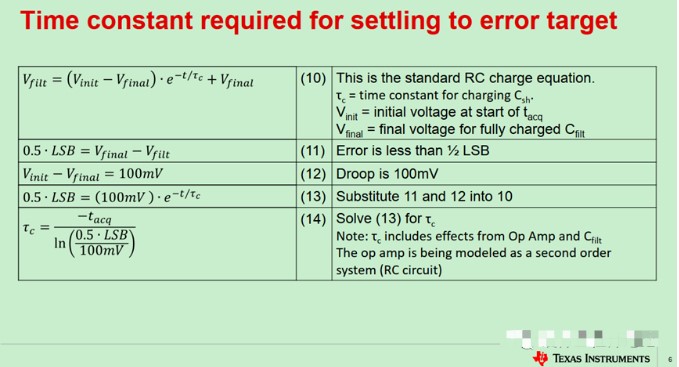

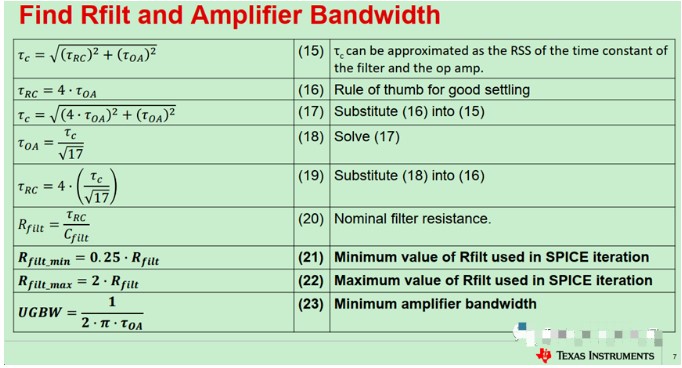

图4 那软件是如何算出来RC滤波器取值范围和运放增益带宽积的呢?“help”选型点进去是有链接的,TI有一个视频讲了软件的算法。我这里只是简单的提下它的假设条件,因为公式跟这几个假设条件关系密切。见图5。这些假设是基于多个设计的测量和仿真结果,结合了大量SAR型ADC选择放大器和电荷桶文献中最佳的方面,从而为优化电路提供了更有条理的方法。第一,Vin是满量程输入即最恶劣情况,通常就是基准源电压;第二,采样保持电容Csh的电荷一半来自Cfilt一半来自运放;第三,下冲电压假设为100mV;第四,目标误差为1/2LSB;第五,运放近似为二阶系统;第六,运放的速度是四倍的滤波器,即滤波器的带宽是运放的四倍。

图5,TI的ADC驱动电路设计软件背后的算法

图6

图7

图8

图9

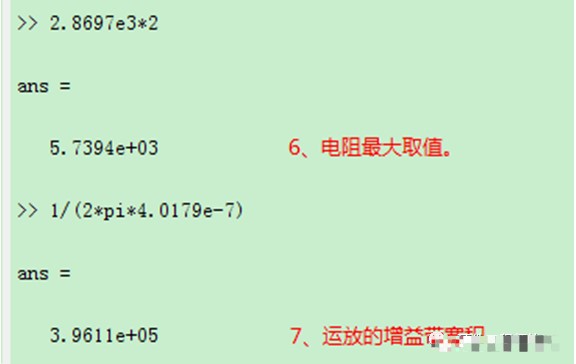

图10 图6到图10是相关公式。我自己用matlab算了下,跟软件的结果也是比较符合的。见图11和图12。但这里有个疑问,它这里算出来的是增益带宽积,因为电路里是跟随器,其实就是运放的带宽。要用的是比如10倍放大电路,那么增益带宽积就需要放大十倍吗?我觉得应该是这个意思吧。其实看过有的文档写道还跟运放的压摆率即大信号带宽有关系,但TI的文档明确提到只跟增益带宽积有关。

图11

图12 (责任编辑:admin) |