|

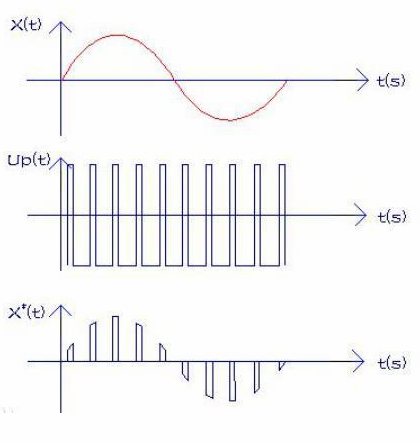

模拟信号转成数字信号需要经过采样-保持-量化-编码这四个过程。下面逐一来分析这四个过程。 采样:采样要满足采样定理,采样定理(香农采样定理或奈奎斯特采样定理)是美国电信工程师H.奈奎斯特在1928年提出的,在数字信号处理领域中,采样定理是连续时间信号(通常称为"模拟信号")和离散时间信号(通常称为"数字信号")之间的基本桥梁。该定理说明采样频率与信号频谱之间的关系,是连续信号离散化的基本依据。它为采样率建立了一个足够的条件,该采样率允许离散采样序列从有限带宽的连续时间信号中捕获所有信息。采样定理又称取样定理、抽样定理。采样定理说明采样频率与信号频谱之间的关系,是连续信号离散化的基本依据。 采样定理的定义为:为了不失真地恢复模拟信号,采样频率应该不小于模拟信号频谱中最高频率的2倍。即fs≥2f max。如图3-3所示。在图3-3中,X(t)是被采样信号,U(p)是采样序列示意,X'(t)是采样之后的信号示意。根据图3-3,不难看出,如果采样频率过低,低于信号的最大频率,那这个信号就不能被还原,甚至会产生混叠,即上一个周期的波形和下一个周期混合到一起去。

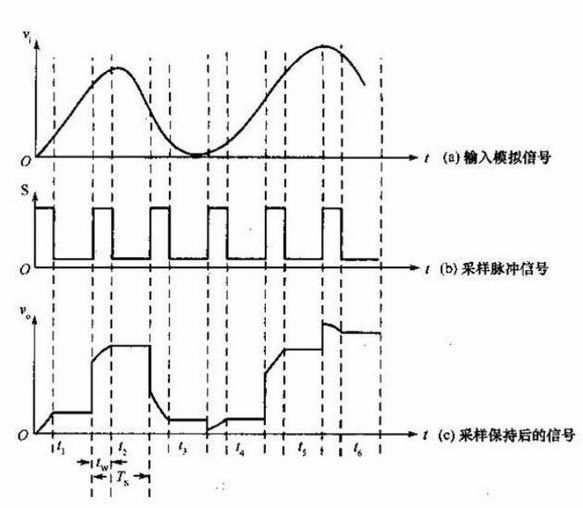

图3-3 采样定理波形示意 保持:采样保持电路由模拟开关、存储元件和缓冲放大器A组成。在采样时刻,加到模拟开关上的数字信号为低电平,此时模拟开关被接通,使存储元件(通常是电容器)两端的电压UB随被采样信号UA变化。当采样间隔终止时,D变为高电平,模拟开关断开,UB则保持在断开瞬间的值不变。缓冲放大器的作用是放大采样信号,它在电路中的连接方式有两种基本类型:一种是将信号先放大再存储,另一是先存储再放大。对理想的采样保持电路,要求开关没有偏移并能随控制信号快速动作,断开的阻抗要无限大,同时还要求存储元件的电压能无延迟地跟踪模拟信号的电压,并可在任意长的时间内保持数值不变。采样保持的波形如图3-4所示。

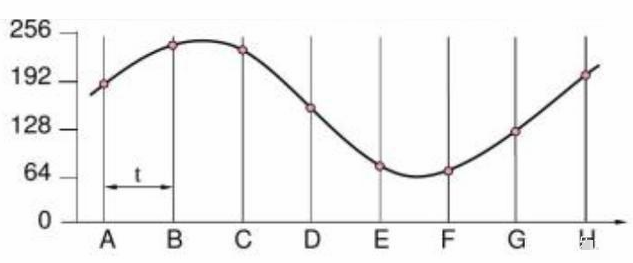

图3-4 采样保持电路的输出随输入变化的波形图 采样后,还需要对采样信号进行量化。为什么量化呢?就算是经过采样,采样点的值依旧是模拟信号本身的值,该多少是多少,没有变化,那么多的值,而且还有可能各不相同,那处理起来同样是很困难啊。为了把无限多个值,变成有限个值,就需要用量化这个技术了。 如果是N位ADC,则把信号幅度值(也就是纵轴)进行2^N次均匀分割,采样点落入哪个区间,就取这个区间所对应的二进制值(N位),这么做就实现了无限个值变成有限个值的目的了。如图3-5所示。

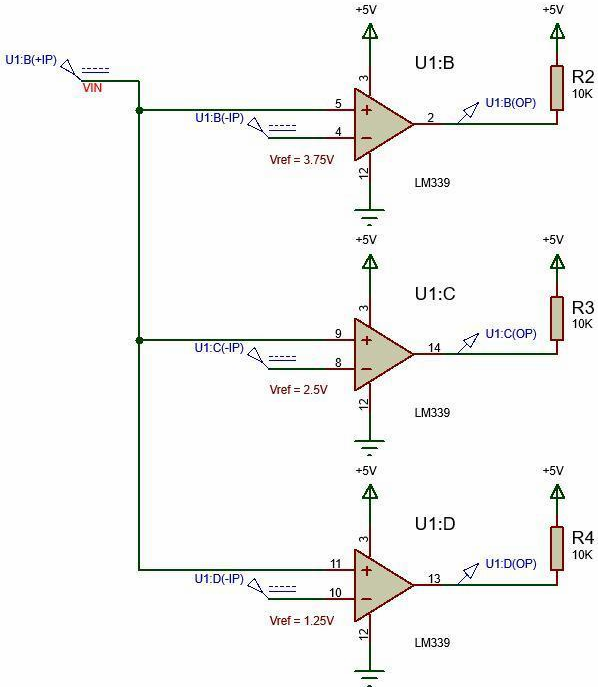

图3-5 量化示意图 上述的采样和量化两个阶段,实际上分别是将时间连续,幅度连续的模拟信号,进时间离散分割,幅度离散分割。到此时,模拟信号实际上还没有变成数字信号,只是变成了在时间上和幅度上离散的信号,而正真数字化是在编码阶段进行的。 编码:编码实际上是将量化电路输出的状态转成特定的二进制编码,进行输出,这个阶段由于AD芯片的不同,输出的编码格式可能有区别。 再来看量化电路,量化电路实际上是将一个电压进行2^N次分割的电路。2^N次分割,这个数量可能有点多,不利于分析。先来看一个简化模型,如果要将一个电压信号量化成大于2.5V和小于等于2.5V的两个状态,应该怎么做?这里想到了比较器电路,只要将比较器的反向参考电压设置为2.5V,那么当输入电压大于2.5V时,比较器输出高电平,低于2.5V比较器输出低电平。虽然量化的状态只有两种,但实际上确实是实现了量化的目的。那么请再思考一下,如果要将5V量化成4种状态,以1.25V为一个量化档位,那该怎么做呢?那就需要用到三个比较器,并且分别设置不同的参考电压。如图3-6所示。

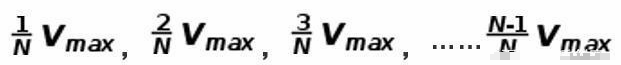

图3-6 四状态量化电路 分析图3-6的电路,我们不难得出输入与输出的状态。 由此再来做个思想实验,假设有N个比较器单元,每个比较器单元的参考电压为

那就可以将输入电压分成N种状态,即量化N个值,以上就是一种早期的并行比较AD的原理。 Vmax即为此ADC的参考电压。 量化电路其实是对连续的模拟信号在幅度维度上的离散化过程,一个量化电路是ADC内部最核心的部分,其实现原理决定了这个ADC的类型。以上是并行比较ADC的原理,并行比较型A/D转换器由电阻分压器、电压比较器、数码寄存器及编码器4个部分组成。这种A/D转换器最大的优点是转换速度快,其转换时间只受电路传输延迟时间的限制,最快能达到低于20ns。缺点是随着输出二进制位数的增加,器件数目按几何级数增加。一个n位的转换器,需要2n-1个比较器。例如,n=8时,需要2^8-1=255个比较器。因此,制造高分辨率的集成并行A/D转换器受到一定限制。显然,这种类型的A/D转换器适用于要求转换速度高、但分辨率较低的场合。 除并行ADC以外,还有非常多种类的ADC,如逐次逼近型AD,双积分型AD,压频转换型AD,这些AD在后面用到时再来详细分析其原理及特性参数。 (责任编辑:admin) |