|

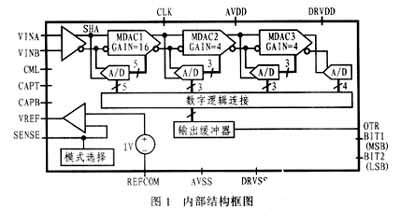

1、引言 AD9224是美国AD公司生产的一种12位、40MSPS高性能模数转换器。它具有片内高性能采样保持放大器和电压参考。在单一+5V电源下,它的功耗,仅有376mW,信噪比与失真度为±0.7dB。且具有信号溢出指示位,并可直接以二进制形式输出数据。AD9224采用多级差动流水线式结构对输出错误进行逻辑纠正,以保证在整个工作温度范围内不失码。AD9224的接口十分方便,可广泛应用在图象、通信系统以及医疗超声波设备中。 2、 内部结构与引脚说明 AD9224是一种高性能、单一电源供电的12位ADC,其内部结构框图如图1所示。

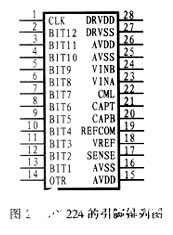

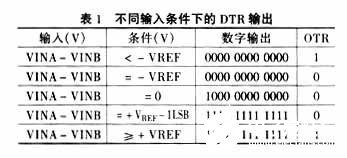

AD9224的模拟输入范围非常灵活,可以是DC或AC耦合的单端或差分输入。AD9224采用四级流水线式结构,并由一个宽频输入采样保持放大器来实现高效经济的CMOS流程。它的最后一级只包含一个闪烁式A/D,而其它三级都包含有连接到比较放大器MDAC的低分辨率闪烁式A/D。因而可用残余放大器把重构的DAC输出和闪烁式A/D之间的差别放大以用于流水线的下一级,每一级中冗余的一位用于错误的数字纠正。流水线式结构在同样的流水线延迟与等待时间条件下可以有更大的通过率,也就是说当转换器在每个时钟周期之中能扑捉一个新的采样输入时,转换的全部完成和数据输出实际上花费了三个时钟周期。将数据溢出标志位(OTR)及数字输出锁入输出缓冲器可用来驱动输出管脚。图2为AD9224的引脚图,各引脚功能说明如下: 1(CLK):时钟输入; 2(BIT12):数据输出最低位LSB; 3~12(BIT11~2):数据输出; 13(BIT1):数据输出最高位MSB; 14(OTR):数据溢出标志位; 15、26(AVDD):+5V模拟电源; 16、25(AVSS):模拟地; 17(SENSE):参考选择; 18(VREF):输入参考选择; 19(REFCOM):通用参考(AVSS); 20、21(CAPT、CAPB):减噪管脚; 22(CML):共模方式; 23(VINA):模拟输入(同相端); 24(VINB):模拟输入(反相端)。 当输入超出输入范围时,OTR位的相应输出结果如表1所列。

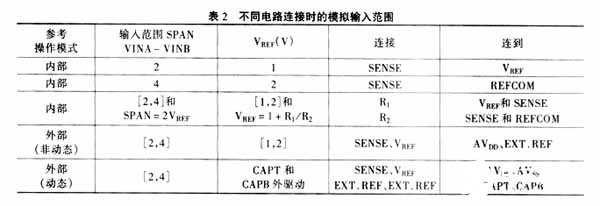

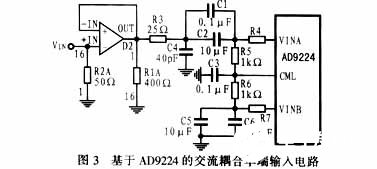

3、 典型应用 3.1 模拟输入范围 AD9224可以在内部参考与外部参考方式下采用不同的电路设计来获得灵活的模拟输入范围。其不同电路连接时的模拟输入范围见表2所列。 3.2 模拟输入的驱动电路 AD9224的高度灵活的输入结构使它可以与单端或差分输入电路接口。其输入范围可参照表2。操作的最优模式、模拟输入的范围以及相关接口电路应由特定应用的需要来决定。其直流耦合单端输入多应用于数据采集和成像技术的场合。同时在许多通讯应用中,为进行正确的检波,也需要直流耦合输入方式。图3是一个AD9224应用于交流耦合的单端输入典型电路。

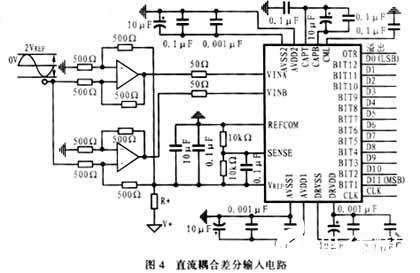

另外,单端操作往往受驱动放大器的限制。在单端直流耦合应用中,当输出接近正的输出电压限制时,往往不能保持其低失真率。因此高性能直流耦合的输入方式经常要用到单端—差分电路。而单端操作则需要VINA与输入信号源AC或DC耦合,同时 VINB管脚则必须被偏置到适当的电压。如果将VINA、VINB的位置颠倒,则很容易产生信号的翻转。VIN的输入范围比较灵活,由于VINA、 VINB及VCML与VREF相独立,因此VREF可以被短接或重构以获取2~4V的输入范围。连接到CML上的对称的R—C网络可使AD9224有效地抑制电源偏差及噪声。其中C1、C2的值依赖于电阻R的大小,C1、C2一般选用0.1μF的陶瓷电容和10μF的钽电容相并联,以便在宽频条件下保持低阻抗时获取一个低截止点的频率。RS对缓冲放大器和AD输入起了孤立作用。 差分模式可在宽频条件下提供最优的THD(总谐波失真)和SFDR(无杂散信号动态范围)性能(相对于单端输入方式),这在输入频率接近或远离 Nyquist频率(fin>Fs/2)时尤为显著,一般可用于大多数需要基于光谱应用的场合。差分方式要求VINA和VINB对称驱动,也就是说两个相同输入信号在通过了连接到VINA、VINB的驱动电路以后,其相位必须保持一致。AD9224的差分方式有如下优点: (1)信号摆幅更小,因此很容易达到对输入信号的线形要求; (2)由于信号摆幅更小,因此允许使用已另外被净空高度限制强制的放大器; (3)减少了偶次谐波分量; (4)提高了对噪音的抗干扰能力。

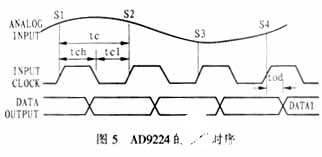

图4所示电路是一种直流耦合差分输入的理想模式。在这种模式下,直流输入将上升到关于参考电压对称摆动的点上。R+是一个可选电阻,当需要的参考驱动较多时,它可以产生所需的电流。在应用DC耦合的场合,如果需要最优失真性能,图4所示的电路应当是最佳选择。这个电路是把两个放大器配置为一个对称单元以形成差分放大器。放大器的差分驱动电路可以把一个以地为参考的2V的单端信号转换为一个以AD的VREF管脚电压为中心的4V的差分信号。单端输入信号接到不同放大器的两个相反的输入上可以驱动差分放大器,放大器可选用双通道放大器AD8056。通常为保护AD9224不受过电压的影响,应当在放大器的输出端和AD的输入之间加一个接地二极管。如果放大器和AD9224用同样的正电源,那么,AD就不会受到过电压的影响。 在不需要直流耦合的系统中,用一个有中间抽头的RF变压器对AD9224而言是产生差分输入的最好方法。使用RF变压器相对于其它方法具有很多的优越性,它对偶次失真分量和共模噪声干扰有很好的抑制作用。同时,RF变压器还对信号源和AD具有一定的隔离作用。AD9224的采样时序如图5所示。

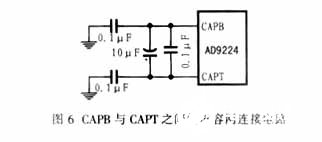

A/D对模拟输入的采样是在时钟输入的上升沿进行的,时钟为高时为保持时间,时钟为低时,输入SHA处于采样模式。如果过度的时钟抖动或系统干扰恰巧发生在时钟的上升沿之前,那么输入SHA有可能得到的是错误的数值。在设计时应当尽量避免这种情况的发生。当使用内部或外部参考方式时,还应当在CAPT与 CAPB之间加一个电容网,如图6所示。该电容网的作用有三个:其一是与内部参考放大器A2一起在大频率范围下提供一个低阻抗源以驱动A/D内部电路。其二是提供A2需要的补偿。其三是限制由参考电源产生的噪声干扰。

另外,为减少高频干扰,在制作电路板时应尽量采用四层板,在中间加上地线层和电源层。另外,由于采样时钟的相位抖动会对AD产生相当于模拟输入正弦波所产生的影响,而时钟输入对AD9224来说相当于一个模拟输入,因此应当尽量选择低抖动晶体振荡器。建议采用将80MHz的时钟分频以获得40MHz时钟信号的方法,并将时钟电路与系统模拟电路、数字电路相隔离,以防止其产生噪声。 责任编辑:gt (责任编辑:admin) |