|

1、概述 ADS1202是一种高精度、80dB动态范围的Δ-∑调节器,其工作电源为+5V。该芯片的差分输入端可直接与传感器或低电平信号相连,并具有合适的数字滤波器和调制速率,可以完成16-bit模数变换(A/D),而且不会遗漏代码。在调节速率为10MHz、数字滤波器带宽为10kHz情况下,该器件可保持12bit的有效分辨率。ADS1202适合用于中等分辨率的测量,其应用领域包括:电机电枢电流测量、通用电流测量、精密转换测量、工业过程控制、重量测量、印刷和便携仪器、压力传感器测量等。 2、主要特性及内部结构 ADS1202是单通道、2阶、CMOS模拟调节器,主要特性如下: *具有16bit分辨率; *具有13bit线性度; *具有分辨率/速度交替切换功能:10bit有效分辨率时具有20μs的信号延迟;12bit有效分辨率时具有77μs的信号延迟; *使用5V单电源是的输入范围为±250mV; *增益误差为2%; *具有四种不同方式的串行接口; *可由分解相位或曼彻斯特译码实现成对的二进制译码,适用于一线接口连接。 ADS1202采用8脚TSSOP封装,其外形和管脚排列图1所示,各管脚的功能如表1所列,由于ESD可能造成器件损坏,故在使用时要采取适当的防范措施。

表1 管脚功能

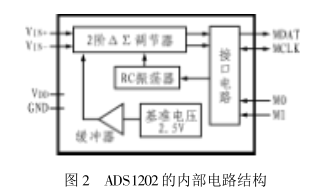

ADS1202的内部电路结构如图2所示,从图中可以看出:该芯片由2阶Δ-∑调节器、20MHz的RC振荡器、接口电路、2.5基准电压源以及一个缓冲器组成。应用时,芯片的工作电压不允许超过6V,数字输入电压范围:GND-0.3V~VDD+0.3V,模拟输入电压范围:GND-0.4V~VDD+0.3V,芯片的功耗为0.25W。 3、工作原理 ADS1202用一个用关电容电路来完成差分模拟输入,这个开关电容可实现2阶调节过程,它可将输入信号数字经为一个1-bit数字流。取样时钟信号(MCLK)提供开关电流网络,而调帛时钟信号用于A/D变换过程,也作为输出的数据帧时钟,时钟源可位于芯片内部也可位于芯片外部。时钟的差频允许随着解决方案和信号带宽变化。模拟输入信号被调节器连续取样并与内部基准电压进行比较。数字流出现在变换器的输出端,它精确地表示了模拟输入电压随时间的变化情况。

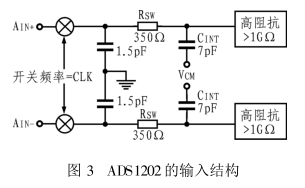

3.1 模拟输入 ADS1202的模拟输入完成基于微分调节器结构。这个输入级可实现低系统噪音、高共模抑帛比(90dB)和极佳的电源抑制比。模拟输入端的输入阻抗由输入电容和调节器的时钟频率决定,调节器的时钟频率也是调节器的取样频率。ADS1202的基本输入结构如图3所示,输入阻抗和调节器时钟频率之间的关系是: AIN(Ω)=10 12/7fMCLK(MHz)

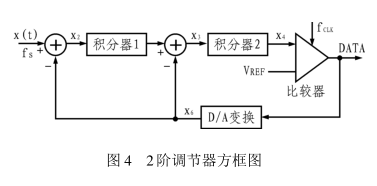

设计中应考虑输入阻抗的影响,由于输入级的源极阻抗很高。因此,信号经过这个外部源极阻抗时将有一部分损失。对ADS1202的模拟输入信号有两个限制,一是决不允许进出模拟输入端的电流超过10mA。二是绝对输入电压要保持在规定的范围内,如果输入电压超过了此限制,变换器前端的保护二极管将导通。此外,把加到任一输入端上的电压维持在规定的-320mV~+320mV范围内时,可确保器件的线性度。 3.2 调节器 在以方式3工作时,调节器的取样频率(CLK)范围在几MHz~12MHz之间。根据时钟应用的要求可以减小MCLK频率,但外部的MCLK必需为调节器频率的两倍。调帛技术基于2阶、充电平衡A/D变换器,其设计构想如图4所示。1bit数据变换器(DAC)的模拟输入电压和输出电压被积分后,在X2和X3处提供了一个模拟电压。这一模拟电压出现在他们各自的积分器上,这些积分的输出以正或负方向变化。当X4处的信号值等于比较器的基准电压时,比较器的输出从负变为正或从正变为负由它的初始状态决定。当比较器的输出值从高变为低时,1bit DAC对下一个时钟脉冲的响应由X6处的模拟输出电压充电决定,促使积分相应的方向进行。调节器对积分器前端的反馈将迫使积分器输出端的值去跟踪输入的平均值。

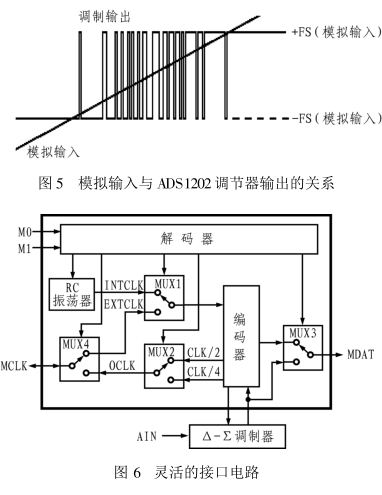

3.3 数字输出 当一个外部时钟提供给MCLK时,它被用来作为芯片的系统时钟,也可作为数据输出的帧时钟。调节器输出端的数据是一个串行流,可通过MDAT管脚在MCLK的下降沿读取。理论上,0V的输入差分信号将产生一连串1和0,其中50%的时间是高电平,50%的时间是低电平。而256mV的差分输入信号将产生一连串1和0,其中80%的时间是高电平;相应的,-256mV的差分输入信号以及产生的一串1和0中,有20%的时间是高电平,输入电压与输出调制信号的关系如图5所示。 3.4 数字接口电路 使用加到调节器的时钟信号(CLK)对与Δ-∑调节器输入端相连的模拟信号进行变换,以从Δ-∑调节器输出数据。大多数应用中,将Δ-∑调节器和DSP或单片机直接相连以提供两个标准信号。MDAT和MCLK信号提供了最简易的连接方法,如果要减少连线的数量,两个信号有时不是最理想的解决办法。 在精确取样瞬间,接收器、DSP或其它控制设备必须对来自调节器的输出数据信号进行取样。要做到这一点,必须对接收器的时钟信号进行取样,以便与发送器的时钟信号同步。而Δ-∑调节器时钟信号、接收器、滤波器、以及时钟必须同步。可用三种方式来获得这种同步:第一种方式是用Δ-∑调节器和滤波器接收来自主时钟的时钟信号;第二种方式是由Δ-∑调节器发送与数字信号在一起时钟信号;第三种方式是用滤波器获得来自接收波形本身的时钟信号。最佳的解决方案是使用带有灵活接口的Δ-∑调节器ADS1202,它在输出线MCLK和MDAT上可能提供灵活的输出形式,因此适用于不同的工作方式。可用控制信号管脚M0和M1来选择提供的信号类型。 3.5 灵活的接口电路 ADS1202灵活的接口电路如图6所示。控制信号M0和M1进入解调器,解调输入码并选择所需的工作方式。来自解码器的五个解码信号分别控制RC振荡器、多路复用器MUX1、MUX2、MUX3以有MUX4。当使用内部RC振荡器时,来自解码器的控制信号可控制RC振荡器。同时,MUX1用INTCLK信号作MUX1输出信号的信号源,被送至编码产生器。如果使用外部时钟,则来自解码器的控制信号将使内部的RC振荡器禁用,并确定MUX1的位置。以便于EXTCLK提供MUX1的输出信号作为编码产生器的输入。

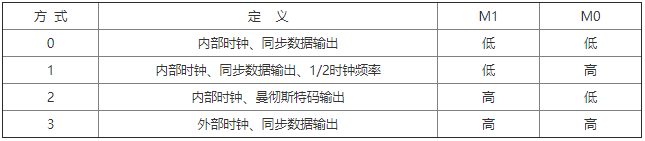

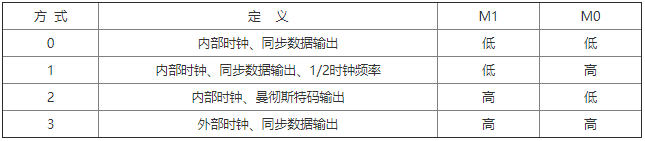

MUX2可用于选择输出时钟OCLK。设计时,可使用来自解码器的控制信号控制输出时钟。本设计中的两个信号均来自编码产生器,其中一个是一半的时钟频率(CLK/2),另一个是四分之一的时钟频率(CLK/4),这两个时钟即可用作MUX2的输入时钟信号。在OCLK信号上,根据CLK/2或CLK/4入时钟信号。在OCLK信号上,根据CLK/2和CLK/4控制信号将选择两种不同的输出方式。编码产生器接收来自MUX1的时钟信号并把产生的Δ-∑调制时钟分成CLK/2和CLK/4时钟。同时,来自Δ-∑调节器的连续的数据串被编码器精心处理,以产生成对的二进制码,然后由编码器输出到MUX3。 MUX3用于选择输出bit连续数据MDAT的来自。来自解码器的控制信号控制MDAT的来源。进入MUX3的两个信号一个直接来自于Δ-∑调节器,另一个来自于编码器。 解码器的控制信号可以对MDAT信号选择两种不同的输出方式:即Δ-∑调帛器的一位连续数据,或相同信号的成对二进制码。来自解码器的最后一个控制信号用于控制MUX4,MUX2则用于选择输入或输出时钟、MCLK信号。解码器的控制信号控制着时钟的方向,从MUX2进入MUX4的一个信号作为时钟信号OCLK,另一个信号离开MUX4,并提供一个输入给MUX1作为外部时钟EXTCLK。来自解码器的控制信号MCLK的方式,有两种:可以选择两种不同的方式,一种是内部时钟信号的输出,另一种是外部时钟信号的输入。使用五个控制信号的解码电路,可通过多路复用器设定理想的工作方式。 3.6 工作方式的设置 ADS1202有四种工作方式可供选择,具体选哪一种由管脚M0和M1来决定,其选择方式如表2所示。 表2 工作方式的选择

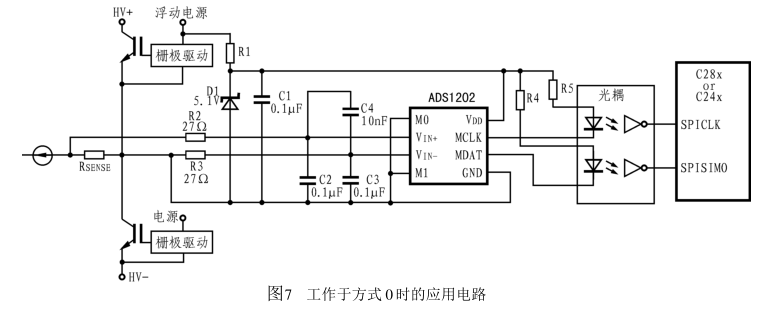

4、用设计实例 ADS1202以方式0工作时的典型应用电路如图7所示。该电路通过分流电阻RSENSE来测量电机的电枢电流。为了得到更好的性能,信号先要被滤波。R2和C2用于滤除同相输入端上的噪声,R3和C3用于滤除后相输入端上的噪声,而C4与R2、R3相结合则可用来滤除共模输入噪声。在这个电路中,分流电阻经三条线与ADS1202相连。

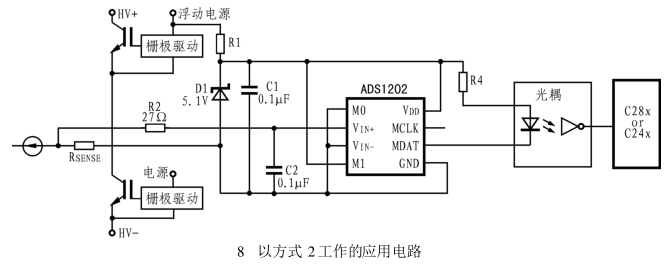

芯片的工作电源取自于IGBT上面的驱动电源,为了对电源滤波,建议连接一个0.1μF的去耦电容,如要更好的滤波,可以另外再加一个1μ~10μF的电解电容。ADS1202的工作方式控制管脚M0和M1都要接低电平。两个输出信号MCLK和MDAT都要直接与光电耦合器相连,因为输出级有能力去提供和吸入相同的电流,所以连接光电耦合器可以传输正向或反向信号,而不需要给光耦二极管并联放电电阻,原因是输入驱动器有能力保持LED二极管输出放电。数字信号处理芯片(DSP)C28X或C24X可以直接连到光耦的两个通道的输出端,在这个电路中,到达C28X或C24X的信号是标准的Δ-∑调制信号,并直接与SPICLK和SPISMO引脚相连。Δ-∑变换器不需要有串行数据的字同步。 当需要减少元件时,ADS1202以方式2工作时的电路如图8所示。图中,管脚M1为高电平,而M0为低电平,仅同相输入信号要被滤波,R2和C2用于滤除同相输入端上的噪声,反相输入端直接与GND管脚相连。来自ADS1202的输出信号是曼彻斯特码,在这种情况下仅传输一路信号,因此可用一个光电耦合器通道来代替两个通道。

5 、设计印刷电路板时应注意的问题 5.1 工作电源 在设计印刷电路板时,通常仅需要VDD一个电源,如果在线路板上有分开的模拟和数字电源,那么将ADS1202电源同模拟电源相连较为适宜。控制噪音的另一种方法是在ADS1202电源上连接一个10Ω电阻。在ADS1202的电源管脚上连接一个电阻和去耦电容可获得更好的滤波效果。使用的模拟电源必须稳定性好、噪声低。对ADS1202来说,更高的分辨率及电源抑制比将是十分必要的。数字电源含有高频噪声,有可能耦合到ADS1202的模拟部分。这种噪音可能来自于开关电源、单片机或数字信号处理芯片。通常,外部的数字滤波器能以MCLK的整倍数抑制高频噪音。仅仅这些频率以下和以上的噪音将混入数字滤波器的传输频带,从而影响变换结果。例如:在接通电源后,ADS1202的输入、VIN+、VIN-和MCLK还不出现,这种情况将引起锁存。在接通电源之后如果这些信号出现,串连电阻将被用来限制输入电流。要确定ADS1202和不同电源之间的适当连接,实验是最好的方法。 5.2 接地 设计时把模拟和数字电路部分必须小心清楚的分开,每一部分都要有它们自己的地线,并且不能重迭。变换器下面不要连接地线,但应把两者用适当的信号线相连。对于多个变换器,连接的两上地线要尽可能靠近所有变换器的一个中心区域。在某些情况下,要找到把两个地线连到一起的最佳点,必须通过实验。 5.3 电路的去耦 在ADS1202的电路设计中,一定要用好去耦元件,所有的支耦电容,特别是0.1μF的陶恣电容一定要尽可能地安放在靠近去耦管脚。为对VDD至GND去耦,必须将1μF和10μF电容器与0.1μF电容并联在一起。对VDD至GND去耦至少要用一个0.1μF的陶瓷电容,另外,加到每一个数字元件上的电源也应如此。 责任编辑:gt (责任编辑:admin) |