|

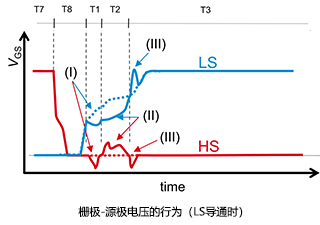

正电压浪涌对策 下图显示了同步升压电路中LS导通时栅极-源极电压的行为,该图在之前的文章中也使用过。要想抑制事件(II),即HS(非开关侧)的VGS的正浪涌,正如在上一篇文章的表格中所总结的,采用浪涌抑制电路的米勒钳位用MOSFET Q2、或误导通抑制电容器C1是很有效的方法(参见下面的验证电路)。

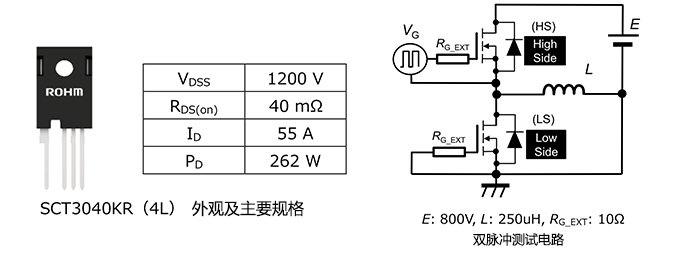

为了验证抑制电路的效果,将抑制电路单独安装在SiC MOSFET(SCT3040KR)的驱动电路上并观察了其波形。下面是所用SiC MOSFET的外观和主要规格,仅供参考。

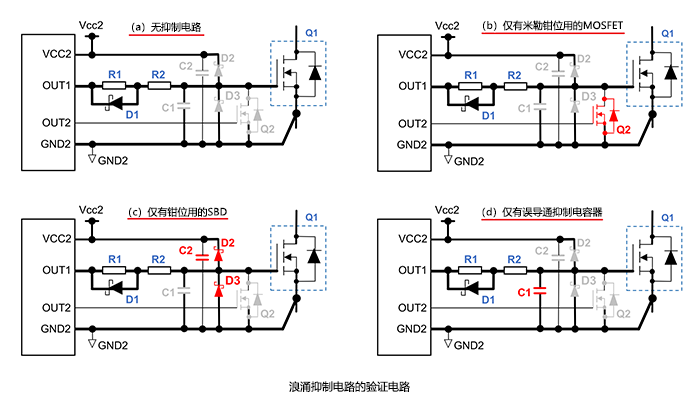

以下电路为用来验证的抑制电路,共四种:(a)无抑制电路,(b)仅有米勒钳位用的MOSFET(Q2),(c)仅有钳位用的肖特基势垒二极管D2、D3、C2,(d)仅有误导通抑制电容器C1。通过“双脉冲测试”确认了GS的浪涌电压。

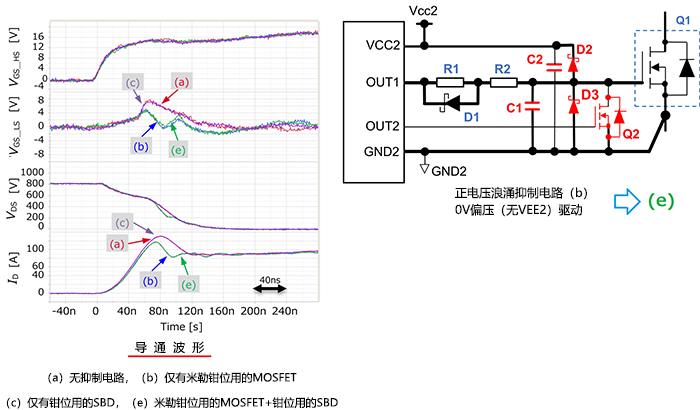

下面是使用了各验证电路的双脉冲测试的波形。这是导通时的波形,从上到下依次显示了开关侧栅极-源极电压(VGS_HS)、非开关侧栅极-源极电压(VGS_LS)、漏极-源极电压(VDS)、和漏极电流(ID)。同时,给出了前述的抑制电路(a)、(b)、(c)的波形,并将上一篇文章中的正电压抑制电路(b)的波形作为“(e)”一并列出。(e)的电路是配备了前述(b)~(d)所有抑制电路的电路。

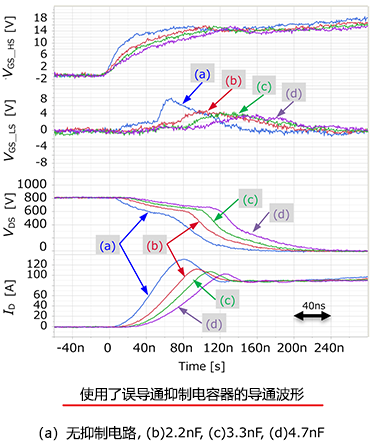

从上面的波形图中可以明显看出,在没有对策电路的(a)和只有钳位SBD的(c)中,可以看到结果是未能抑制正浪涌电压,VGS_LS波形隆起,并显著超过了栅极导通阈值,ID也比其他电路大。也就是说,非开关侧的MOSFET(在本例中为LS)发生了误导通。 要想防止这种误动作,配备有米勒钳位电路的对策电路 (b) 是必不可少的措施。而实际安装米勒钳位电路时,需要能够驱动米勒钳位用MOSFET的控制信号。该信号需要在监控VGS电压的同时控制驱动时序,一般情况下,很多驱动IC都具有该功能,但如果使用不具有该控制功能的驱动IC,则很难实现这种对策电路。 在这种情况下,如验证电路(d)所示,可以在MOSFET的栅极-源极间连接误导通抑制电容器C1,作为浪涌对策电路。连接了误导通抑制电容器C1时的导通波形如下图所示。波形(a)是没有C1的波形,波形(b)、(c)和(d)是有C1、C1分别为2.2nF、3.3nF和4.7nF时的波形。从图中可以看出,与没有C1的(a)相比,在具有C1的(b)、(c)和(d)中,VGS_LS的波形隆起更小,ID的导通浪涌也更小。

但是,从ID的波形中也可以看出,当连接了误导通抑制电容器C1时,导通动作会根据其电容量而减慢,从而会导致开关损耗增加。因此,C1的容值应该选用所需要尽量小的值。在此次的评估中,波形(b)所示的2.2nF可以说是正合适的。 审核编辑:郭婷 (责任编辑:admin) |