|

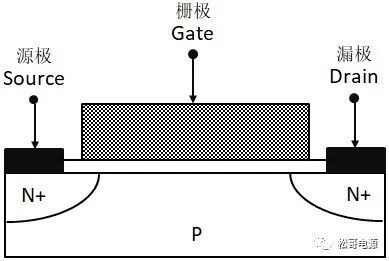

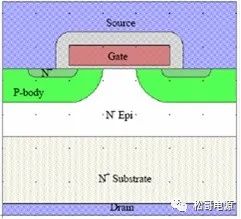

功率MOSFET即金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor)有三个管脚,分别为栅极(Gate),漏极(Drain)和源极(Source)。功率MOSFET为电压型控制器件,驱动电路简单,驱动的功率小,而且开关速度快,具有高的工作频率。常用的MOSFET的结构有:横向导电双扩散型场效应晶体管LDMOS(Lateral Double-Diffused MOSFET)、垂直导电双扩散型场效应晶体管(Planar MOSFET),沟槽型场效应晶体管(Trench MOSFET),超结结构场效应晶体管(Super Junction MOSFET),浮岛结构场效应晶体管等。 1、横向导电双扩散型场效应晶体管的结构 N沟道的横向导电双扩散型场效应晶体管的结构如图1所示,栅极,漏极和源极都在硅片的上表面,下部为衬底。栅极和源极加上正向电压后,在栅极的氧化层下面的P区吸附电子,栅极和源极正向电压大于一定的值时,P区紧靠栅极的氧化层的薄层中,局部的电子的浓度大于P区的空穴的浓度,从而形成“反型层”,也就是薄层由P型变成N型,电子就可以从源极通过反型层流向漏极,电流从漏极向源极流动,这个反型层就形成电流流过的通道也称为“沟道”。 电流从漏极流向源极时,电流在硅片内部横向流动,而且主要从硅片的上表层流过,因此没有充分应用芯片的尺寸;而且,这种结构的耐压,由栅极下面P层宽度和掺杂决定,这个区域同时也是导电的沟道,为了减小沟道的导通电阻,栅极下面P层宽度不可能过大,掺杂浓度也不可能太低,因此,其耐压通常也比较低,无法承受高的反向电压。另外,电流从芯片表面的薄层流过,即使是沟道的截面积增加,但芯片整体的截面积也不大,这样,芯片电流流过的截面积非常小,因此,导通电阻比较大,无法流过大的电流。这种结构的电压和电流的额定值都受到限制,无法用于功率电路。但这种结构具有低的电容,使用短沟道,因此开关速度快,主要适合低压应用,如微处理器、存储芯片,运放、数字电路及射频电路等。

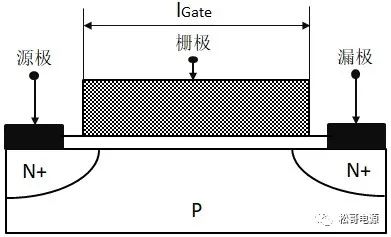

图1 横向导电结构的MOSFET 在芯片制程工艺中,经常使用芯片或半导体的工艺尺寸,如3um、2um、1.5um、1um、0.8um、0.5um、0.35um、0.25um、0.18um、0.13um、90nm、65nm、45nm、32nm、22nm、14nm、10nm,通常所说这个工艺尺寸,指的就是栅极Gate的宽度,也是沟槽宽度或者线宽,不是每个晶胞单元尺寸,如图2所示。沟槽宽度对应着漏极到源极的距离,沟槽宽度减小,载流子流动跨越沟道的导通时间减小,允许工作开关频率可以提高;沟槽宽度小,沟道开通所加栅极电压可以降低,导通更容易,开关损耗降低,同时,沟道导通电阻降低,降低导通损耗。但是,漏极和源极的间距不断减小,栅极下面接触面积越来越小,栅极对沟道的控制力就不断减弱,带来问题就是栅极电压为0时,漏极和源极的漏电流增加,导致器件性能恶化,增加了静态功耗。使用上下双栅极结构、鳍型结构(FinFET),就可以解决了短沟道效应这个问题,这样也促进了新一代芯片的工艺尺寸不断的降低,工艺水平不断提升。

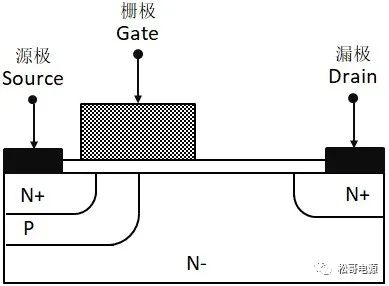

图2 芯片工艺制程的线宽 单芯片的电源IC中,内部集成的功率MOSFET只能使用横向导电结构,因为所有的引脚都在芯片的表面。为了解决漏极和源极的耐压比较低的问题,必须对上面的结构进行改进。因为外加电压的正端加到MOSFET的漏极,如果在高掺杂的漏极N+和P区的沟道之间,增加一个低掺杂的N-区域,如图3所示,因为N-和N+为相同的半导体类型,不影响电流导通的回路,电流可以直接从N+流向N-;尽管N-为低掺杂,但是,其电阻率低于沟道,这样,通过调整其掺杂浓度和宽度,就得到较高的反向电压,同时控制其导通电阻在设计的范围内,这种结构就可以流过大电流,应用于功率电路。

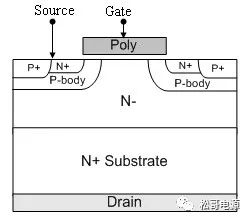

图3 横向导电的功率MOSFET 在漏极N+和P-体区之间增加的N-层,称为“漂移层(Drift Layer)”,也称为“外延层(Epi Layer)”。当漏极和源极之间加上电压时,P区掺杂浓度高,耗尽层主要在N-层的漂移层中扩展,漏极和源极的阻断电压,几乎完全依赖漂移层的宽度和掺杂浓度。 使用N-漂移层作为衬底,在N-漂移层中,通过2次的扩散就可以形成图3的结构:第1次扩散制作出P阱,也称为P-体区(P-Body);然后,在P-体区的内部,第2次扩散制作出N+源极。因此,这种结构称为横向导电双扩散型功率MOSFET,LDMOS(Lateral Double-Diffused MOSFET)。 尽管P区多数载流子(多子)为空穴,在P区内部局部区域进行扩散掺杂,只要掺杂的5价元素的浓度,大于P区原来3价元素的掺杂浓度,那么,在这个局部区域的电子的浓度就大于空穴,从而转变为N型半导体。因此,判断是N型半导体还是P型半导体,掺杂几价的元素不是关键,主要的依据是电子浓度和空穴浓度。如果一个区域中,电子浓度高于空穴浓度,那么,多子是电子,少子是空穴,就是N型半导体,反之就是P型半导体。 2、垂直导电双扩散型场效应晶体管的结构 芯片的厚度非常薄,而芯片的面积,相对的尺寸比较大,图3中,电流依然是在芯片的上表层,横向水平从漏极流向源极,电流流过的截面积小,导通电阻大,芯片的尺寸没有充分得到利用;同时,为了提高漏极和源极的耐压,N-层漂移层的宽度必须增加,这样进一步增加了导通电阻,限制了芯片流过电流的能力,因此,如果设计高压大电流的LDMOS,芯片的尺寸将非常大,成本非常高。所以,LDMOS只用在低压、较小电流的单芯片电源IC里面。 如果把图3的结构中MOSFET的漏极N+区,移到衬底的底部,漏极通过衬底的下表面引出, MOSFET导通后,电流就可以从衬底底部的漏极垂直流向顶部的源极,电流在芯片内部垂直流动,而且电流流过芯片整个水平的截面积,由于芯片水平截面积较大,导通电阻小,这样,就可以提高MOSFET通过电流的能力,如图4所示。

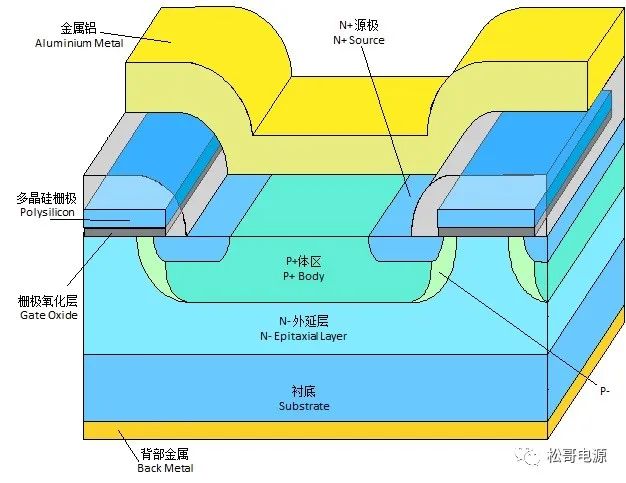

图4 垂直导电的功率MOSFET 这种结构中,N-外延层的掺杂浓度越低、厚度越大,漏极和源极的耐压值越高,导通电阻越大;反之,掺杂浓度越高、厚度越小,耐压值越低,导通电阻越小。因此,通过调整N-外延层的掺杂浓度和厚度,就可以保证耐压值达到要求,同时,导通电阻也满足设计的要求。 这种结构的N沟道功率MOSFET,使用衬底为高掺杂的N+衬底,高掺杂衬底部分的电阻小;然后在N+衬底上制作出低掺杂、高纯度、一致性非常好的N-的外延层。然后,在N-的外延层中,同样的通过2次扩散掺杂,制作出两个连续的P-体区以及在二个P-体区内部的N+源极区。在芯片表面制作出薄的高质量的栅极氧化物,在氧化物上面沉积多晶硅栅极材料,沟道在栅极氧化物下面的P-体区中形成,源极和漏极区沉积金属材料,就完成了这种结构的生产。这种结构的电流从下到上垂直流过,通过2次扩散掺杂加工,因此,称为垂直导电双扩散功率MOSFET。在加工过程中,这种结构没有挖沟槽,采用的是平面的工艺,也称平面结构的功率MOSFET。 其工作原理是:栅极和源极间加正向电压,P区中的少数载流子,即少子,也就是电子,被电场吸引到栅极下面的P区的上表面,随着栅极和源极正向偏置电压的增加,更多的电子被吸引到这个表面的薄层区域,这样本地的电子密度要大于空穴,从而出现“反转”,形成反型层,半导体材料从P型变成N型,形成N型“沟道”,电流可以直接通过漏极的N+区、N-外延层、栅极下面N型沟道,流到源极的N+型区。 实际上,在上面的结构图中,示意的只是功率MOSFET内部一个单元的结构,也称“晶胞”。功率MOSFET的内部,由许多这样的单元,也称“晶胞”,并联而成。芯片的面积越大,所能加工出的单元越多,器件的导通电阻越小,能够通过的电流就越大;同样,在单位的面积的芯片上,能够加工的晶胞越多,也就是晶胞单位密度越大,器件的导通电阻也就越小。器件的导通电阻越小,通过电流的能力就越大,电流额定值也就越大。 在这种结构中,栅极下面的区域没有流过功率主回路的大电流,因此栅极下面占用的部分芯片的面积不能充分得到应用,也影响到能够加工的晶胞单位密度的最大值;栅极的面积大,寄生电容Crss就越大,因此开关性能较差,开关损耗大;同时,结构内在的JFET效应,导致导通电阻也偏大。但是,这种结构的功率MOSFET,工艺非常简单,单元的一致性较好,因此它的跨导的特性比较好,雪崩能量比较高,同时寄生电容也较大,主要应用于高压的功率MOSFET和开关频率不太高的中压功率MOSFET。

图5 平面结构的功率MOSFET

图6 平面结构的功率MOSFET立体图

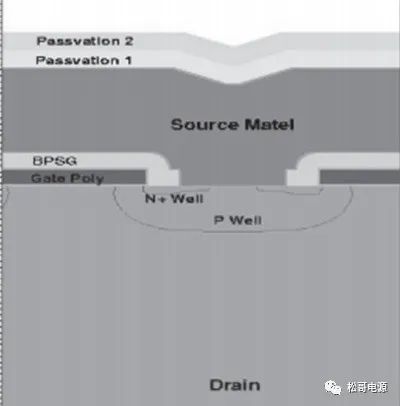

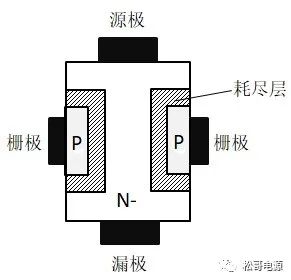

图7 平面结构的功率MOSFET截面图 在图4中,栅极氧化层的的下面是N-外延区,在其二侧是二个P-体区,这种结构内在的就形成了一个JFET,如图8所示,产生JFET效应。N-区和二侧P区,形成PN结,产生耗尽层和空间电荷区。即使是在功率MOSFET导通的时候,这个耗尽层依然存在,那么,电流主要从二个P区之间非耗尽层的区域流过,相当于实际能通过电流的截面积减小,也就是相当于导通电阻变大,因为JFET效应增大的电阻,称为JFET电阻。耗尽层越宽,电流的通道面积越小,JFET效应越明显,JFET电阻越大。耗尽层的宽度,和JFET的栅极(P区)到JFET的源极(N-外延层最上部区域)的电压绝对值有关,这个电压绝对值为0,耗尽层非常窄,JFET电阻非常小;这个电压绝对值升高,耗尽层变宽,JFET电阻变大。当然,JFET电阻也受功率MOSFET的漏极和源极导通电压的影响。

图8 JFET的结构 审核编辑:汤梓红 (责任编辑:admin) |