|

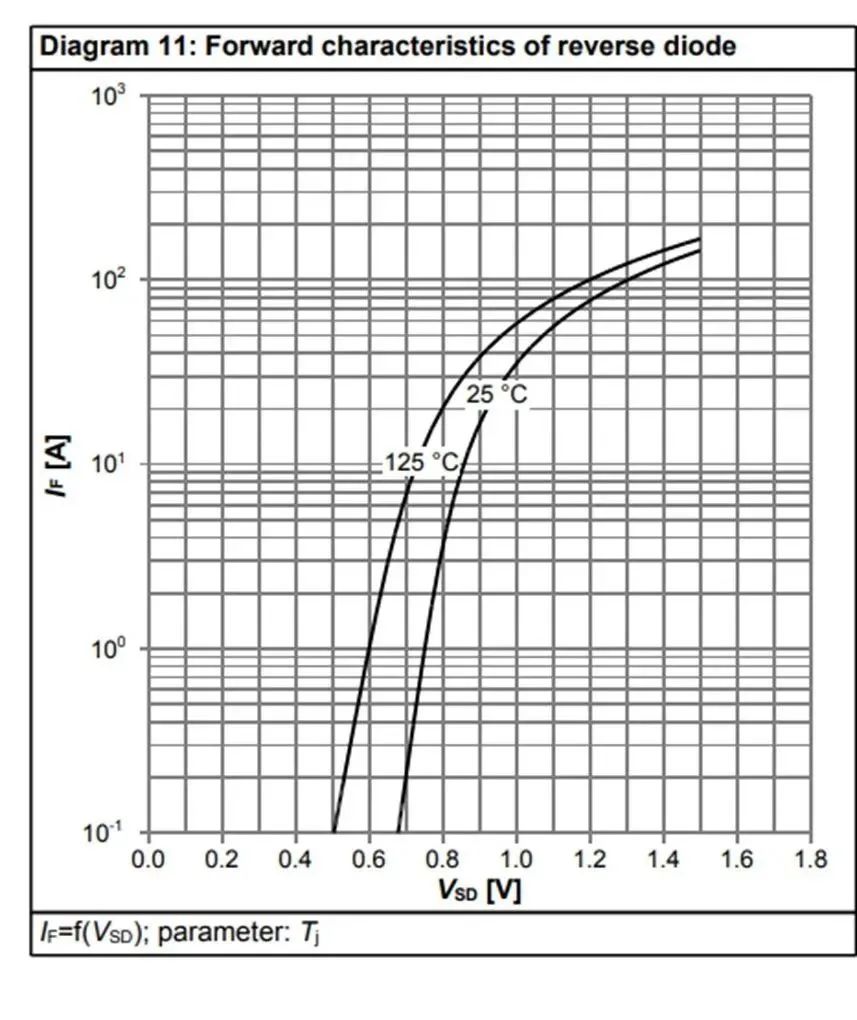

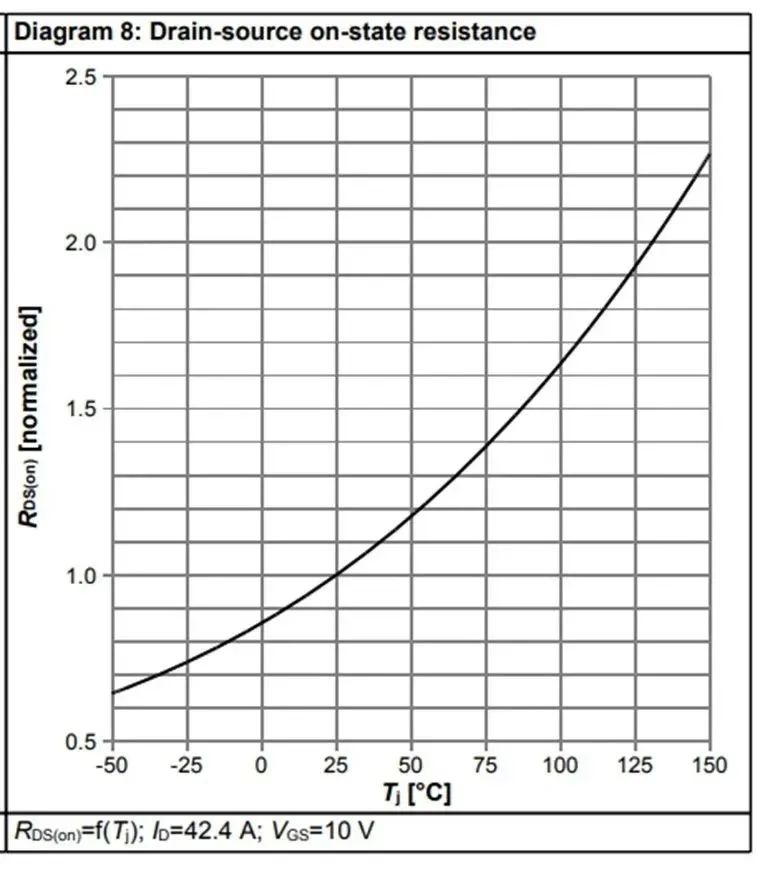

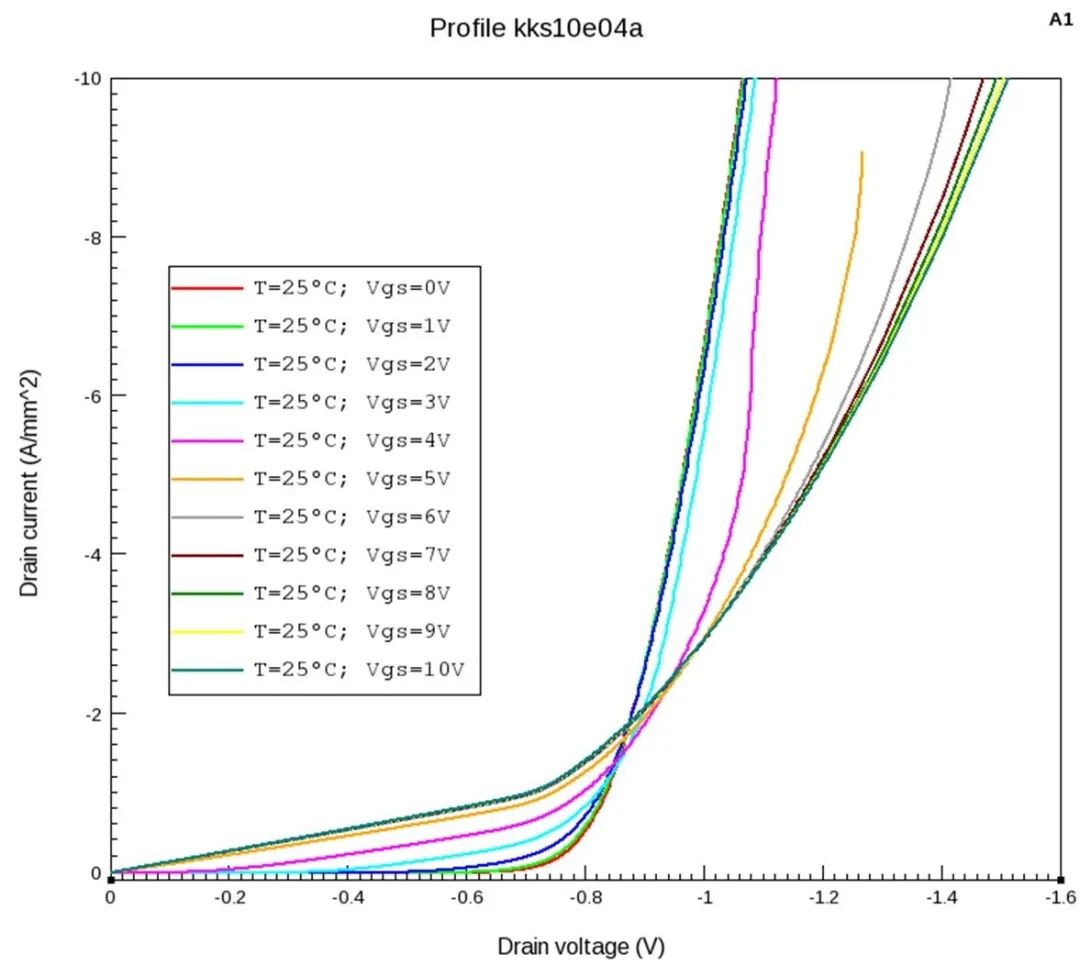

引 言 相信各位工程师在日常的电源设计中,当面对ZVS的场景时,经常会有如下的困惑:比如大名鼎鼎的LLC,工作在死区时,MOSFET 寄生二极管续流,当完成了对结电容的充放电之后,再打开MOSFET以降低器件的损耗。 细心的工程师可能就会发现一个有趣的问题,我们这里拿IPW60R024CFD7举例说明,假设死区时刻,流过二极管的电流为50A (125℃结温),那么此刻MOSFET源漏极压降Vsd=0.96V;(如下图所示)

当死区结束,给到驱动信号,打开MOSFET,假设电流完全流过沟道,那么此刻Vsd=50*0.024*1.9=2.28V。(备注:1.9为125℃下电阻标准化比率)

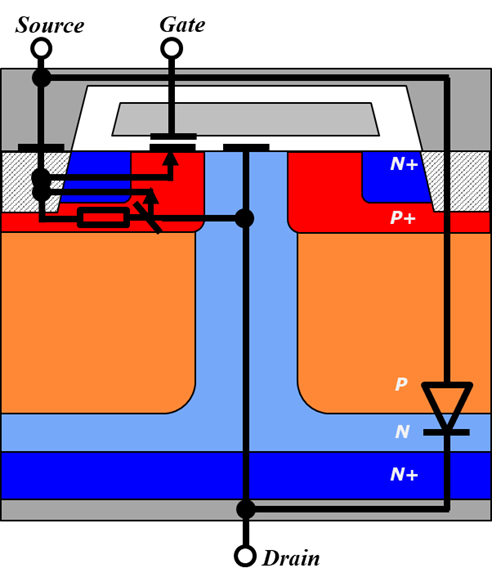

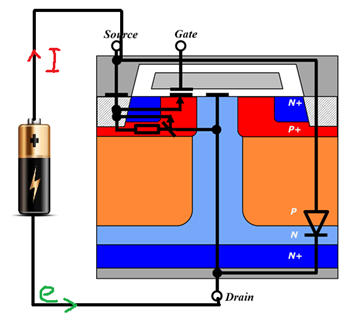

这时候您可能心里就要犯嘀咕了:打开了MOSFET后,导通损耗反而变大了?电流到底是走沟道还是体二极管?如果损耗变大了那么我还需要打开MOSFET吗? 带着以上疑问,我们来细细的品一下HV SJ MOSFET的一些小知识吧! 2 HV SJ MOSFET小知识 SJ MOSFET的剖面图如下所示:在这个结构中,我们可以看到三个器件模型: 1.NMOS 导电沟道 2.寄生NPN三极管(BJT) 3.寄生PIN二极管

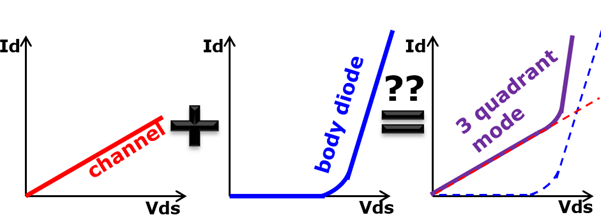

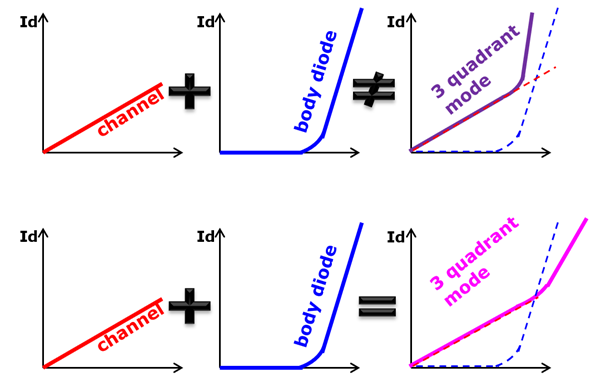

以上2种寄生结构分别对MOSFET器件的物理参数有着如下的限制: 1.寄生BJT:限制MOSFET器件dVds/dt能力,寄生BJT导通条件约为dVds/dt > VBE(BJT)/(Rp+ * Cdb),硬开关场景需要考虑该因素; 2.寄生体二极管:限制MOSEFT器件dI/dt反向恢复能力(Qrr),硬开关场景需要考虑该因素。 当MOSFET工作在开关状态时,处于线性工作区,其物理特性为等效电阻,(如下图所示),二极管I-V曲线大家都耳熟能详,那么当二者同时导通电流时,会是怎样?简单的几何相加吗?

3 探究MOSFET在第三象限的工作 根据常识我们知道,对于一个给定的MOSFET,其导通电流的能力,宏观上,与驱动电压大小,MOSFET结温都有着密切联系。那么当MOSFET工作在第三象限是否还有类似的关系呢?我们这里采用控制变量法,通过仿真来一探究竟: 首先我们看同一结温(25℃)下,不同的驱动电压I-V曲线:

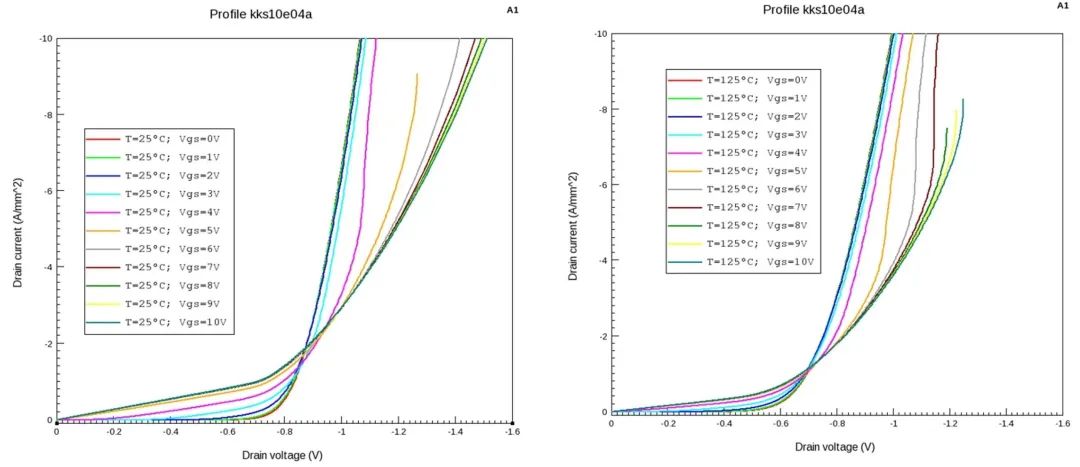

由上仿真结果图我们可以总结出: 1.Vgs< Vgs(th)时,沟道尚未打开,MOSFET I-V曲线表现为二极管特性; 2.Vgs>Vgs(Miller)时,沟道打开,MOSFET IV曲线在小电流下表现为纯阻性(I-V曲线呈现线性关系),在大电流下表现为沟道、寄生体二极管二者共同作用(I-V曲线呈现非线性关系); 3.在大电流场景下,Vgs电压越高,MOSFET器件呈现阻性(I-V曲线斜率)越大。 其次,我们再看一下不同结温下 MOSFET I-V曲线,有如下结论:

1.Vgs沟道尚未打开,结温越高,寄生体二极管导通阈值电压越低,电阻率越低(二极管特性); 2.Vgs>Vgs(miller)时,沟道打开,小电流下,结温越高,器件电阻率越高;大电流下,结温越高,器件的电阻率越低。 MOSFET器件沟道本身为少子(电子)导电,其温度越高,电子迁移率越低,因此阻性越大;PIN二极管、BJT 均为双极型载流子器件,其电导调制效应起主导作用,因此电流越大,阻性越低;温度越高,(电导调制效应越强,载流子浓度越高)阻性越小。 4 微观世界的神秘风采 好奇的工程师朋友们肯定想知道:在微观世界下,是什么之间的相互作用,导致了上述的结果呢?我们在这里抛砖引玉,尝试性的扒开微观世界的面纱,一瞥其神秘风采: 1.当Vgs=0时, P、N、N+掺杂层形成PIN二极管的结构,在外加电场的作用下,电子源源不断的通过电源负极,注入到N+层,N层,使得轻掺杂的N层载流子浓度以非线性的形式快速提高,大大提高了通流能力;空穴同理。 2.N+、P+、N掺杂层形成NPN BJT结构,变化的电场改变电子移动方向、速度(电流方向、大小),当电子(位移电流)流过P+层(等效电阻)以及P+层与衬底等效电容的产生的压降>BJT的开通阈值电压Vʙᴇ时,(即当外加电场变化率dVds/dt > VBE(BJT)/(Rᴘ+* Cdb)时,)BJT导通。 3.当Vgs > Vgs(miller)时,P+层足够多的电子被吸附到栅氧层表面,形成导电沟道,此时MOSFET沟道导通: 1)当电流较小时,MOSFET Vsd两端管压降 < 二极管开通阈值,不足以维持二极管内部反型层,二极管关闭,此刻电流完全流经沟道。 2)当电流较大时,MOSFET Vsd 两端管压降 > 二极管开通阈值,二极管参与导通:PIN结构二极管内部电子空穴对均参与导电。由于Gate-Souce正电压的存在,将会捕获PIN结构二极管部分自由移动的电子空穴对,进而呈现出Vgs电压越高,电阻率越大的结果。当在导电沟道内的电子移动速率、数量与PIN二极管的电子空穴对移动速率、数量达到动态平衡时,器件进入稳态。

通过以上的分析,我们知道了MOSFET器件工作于第三象限时,电流路径不是简单的加和,是沟道跟寄生结构的共同作用效果。

5 能效非凡,低碳未来 既然是这样,那么为什么我们在器件处于第三象限时,我们还要打开驱动,让沟道也参与导电呢?(此刻的阻抗明显更大了) 答案是这样的:MOSFET寄生的结构虽然可以大大的降低导通阻抗,但是由于电导调制效应的存在,使得载流子复合消失过程时间大大增加,进而导致严重的关断损耗。在实际的电路设计中,需要权衡开关损耗、导通损耗,折衷处理。通常,对于硅基 MOSFET来讲,导通损耗与关断损耗会控制在一个数量级上。在如今的电源产品中,开关频率已经从几十KHz覆盖到几个MHz,即使是ZVS的拓扑结构(比如LLC),由于关断损耗的存在,也需要完全打开沟道,使得尽可能多的电流流经沟道,这样在关断时有,PIN结构二极管内载流子可以更快的复合消失,以减小器件关断损耗(Qrr)。 好消息是伴随着Infineon CoolGaN器件的出现,GaN器件由于其材料特性(关断损耗极小)、结构特性(不存在寄生二极管),在ZVS的拓扑(比如LLC),可以在不牺牲效率的前提下大幅提升开关频率,将电源产品的功率密度、效率,往前推进一个新的时代。 全文完 (责任编辑:admin) |