|

在2000年的第一个月,Santa Clara University的Sergey Savastiou教授在Solid State Technology期刊上发表了一篇名叫《Moore’s Law – the Z dimension》的文章。这篇文章最后一章的标题是Through-Silicon Vias,这是 Through-Silicon Via 这个名词首次在世界上亮相。这篇文章发表的时间点似乎也预示着在新的千禧年里,TSV注定将迎来它不凡的表演。

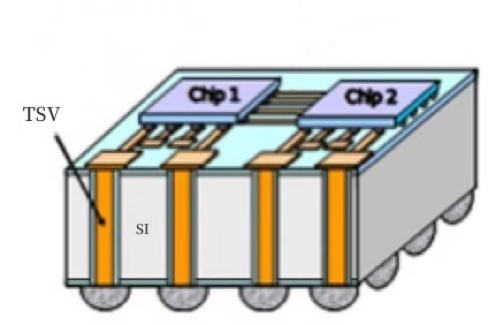

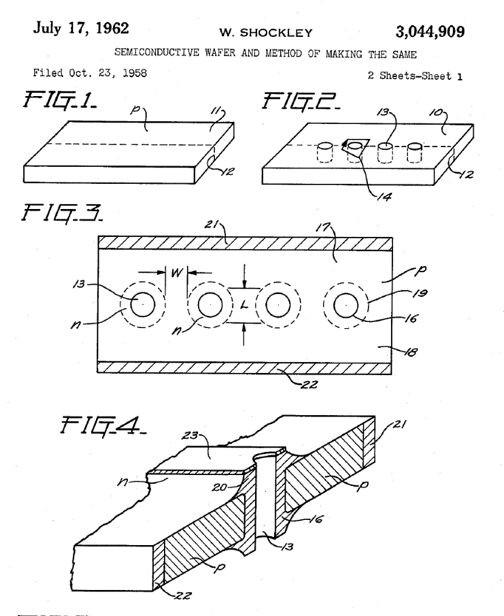

TSV示意图 TSV,是英文Through-Silicon Via的缩写,即是穿过硅基板的垂直电互连。 如果说Wire bonding(引线键合)和Flip-Chip(倒装焊)的Bumping(凸点)提供了芯片对外部的电互连,RDL(再布线)提供了芯片内部水平方向的电互连,那么TSV则提供了硅片内部垂直方向的电互连。 作为唯一的垂直电互连技术,TSV是半导体先进封装最核心的技术之一。 与集成电路一起诞生的垂直互联 1958年的秋天,肖特基(William Shockley)坐在办公室思考着如何设计晶体管可以实现高频的应用。早在1947年,他便与巴丁、布拉顿一起研制出了第一个晶体管,并在1956年一起获得了诺贝尔奖。 “为什么不能在晶圆上打些孔?” Shockley喃喃自语。 不久Shockley申请了一项专利 -(SEMICONDUCTIVE WAFER AND METHOD OF MAKING THE SAME),这是历史上第一项在晶圆上刻蚀通孔的专利。虽然这项专利的初衷是只为了晶体管在在高频率领域的应用,但在这项专利中,肖老也提到了如果需要可以在通孔中填充导电金属。就这样,发明晶体管的人也成了第一个想到在晶圆做导电孔的人。同一年还发生一件大事,将多个晶体管制造在一起的集成电路(芯片)也被发明出来了。

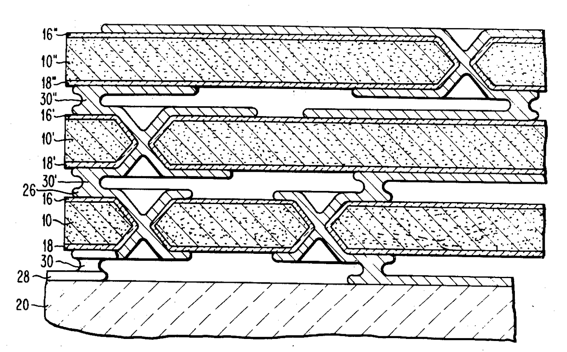

肖特基的硅片上制作孔专利 此后, IBM开始在集成电路领域发力,并在垂直电互连方面取得了突破。 6年之后的1964年,IBM申请了一项专利(METHODS OF MAKING THRU- CONNECTIONS IN SEMICONDUCFOR WAFERS),提出了利用在通孔中做简并掺杂降低电阻的方式实现硅片的垂直互连,即用低阻硅为导电材料。但是这项专利还只是停留在硅片自身上下表面器件的,并没有用于多芯片的堆叠。直到5年后的1969年,IBM才在另一项专利 (HOURGLASS-SHAPED CONDUCTIVE CONNECTIONTHROUGH SEMCONDUCTOR STRUCTURES) 中首次提出了基于垂直互连的多层芯片的堆叠,如下图:

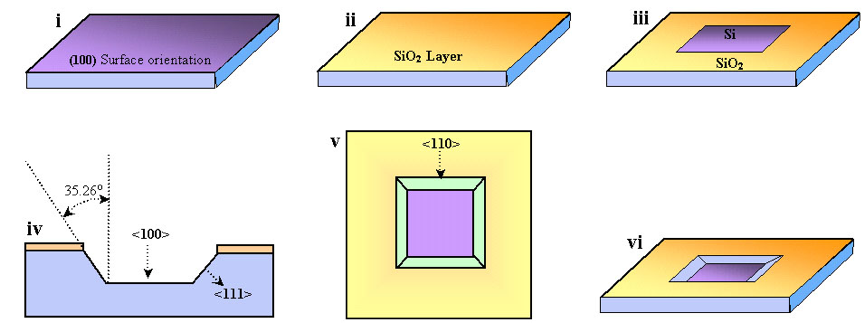

第一个芯片堆叠专利 似乎只用了11年,甚至在TSV这个名词被正式发明前,垂直互连的概念和工艺都已经发展好了。只是IBM的这项专利并没有得到大规模的应用。原因在于这个专利中导通孔的形状,如其专利名字 “HourGlass” 所示,是沙漏形的,它占用太多的面积。这种形状的通孔涉及到2年前(1967年)Bell Telephone Laboratories的H.A. Waggener的一项发现:KOH对于单晶硅的不同晶面的腐蚀速率有巨大的差异【1】。 例如对<100>晶面的腐蚀率要比<111>晶面大几百倍。利用这个特点可以在常用的<100>硅晶圆很方便的刻蚀的通孔,但是孔形是倒金字塔形状的(或者说是沙漏形的)。随着摩尔定律的不断发展,单位面积上晶体管越来越密集,这种占用大量表面积的垂直互连显然失去了其存在的意义。

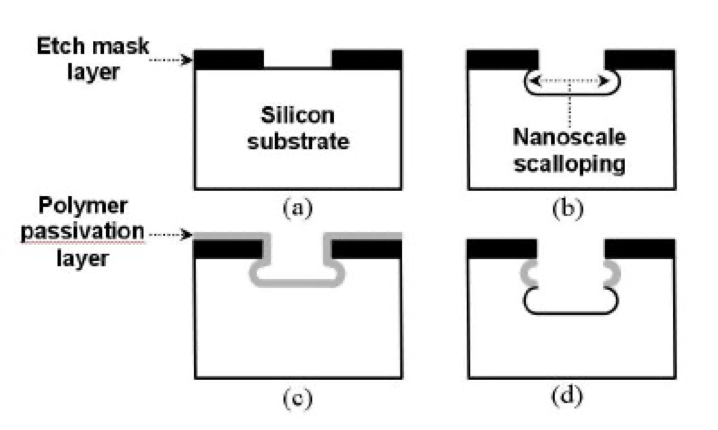

KOH刻蚀示意图 但或许是受IBM提出的这个堆叠芯片概念的影响,三维集成芯片这个理念在半导体行业像星星之火燎原一样传播开来。此后共计有40多家研究机构和公司参与了相关技术的研究【2】,而 作为三维堆叠芯片中最核心的垂直电互连技术 自然也倍受关注。在接下来的70到90年代,半导体微加工技术的多项突破将为现代TSV的诞生打下坚实的基础。 技术的突破 硅作为一种半导体材料,既没有很好的导电性也没有很好的绝缘性。 要在硅片上实现垂直的电互连,一般需要在上面制作微孔 (取决于具体的应用,一般孔径在几个微米到几百微米,头发丝约为50微米,而且单片硅片上需要的孔数量可达数十万);在孔的侧壁沉积绝缘材料;在微孔中填充导电材料等制造步骤。其中最具挑战的是微孔的批量刻蚀和导电化。 首先,在硅晶圆上加工微孔不是件容易的事。硅硬度大且脆,而需要加工的孔径小且量大,用传统的机械加工方式根本不可行。在1958年肖特基的专利中,他提出了用晶料界面的化学腐蚀速率的差异来实现微孔的刻蚀 (因为历史久远加上缺少足够资料,未能完全理解肖老的这种腐蚀方法*_*)。 反向溅射(即等离子物理轰击刻蚀)也曾被尝试做刻蚀,但是速率太慢,于是人们不得不又回到化学腐蚀的老路上。上文提到的KOH刻蚀是化学腐蚀的一种,属于各向异性腐蚀,只是无法实现最合适TSV的圆柱孔。80年代开始,日本开始在三维集成方面发力,成立了“Three-Dimensional Circuit Element R&D Project”。1983年和1984年Hitachi的两项专利中都提到了用激光打孔的方式来解决硅片上微孔刻蚀的问题【3】。不同于KOH刻蚀的“沙漏孔”,这些专利都使用了圆柱孔。但是激光加工也存在不少问题,一方面孔只能一个个加工比较耗时,另外加工的孔存在表面粗糙以及崩边等问题。 直到90年代,硅刻蚀才迎来了突破,DRIE深硅刻蚀技术横空出世。 DRIE,Deep Reactive Ion Etching的首字母缩写。 这项技术是1994年德国Robert Bosch公司在此前一项低温离子硅刻蚀技术的基础上发展的一项高深宽比硅刻蚀技术【4】。这项技术用了一种很巧妙的方法实现了 各向同性腐蚀来刻蚀圆柱孔。各向同性腐蚀与上面讲的KOH这种各向异性腐蚀不同,它在腐蚀硅片时各个方向是均匀的,所以正常情况下它只能在硅片上刻蚀出球状的孔。使各向同性腐蚀实现圆柱孔刻蚀的核心思想是将腐蚀分割成无数的小步。 它的具体方法是:先在硅片把需要刻蚀微孔的位置的硅裸露出来,用各向同性的腐蚀气体在硅片上刻蚀下去一薄层,然后在刻蚀出来的坑的表面沉积保护层,再用等离子打掉坑底的保护层打掉,再用各向同性的腐蚀气体刻蚀一薄层,通过这样多次微小的各向同性腐蚀循环就可以在硅片上实现批量的高深宽比微孔的刻蚀。事实上这项技术如此重要,后来也成为MEMS的核心制造技术。

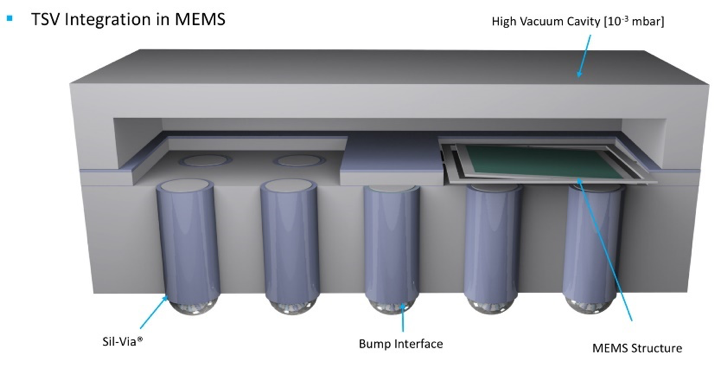

DRIE的示意图 微孔的导电化也同样富有挑战。在1958年肖老的专利中只是提及在孔中填充金属的想法,但并未提供任何具体的实施方法;1964年IBM的专利中是利用简并掺杂来降低硅的电阻从而将硅自身转化导电介质,这种方法无法用于微孔的导电化;而在1969年IBM申请的专利中,金属层是通过溅射的方式实现的。虽然溅射在当时是半导体主流的金属沉积方法,但是溅射一般只能用于厚度在1um以下的薄金属沉积,并且包覆性差,只能用于沙漏形孔的金属化。 1970年,Hitachi公司在一个专利中首次提出将用电镀在半导体晶圆中实现金属沉积【5】,虽然这个专利中电镀只是为了实现金属与硅的欧姆接触,但这项研究开启了电镀用于半导体加工的序幕。电镀技术是19世界上半叶由英国和俄罗斯的科学发明的一种全新的金属成形技术,与以前人类所有的纯物理金属加工方式,例如锻造,铸造,蒸发沉积,溅射沉积,机加工等都不同, 电镀是一种电化学技术。这项技术一开始主要被用于金属艺术品的批量制造。因其沉积速度相对较快并且可以实现批量的沉积这个特点,电镀这项技术在被发明100多年后,终于与半导体走到了一起。 5年后的1975年,IBM进一步将X射线光刻与电镀结合,开始探索电镀用于晶圆厚金属的沉积【6】。 1982年,这项技术在德国被进一步发展成一项重要的 MEMS技术LIGA。全称叫Lithographie, Galvanoformung, Abformung (英语:Lithography, Electroplating, and Molding) 【7】。这是一项结合光刻和电镀的用于高深宽比金属结构沉积的技术。作为MEMS(微电子机械)的核心技术,LIGA为MEMS早期的发展立下不少功劳。如果对上文还有印象的话,DRIE深硅刻蚀后来也成为MEMS的核心技术。所以说TSV和MEMS在技术是孪生兄弟一点都不为过! 90年代中期,半导体行业发生一件大事: IBM用铜电镀大马士革工艺全面替代的溅射铝作为集成电路中晶体管互连。这样电镀铜在半导体行业便开始成为标准工艺,这让电镀铜用于TSV的微孔金属化填充更加顺理成章。 至此, 现代TSV的两项核心技术:深硅刻蚀和电镀都出现了。 走向商用 TSV不仅赋予了芯片纵向维度的集成能力,而且它具有最短的电传输路径以及优异的抗干扰性能。随着摩尔定律慢慢走到尽头,半导体器件的微型化也越来越依赖于集成TSV的先进封装。TSV对于像CMOS Image Sensor(CIS,CMOS图像传感器),High Bandwidth Memory(HBM)以及Silicon interposer(硅转接板)都极其重要。因为存在感光面的缘故,CIS芯片的电信号必须从背部引出,TSV因此成为其必不可少的电互连结构。HBM是基于多层堆叠的存储芯片,如今HBM已经可以实现12层的堆叠,16层以上更多层的堆叠相信在不久的将来也会实现,当然这一切都离不开TSV的互连。而Silicon interposer可以将多种芯片,像CPU, memory, ASIC等集成到一个封装模块的关键组件,它的垂直互连同样需要TSV。事实上,法国的Yole development咨询公司曾做过一项研究发现TSV几乎可以应用于任何芯片的封装以及任何类型的先进封装,包括LED, MEMS等。 正是因为TSV的重要性,各大Foundry和OSTA公司也不断投入TSV技术的研发。这阶段的研发重点是如何保证电镀沉积主要发生在TSV孔内而不是硅片表面。如果不采取任何措施,电镀时硅表面金属沉积的速度会远快于TSV孔内。这个问题目前的解决方法是在电镀液中添加抑制剂和加速剂,分别抑制硅片表面的金属沉积并加速TSV孔内的沉积。为了获得完美的填充效果和足够高的良率,各大Foundry和OSTA公司都做了大量研究以获得最佳的电镀的参数,例如电流,温度,硅片的与电极的相对位置,添加剂的浓度等。各大半导体设备公司也开始针对TSV的电镀推出专用的半导体设备。 21世纪,基于深硅刻蚀和铜电镀工艺的TSV技术日渐成熟,并开始正式走向商用。 1999年和2000年,日本分别率先研发出第一款三层堆叠的图像传感器和三层堆叠的存储器件。2004年,出于对TSV未来应用前景的看好,TSV名词的提出者Sergey Savastiou教授成立了ALLVIA的公司专注于TSV代工制造。2005年,10层堆叠的存储芯片被研制出来。2007年集成TSV的CIS芯片由Toshiba公司量产商用,同年ST Microelectronics和Toshiba一起推出8层堆叠的NAND闪存芯片。2013年第一款HBM存储芯片由韩国Hynix推出。2015年,第一款集成HBM的GPU由AMD推出。 不走寻常路的Sil - Via 随着TSV在CIS和HBM中的大规模应用,似乎TSV技术已经成熟并没有太多可以创新的空间了。但是无论是CIS还是HBM,其中用到的TSV都是孔径只有10微米左右的小孔径TSV, 而基于电镀的TSV却一直没能攻下最后一个阵地:大孔径TSV的实心填充。对于大孔径例如直径50微米以上甚至100多微米的微孔,如果用电镀填充满需要几个小时,不仅成本非常高而且良率也难以保证。 对于大孔径TSV,瑞典有家MEMS公司却走出了另外一条“特色”技术路线。这家叫 Silex的公司不走寻常路, 独立开发出了一项基于低阻硅的Sil-Via的TSV技术。Sil-Via与电镀TSV有两大不同:首先,它用的硅基板材料本身就是低阻硅,类似于1964年IBM专利中的简并掺杂硅。其次,在制造过程中,Sil-Via刻蚀的不是孔而是环槽,通过在环槽是填充绝缘材料的方式实现中心低阻硅圆柱作为导电介质。Sil-Via主要用于MEMS器件的封装中,正是因为Sil-Via的巨大成功,Silex也成为世界最大的MEMS代工厂。2015年7月,中国资本收购了Silex,只是Sil-Via这项技术的核心,在几十微米的圆槽中饱满填充可以耐800度以上温度的绝缘材料,仍然被瑞典人所掌握着。但Sil-Via并不完美,低阻硅只能满足MEMS器件的导电要求,金属化的大孔径TSV孔依旧有着很大的需求,而这又涉及到一条新的技术路线,以后专门写一篇细说。

Sil-Via(from silex website ) 结 语 2022年3月9号,苹果公司推出的M1 ULTRA处理器,这款性能爆表的处理器中,多个CPU使用带TSV的Silicon interposer进行集成的。如今,无论是AI/AR/VR中用到的传感器,图像传感器,堆叠存储芯片以及高性能处理器,都越来越离不开TSV。 TSV, 这项并不为人熟知的技术,正在硬件的底层深深的影响着人类的生产生活方式。 半个多世纪前的那个秋天,肖特基那个在硅片上打孔的想法最终将人类带入了人工智能的时代。 编辑:黄飞 (责任编辑:admin) |