|

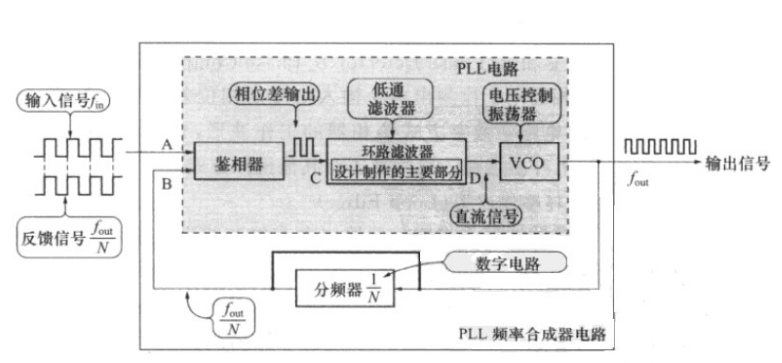

作者:吴红辉 公司:骏龙科技 随着移动通信的发展,通信技术已发展到5G 时代,通信系统也变得越来越复杂,频段也越来越高。有用的信号向更高频率的搬移,离不开本振的参与。锁相环(PLL)作为本振信号的来源,是现代通信系统的基本构建模块,广泛应用于各种通信设备,仪器仪表等测试设备中,也可用于时钟信号分配和降噪,或用作高采样速率模数或数模转换的时钟源。因此,本振的质量在通信系统中也至关重要。由于各种新的应用如信号的扫描不断出现,越来越多客户希望找到一款相噪好,又能更快锁定时间的合成器。ADI LTC6948和LTC6946系列就能很好地解决这个问题。频段能够覆盖从0.37G-6.39G,并可广泛应用于信号扫面、识别和捕捉。 一、锁相环的基本原理 锁相环主要由三大部分构成:鉴相器、VCO 、环路滤波器,如下图(图1)所示:

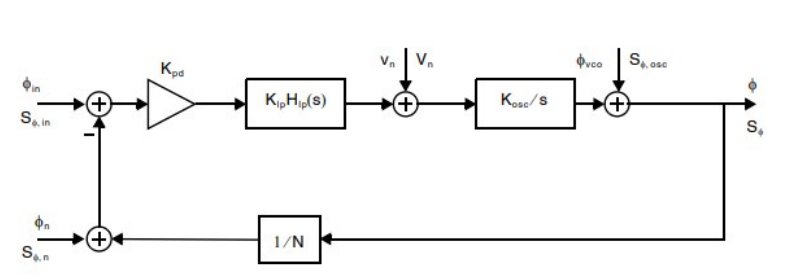

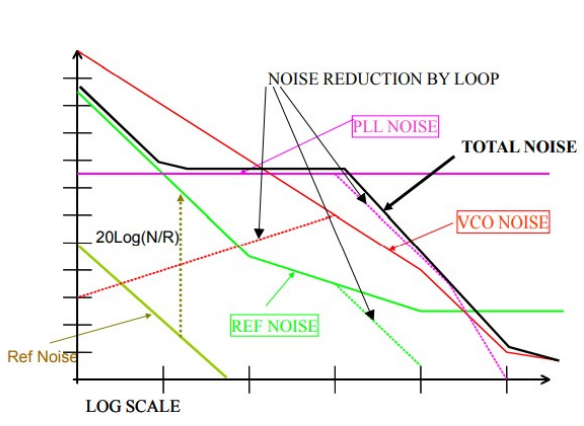

二 、合成器的核心指标 核心指标一:相位噪声 首先说到合成器的核心指标:相位噪声,我们需要了解相位噪声是由哪些因素决定的。这有利于我们在进行硬件调试时,及时准确找出问题所在,提高工作效率。 相位噪声的决定因素: · 参考源的抖动:φin · VCO 的固有抖动 · 环路滤波电路产生的噪声 · 分频电路产生的噪声

图2 锁相环传输函数模型

图3 相位噪声贡献分布图

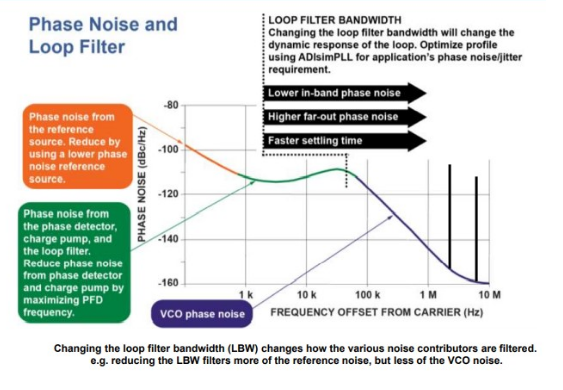

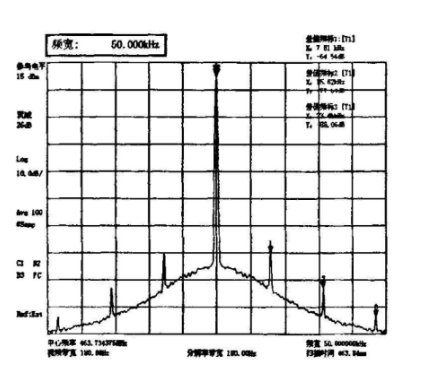

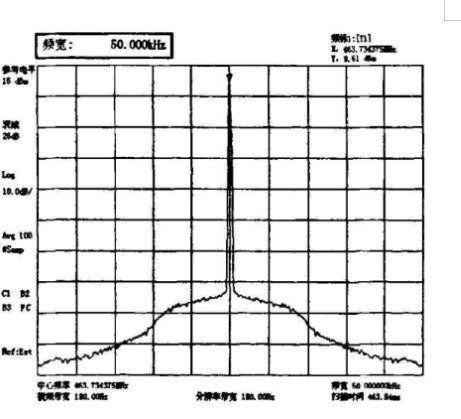

图4 相位噪声分布图 核心指标二:杂散 其次说到杂散,不得不提的是:ADI的LTC6948系列小数分频合成器,其采用了消除∆-∑ Modulator Spurs。∆-∑调制技术已成功地应用于音频范围的各种高性能的过采样中。在小数分频锁相环中 , 利用∆-∑调制技术 , 将合成器锁相环中小数分频器产生的相位杂散转换为高通型相位噪声 , 再利用环路低通滤波特性予以滤除 , 从而仅用单环即可获得很高的频率分辨率、极低的相位杂散及实现各种数字调制 , 这就大大简化了各种合成信号发生器的结构 , 成为一种先进实用的频率合成方式,并在国外获得广泛应用 。 对比前后的差异会发现为什么指标那么重要。因为在接收机系统中,杂散和其他信号混频得到的信号如果落在有用信号带内,会影响接收机的灵敏度,然而这些信号又是无法通过滤波来解决的,因此消除这些杂散是必要的。

图5 传统架构(无∆-∑调制技术)频谱

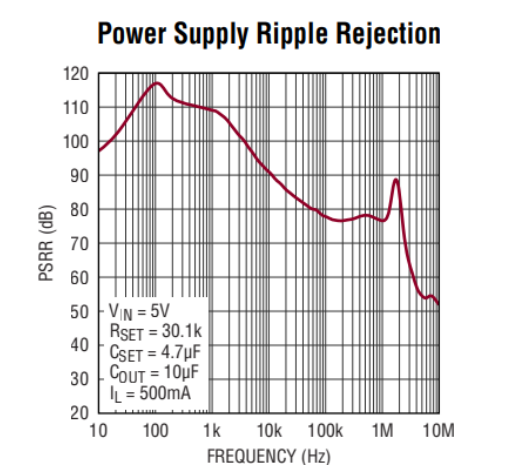

图6 有∆-∑调制技术的频谱 核心指标三:锁定时间 最后说到锁定时间的问题,LTC6948系列小数分频合成器,可以实现很小的频率分辨率,同时大大提高了鉴相参考频率,小数分频部分的整数分频远小于整数分频的分频比,这样就提高了频率切换的速度,解决了分辨率与速度之间的矛盾问题。 实测LTC6948和LTC6946系列合成器,在查表的模式下能达到大约20us的锁定时间:即预置寄存器。这个时间达到了模拟锁相环的极致,既尽可能接近数字锁相环DDS的锁定时间,又很好地回避了杂散问题。可以说把模拟锁相环的指标做到了极致。同时该系列合成器,特别对于人们普遍关系的@10K处的相噪做了深度优化,能保证在高频率输出的情况下达到很好的相位噪声。 三、硬件设计 一个好的合成器,除了本身优秀的芯片设计,严格的PCB Layout,也是不可缺少的。其中最关键的莫过于电源设计,合成器的关键部分PLL和VCO都是非常敏感的电路,极易收到外部的干扰。电源上的干扰主要是干扰路径,一个干净的供电,是合成相噪的保证。在这里推荐大家使用ADI目前业界最好的LDO:LT3042/3045, 它们具有极低的噪声和极高的PSRR。这些指标都完美契合了锁相环的相噪指标。 LT3045/3042的关键指标: · Ultralow RMS Noise: 0.8µVRMS (10Hz to 100kHz) n · Ultralow Spot Noise: 2nV/√Hz at 10kHz

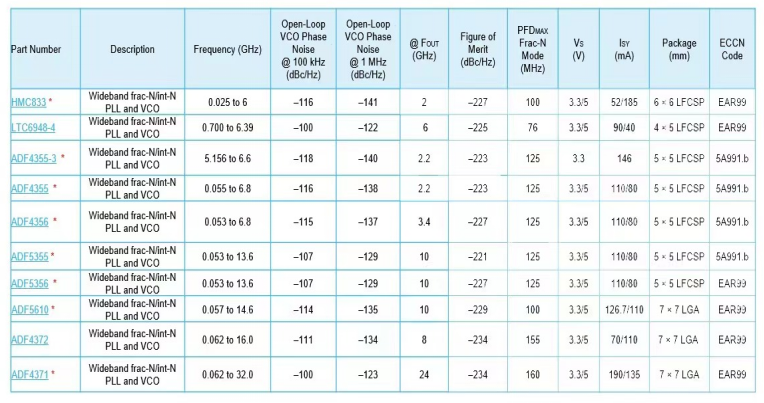

图7 LDO:LT3045 纹波抑制比 除此之外,合理的不限布局也是合成器设计成功的关键,芯片模拟和数字部分的隔离是必要的,包括模拟和数字的供电等,芯片尽可能远离辐射较大电路部分比如开关电源等,如果实在无法避免或者空间不够,可以采用加屏蔽罩等措施来进行空间隔离,同时合理的布局也是避免参考整数倍杂散的关键。 ADI 不仅提供了高性能的芯片,同样提供了完美的仿真工具(ADIsimPLL), 这个工具让我们的环路滤波器设计变得简单很多,同时还有时域和频域的量化仿真结果,而且可以灵活的调制,来满足不同客户的不同要求。 此外,LTC6948和LTC6946做了尽可能PIN TO PIN 的设计,让客户在同时使用这俩款芯片的时候,尽可能减少重复设计,减少了工作量,为客户节约了成本。与此同时ADI LTC6948和LTC6946在寄存器配置方面非常简单,容易操作,不同于其他厂商繁琐的寄存器配置。 由于LTC6948系列内部集成的是18-Bit Fractional Denominator,根据实测一般都会有几Hz的偏差。因此,对于客户需要频率精度非常准的场合,不建议选用此系列芯片。而ADI 的HMC83X系列合成器,集成了24/32-Bit Fractional Denominator, 就能够完美解决这个问题,并且能够提供很好的相位噪声。 ADI是唯一一家可以提供齐全的频率合成器选择的公司,频率从10K到32GHz,能够满足各种场合的不同需求,同时配合倍频器系列产品,能够将频率范围实现成倍的增加。ADF4371合成器是目前业界能够达到的最高频率的合成器,最高频率可达32G,带有RF输出静音的功能,能为ADF4372(最高到16G )及具有扫频功能的ADF5610提供高速采样时的时钟参考。

四、总结 一个好的合成器设计,不仅需要一个高性能的芯片,还要有合理规范的布线布局来支撑,并需要一个好的参考源(其中合理的压摆率选择也是考虑的关键)。合理的电源管理,合理的环路滤波器设计,正确合理的寄存器配置,才能设计出性能更好的频率源。 参考资料 《锁相环电路设计与应用》作者:(日)远坂俊昭 (责任编辑:admin) |